一种低时延的试验仪器测控系统结构及其方法

文献发布时间:2023-06-19 11:35:49

技术领域

本发明涉及测控系统技术领域,更具体地说,是一种低时延的试验仪器测控系统结构及其方法。

背景技术

目前市场上主流试验仪器测控系统多是以MCU处理器为核心,利用其强大的内部资源进行外设扩展。国际主流MCU处理器内部总线功能非常齐全,非常方便且灵活外挂各种芯片,用以快速解决外设问题,如SPI总线、I2C总线、并行数据总线、RS232接口总线、LAN总线等等,如图1所示结构。此种设计结构,所有的数据吞吐都需要MCU处理器独立完成,所有外设资源都需要MCU处理器分时处理。实际上处理器最强的功能是运算而非与外设器件进行数据交互,尤其是不同设计师所采用的外设时钟有较大差异,致使外设频率远远限制了处理器的性能发挥。

发明内容

本申请提出一种低时延的试验仪器测控系统结构,其目的在于解决现有MCU处理器由于外设固有采样周期限制而导致其无法发挥在试验仪器领域高性能的问题。

为达到上述技术目的,本申请采用下述技术方案:

一种低时延的试验仪器测控系统结构,其包括MCU处理器、与所述MCU处理器相接的若干外设器件,还包括若干功能模块,各所述功能模块中包括若干依据功能说明划分的所述外设器件;每一功能模块通过CPLD可编程门阵列芯片驱动控制;各所述CPLD可编程门阵列芯片以并行总线的方式与所述MCU处理器进行交互。

所述功能模块包括数字驱动模块、模拟驱动模块、协议驱动模块以及可扩展驱动的模块。

本申请更公开一种试验仪器测控系统的低延时方法,包括以下步骤:

第一步,根据试验所需要的功能选用合适的外设电子器件;

第二步,将外设器件组合成若干功能模块;

第三步,各所述功能模块分别用CPLD可编程门电路独立编程驱动控制;

第四步,再通过CPLD可编程门电路编程,将外设数通过并行总线方式与MCU处理器连接并进行交互通讯。所有数据总线中,并行总线执行速度最快。从而有达到设计目的。

由于采用上述技术方案,本申请的低时延的试验仪器测控系统结构可实现高性能处理器MCU与低性能、多样性的外设单元之间,通过每个模块独立的CPLD将中间环节的数据进行再编程方式吞吐整合,进而转换为标准的并行总线方式与处理器交互,从而实现系统低时延的功能。

附图说明

图1为现有的测控系统的结构;

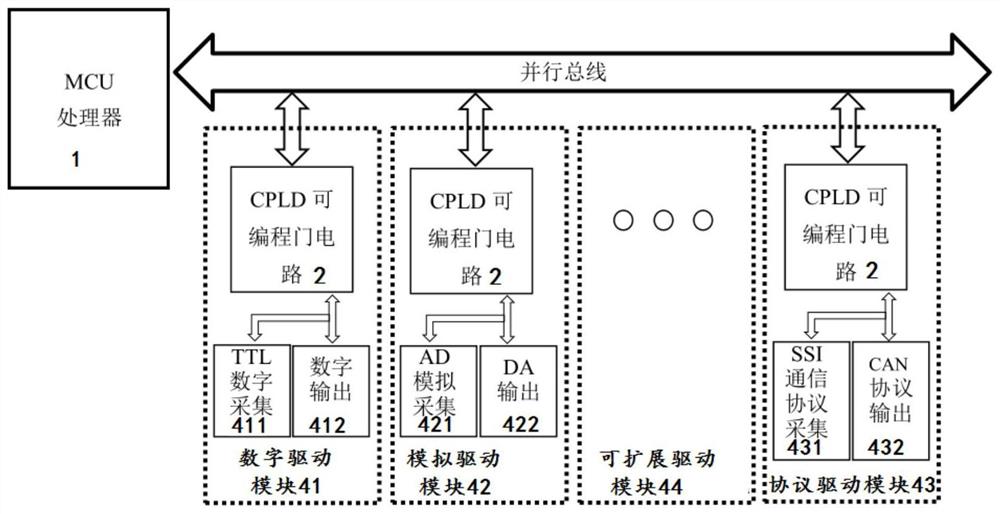

图2为本申请的低时延的试验仪器测控系统结构。

具体实施方式

下面通过实施例,并结合附图,对本发明的技术方案作进一步具体的说明。

参见图2所示,本申请的低时延的试验仪器测控系统结构包括MCU处理器1、与所述MCU 处理器1相接CPLD2交互以及外设器件。

为实现低时延的效果,本申请将各外设器件依据功能说明设计成若干各功能模块,每一功能模块通过一CPLD可编程门阵列芯片2驱动控制。各所述CPLD可编程门阵列芯片2再以并行总线的方式与所述MCU处理器1进行交互。

如图2所示,所述功能模块4包括数字驱动模块41、模拟驱动模块42、协议驱动模块43 以及不同种类可扩展驱动的模块44。数字驱动模块41可以包括TTL数字采集单元411、数字输出单元412等;模拟驱动模块42可以包括AD模拟采集单元421、DA输出单元422等;协议驱动模块43可以包括SSI通信协议采集模块431、CAN协议输出模块432等;所述可扩展驱动的模块44可以根据试验需求再进行外设器件的扩展。

所有模块中的CPLD可编程门阵列芯片2编程为并行总线方式与MCU处理器1进行交互。 CPLD可编程门阵列芯片2与MCU处理器1的交互速度非常快,通过CPLD可编程门阵列芯片2专项去处理不同功能单元,能够提高整体的交互速度,同时释放MCU处理器更多的空间,以便MCU处理器更精准的运用起来。并行总线的时间周期可以达到纳秒级别,所以即便再多的此类外设器件挂接,也不会影响处理器系统采集和控制周期。因而可实现高性能处理器与低性能、多样性的外设单元之间通讯交互,从而实现系统低时延,高性能、最优化结构。

本申请的试验仪器测控系统的低延时方法,包括以下步骤:

第一步,根据试验所需要的功能选用合适的外设器件;

第二步,将外设器件组合设计成为若干功能模块;

第三步,各所述功能模块分别用CPLD可编程门电路驱动控制;

第四步,再将各所述CPLD可编程门电路用并行总线与MCU处理器连接并进行交互通讯。

以上所述的实施方式仅用于说明本发明而不用于限制本发明的范围。本领域技术人员对本发明所做的均等变化与修饰,皆应属于本发明所附的权利要求书的涵盖范围。

- 一种低时延的试验仪器测控系统结构及其方法

- 一种中粗粒土室内直接剪切试验仪器及其使用方法