一种低硬件成本的5G移频多路恢复TDD同步信号的系统及方法

文献发布时间:2023-06-19 10:27:30

技术领域

本发明涉及5G通讯的技术领域,尤其涉及其一种低硬件成本的5G移频多路恢复TDD同步信号的系统及方法。

背景技术

5G有源天线通信系统中,设备需要与移动通信网络中的基站保持严格的时钟同步,避免产生时隙干扰影响基站运行,TDD同步信号对整个通信系统的运行至关重要。

现有的5G有源天线系统TDD同步信号的恢复一般包括:1、设备端接入5G同步MODEM,由MODEM产生同步信号;2、选用FPGA和AD转换芯片通过解调5G下行信号中的同步信号;3、采用卫星同步,接收定位卫星(如GPS、北斗等)的定位信号,获取时钟同步。但是现有的同步信号恢复方法中存在硬件成本高、软件实现复杂的问题,方案1需要外接同步MODEM硬件成本高,方案2需要增加高速AD芯片和FPGA芯片,再通过软件算法对5G下行信号进行解调分析恢复出同步信号,实现复杂度高,方案3需要增加昂贵的时钟芯片与卫星信号保持同步。当前的实现方案中都具有硬件成本偏高,软件实现复杂度高,还需要增加不同的处理芯片对信号进行分析处理。

发明内容

本发明提供了一种低硬件成本的5G移频多路恢复TDD同步信号的系统及方法,旨在解决现有的5G移频多路系统存在的问题。

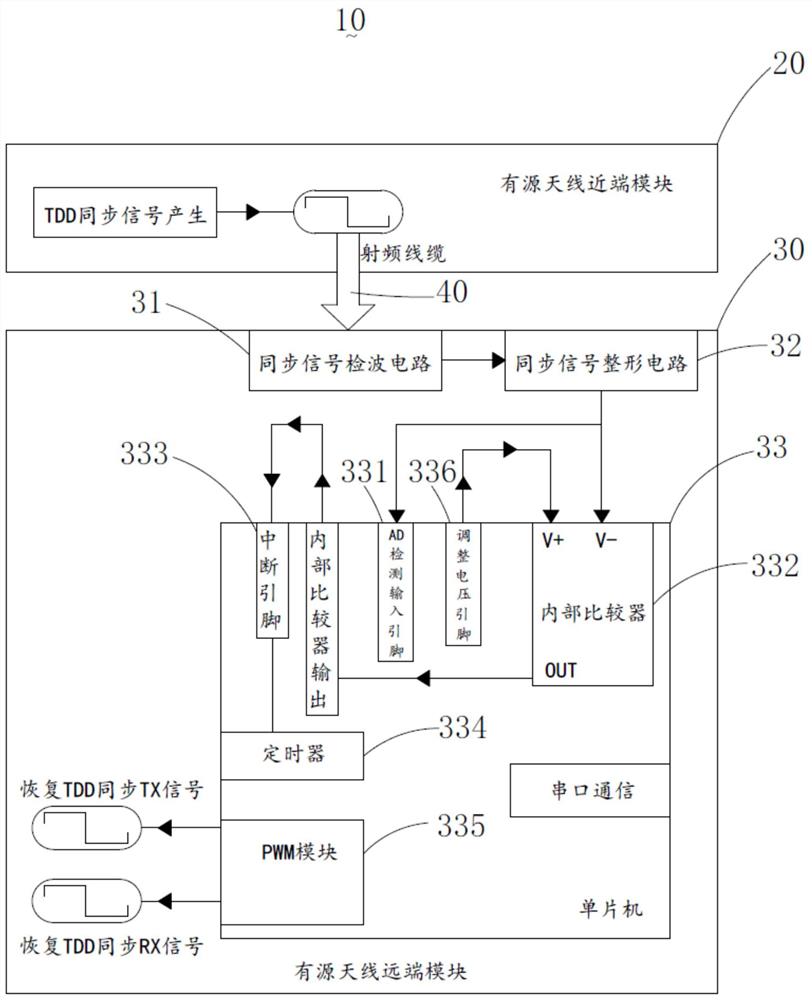

根据本申请实施例,提供了一种低硬件成本的5G移频多路恢复TDD同步信号的系统,包括有源天线近端模块、有源天线远端模块以及射频线缆,所述有源天线近端模块通过射频线缆与所述有源天线远端模块连接,所述有源天线远端模块包括同步信号检波电路、同步信号整形电路以及单片机,所述有源天线近端模块发送TDD同步信号并通过射频线缆传输到有源天线远端模块,所述有源天线远端模块通过同步信号检波电路恢复出单路同步信号,并经过所述同步信号整形电路传送至单片机中。

优选地,所述单片机包括调整电压引脚、分别与所述同步信号整形电路连接的AD检测输入引脚和内部比较器,所述内部比较器包括V+输入端、V-输入端以及输出端,所述调整电压引脚的输出端与所述内部比较器的V+输入端连接,所述内部比较器的V-输入端与所述同步信号整形电路连接,所述AD检测输入引脚用于检测输入同步开关信号的电压,对所述内部比较器的V+输入端电压进行动态调整。

优选地,所述单片机还包括中断引脚,所述中断引脚与所述内部比较器的输出端连接,所述AD检测输入引脚调整所述内部比较器后的同步信号传输至中断引脚,所述中断引脚进行中断处理。

优选地,所述单片机包括定时器,所述定时器与所述中断引脚连接,所述定时器用于计算中断引脚的同步信号高电平时间以及同步信号周期时间。

优选地,所述单片机还包括PWM模块,所述PWM模块用于对所述同步信号的保护间隔和相对原始同步信号的偏移量进行调整。

为了解决上述技术问题,本发明提供一种低硬件成本的5G移频多路恢复TDD同步信号的方法,包括以下步骤:

步骤S1:有源天线近端模块发送TDD同步信号至有源天线远端模块;

步骤S2:有源天线远端模块通过检波电路恢复出单路同步信号,经过同步信号整形电路传输至AD检测输入引脚和内部比较器引脚,对信号做进一步的硬件处理;

步骤S3:通过AD输入引脚检测外部输入开关信号的电压,对内部比较器的另一个输入端电压进行动态调整;

步骤S4:处理完后的同步信号输出到单片机中断引脚,单片机产生中断进行软件处理。

优选地,所述步骤S2包括:

步骤S21:AD检测输入引脚检测信号电压;

步骤S22:判断信号电压是否大于输入门限值;

若大于输入门限值,则进行步骤S3,若小于或等于输入门限值,则返回步骤S21。

优选地,所述步骤S3包括:步骤S31:根据输入信号电压调整内部比较器电压门限;所述步骤S4包括:

步骤S41:内部比较器输出信号至外部中断;

步骤S42:等待中断服务程序处理完成;

步骤S43:根据计算结果利用PWM模块产生同步信号;

步骤S44:根据串口输入指令,调整同步信号输出。

优选地,所述步骤S42的中断程序包括以下步骤:

步骤S421:进入外部中断服务子程序;

步骤S422:判断边沿中断类型;

若为上升沿中断,则进行步骤S423:打开定时器0和定时器1;

步骤S424:第二次进入中断,关闭定时器0,保存计数值;

步骤S425:计算同步信号周期时间;

步骤S426:处理结束,产生完成标志;

若为下降沿中断,则进行步骤S427:关闭定时器1,保存计数值;

步骤S428:计算同步信号高电平时间;

步骤S426:处理结束,产生完成标志。

本申请实施例提供的技术方案可以包括以下有益效果:本申请设计了一种低硬件成本的5G移频多路恢复TDD同步信号的系统及方法,使用低成本的单片机实现了同步信号的恢复,不需要加高速处理器、高速AD芯片等硬件成本高的芯片。该方案解决传统方案硬件成本高的问题,提高产品竞争力,低复杂度的硬件更便于设备的生产与后期维护;

通过单片机中的AD检测输入引脚检测输入同步信号的电平,控制内部比较器输入比较电压,可适应不同的外部输入信号,同时还可设置门限值,对低于门限值的干扰信号不进行处理。该技术使整个系统对于不同的输入信号进行动态调整,不需要修改硬件电路,降低硬件复杂度。

附图说明

为了更清楚地说明本发明实施例技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1是本发明一种低硬件成本的5G移频多路恢复TDD同步信号的系统的结构示意图;

图2是本发明一种低硬件成本的5G移频多路恢复TDD同步信号的方法的流程示意图;

图3是本发明一种低硬件成本的5G移频多路恢复TDD同步信号的方法S2的流程示意图;

图4是本发明一种低硬件成本的5G移频多路恢复TDD同步信号的方法S4的流程示意图;

图5是本发明一种低硬件成本的5G移频多路恢复TDD同步信号的方法S42的流程示意图。

标号说明:

10、一种低硬件成本的5G移频多路恢复TDD同步信号的系统;20、有源天线近端模块;30、有源天线远端模块;31、同步信号检波电路;32、同步信号整形电路;33、单片机;331、AD检测输入引脚;332、内部比较器;333、中断引脚;334、定时器;335、PWM模块;336、调整电压引脚;40、射频线缆;100、低硬件成本的5G移频多路恢复TDD同步信号的方法。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

还应当理解,在此本发明说明书中所使用的术语仅仅是出于描述特定实施例的目的而并不意在限制本发明。如在本发明说明书和所附权利要求书中所使用的那样,除非上下文清楚地指明其它情况,否则单数形式的“一”、“一个”及其“该”意在包括复数形式。

还应当进一步理解,在本发明说明书和所附权利要求书中使用的术语“和/或”是指相关联列出的项中的一个或多个的任何组合以及其所有可能组合,并且包括这些组合。

请参阅图1,本发明公开了一种低硬件成本的5G移频多路恢复TDD同步信号的系统10,包括有源天线近端模块20、有源天线远端模块30以及射频线缆40,所述有源天线近端模块20通过射频线缆40与所述有源天线远端模块30连接,所述有源天线远端模块30包括同步信号检波电路31、同步信号整形电路32以及单片机33,所述有源天线近端模块20发送TDD同步信号并通过射频线缆40传输到有源天线远端模块30,所述有源天线远端模块30通过同步信号检波电路31恢复出单路同步信号,并经过所述同步信号整形电路32传送至单片机33中。

本申请设计了一种低硬件成本的5G移频多路恢复TDD同步信号的系统10,使用低成本的单片机33实现了同步信号的恢复,不需要增加高速处理器、高速AD芯片等硬件成本高的芯片。该方案解决传统方案硬件成本高的问题,提高产品竞争力,低复杂度的硬件更便于设备的生产与后期维护。

所述单片机33包括调整电压引脚336、分别与所述同步信号整形电路32连接的AD检测输入引脚331和内部比较器332,所述内部比较器332包括V+输入端、V-输入端以及输出端,所述调整电压引脚336的输出端与所述内部比较器332的V+输入端连接,优选地,在本实施例中,所述AD检测输入引脚331与所述同步信号整形电路32连接,所述调整电压引脚336的输出端与所述内部比较器332的V+输入端相连,所述内部比较器332的V-输入端与所述同步信号整形电路32连接,所述AD检测输入引脚331用于检测输入同步开关信号的电压,对所述内部比较器332的V+输入端电压进行动态调整。

请继续参阅图1,所述单片机33还包括中断引脚333,所述中断引脚333与所述内部比较器332的输出端连接,所述AD检测输入引脚331调整所述内部比较器332后的同步信号传输至中断引脚333,所述中断引脚333进行中断处理。

在本实施例中,所述单片机33包括定时器334,所述定时器334与所述中断引脚333连接,所述定时器334用于计算中断引脚333的同步信号高电平时间以及同步信号周期时间。

在本实施例中,所述单片机33还包括PWM模块335,所述PWM模块335用于对所述同步信号的保护间隔和相对原始同步信号的偏移量进行调整。利用单片机33内部的PWM模块335产生两路恢复出来的TDD同步信号用于控制射频电路的开关,根据实际应用的需求可通过输入串口指令对两路同步信号的保护间隔和相对原始同步信号的偏移量进行调整,实现更好的同步效果。

通过单片机33中AD输入引脚331检测输入同步信号的电平,控制内部比较器332输入比较电压,可适应不同的外部输入信号,同时还可设置门限值,对低于门限值的干扰信号不进行处理。该技术使整个系统对于不同的输入信号进行动态调整,不需要修改硬件电路,降低硬件复杂度。

请参阅图2,本发明还提供一种低硬件成本的5G移频多路恢复TDD同步信号的方法100,包括以下步骤:

步骤S1:有源天线近端模块发送TDD同步信号至有源天线远端模块;

步骤S2:有源天线远端模块通过检波电路恢复出单路同步信号,经过同步信号整形电路传输至AD检测输入引脚和内部比较器引脚,对信号做进一步的硬件处理;

步骤S3:通过AD输入引脚检测外部输入开关信号的电压,对内部比较器的另一个输入端电压进行动态调整;

步骤S4:处理完后的同步信号输出到单片机中断引脚,单片机产生中断进行软件处理。

请参阅图3,所述步骤S2包括:

开始;

软件初始化;

步骤S21:AD检测输入引脚检测信号电压;

步骤S22:判断信号电压是否大于输入门限值;

若大于输入门限值,则进行步骤S31,若小于或等于输入门限值,则返回步骤S21;

优选地,所述步骤S3包括:步骤S31:根据输入信号电压调整内部比较器电压门限;

请参阅图4,所述步骤S4包括:

步骤S41:内部比较器输出信号至外部中断;

步骤S42:等待中断服务程序处理完成;

步骤S43:根据计算结果利用PWM模块产生同步信号;

步骤S44:根据串口输入指令,调整同步信号输出。

请参阅图5,优选地,所述步骤S42的中断程序包括以下步骤:

步骤S421:进入外部中断服务子程序;

步骤S422:判断边沿中断类型;

若为上升沿中断,则进行步骤S423:打开定时器0和定时器1;

步骤S424:第二次进入中断,关闭定时器0,保存计数值;

步骤S425:计算同步信号周期时间;

步骤S426:处理结束,产生完成标志;

若为下降沿中断,则进行步骤S427:关闭定时器1,保存计数值;

步骤S428:计算同步信号高电平时间;

步骤S426:处理结束,产生完成标志。

本发明提供的一种低硬件成本的5G移频多路恢复TDD同步信号的方法100与上述一种低硬件成本的5G移频多路恢复TDD同步信号的系统10产生的有益效果相同,在此不再赘述。

以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到各种等效的修改或替换,这些修改或替换都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以权利要求的保护范围为准。

- 一种低硬件成本的5G移频多路恢复TDD同步信号的系统及方法

- 一种5G NR无线分布式移频系统及移频方法