一种提高半导体器件台面耐压结构及制备方法

文献发布时间:2023-06-19 10:32:14

技术领域

本发明涉及电力电子技术领域,尤其涉及降低台面处电场峰值,提高半导体器件台面耐压的结构及制备方法。

背景技术

功率半导体器件中,不管是体内还是表面,都需要通过PN结来承受反向耐压。在大功率器件中,芯片内部耐压时可以看作一个平行平面结,随着耐压的增加,电场从PN结界面开始不断展宽来承受耐压,同时电场峰值也不断增大。但是器件的边缘因为更容易受到沾污、表面缺陷、工艺等的影响,在同样的电场峰值下,相比于体内更容易发生击穿。因此要更使表面处的电场峰值低于芯片内部的电场峰值,才能避免器件在边缘处被击穿。为此,大功率器件经常在边缘使用磨角工艺,即在器件边缘处形成一个倾斜的侧面,这部分区域称为台面区,如图1所示。

在给定耐压下,扩展宽度越大,则电场峰值越小。在器件边缘处引入倾斜面就是为了提升耗尽层在边缘表面处的扩展宽度,从而降低电场峰值。如图1,倾斜的台面,对应于更少的P区和更多的N区,耐压时为了维持整个耗尽区的电中性,P区的电场只能向外扩展更多,相应的N区的电场向内缩进。当倾斜的角度设置在一个特定的范围之内时,P区的电场扩展宽度超过了N区的电场缩进宽度,那么台面表面处的实际电场耗尽层宽度超过体内的电场耗尽层宽度。这钟情况下,台面表面处的电场峰值是低于体内的电场峰值,避免了器件在表面台面区域被击穿。

不同于体内电场最大值发生在PN结界面上,在这种台面结构中,电场最大值发生在P区靠近PN结处,因为这里引入了过多的电场集中。而这个最大电场的位置上因为比较靠近表面区域,更容易受到沾污、缺陷、工艺等等的影响而发生失效。常规器件中,芯件的裸片台面区域会沉积一层绝缘膜及一层保护性橡胶层,起到电场隔离和保护的作用。

发明内容

本发明要解决的技术问题通过器件结构改变及制备方法,在台面区域通过增加高绝缘介质层降低器件台面区域的电场峰值,提高器件的耐压和工作可靠性。

为解决上述技术问题,本发明提供的技术方案是一种提高半导体器件台面耐压结构,包括形成PN结的至少一个P区和一个N区;在P区和N区的侧面为台面区域,其特征在于在所述台面区域沉积有一层绝缘层,在所述绝缘层局部区域上沉积有一层高介电常数材料层,在所述高介电常数材料层和绝缘层上设置有保护层;所述高介电常数材料层覆盖台面处电场峰值区域。

高介电常数材料层在电场的作用下会产生感应电荷,这部分感应电荷的存在会吸引电荷线,从而削弱台面处峰值电场强度,使台面处的峰值电场降低。

高介电常数材料层所起的作用与绝缘层厚度有关,绝缘层越薄,则高介电材料层感应的电荷数越多,台面处峰值电场的降低越明显,器件耐压和可靠性更高。绝缘层厚度可介于0.00001-500um间。所述绝缘层材料为类金刚石材料。

高介电常数材料的介电常数要求比硅材料和绝缘层材料的介电常数高。高介电常数材料可以采用HfO2、TiO2或Ta2O5材料。

本发明的器件边缘台面锐角角度要求在10-70度间。

上述提高半导体器件台面耐压结构可以通过以下步骤进行制备:

1)在器件台面处沉积一层绝缘层;2)在器件上下两面及台面处设置挡板留有高介电常数材料层沉积窗口;3)沉积高介电常数材料层;4)去除挡板,在绝缘层和高介电常数材料层涂布保护层。

本发明的半导体器件不仅限于二极管,只要是通过PN结耐压的并包含台面磨角工艺的器件,都可通过在台面绝缘层上增加覆盖电场峰值区域的高介电材料层降低峰值电场强度,包括并不限于晶闸管,IGBT,MOS管等等。

本发明通过在台面处的绝缘层与保护层间增加高介电常数材料层形成耐压结构,其优势如下:

首先,可以有效改善台面区的电场分布,降低台面区的电场峰值;其次,引入高介电常数层,可以弥补台面磨角工艺误差引入的不利影响,保证器件的成品率,提升器件可靠性。

附图说明

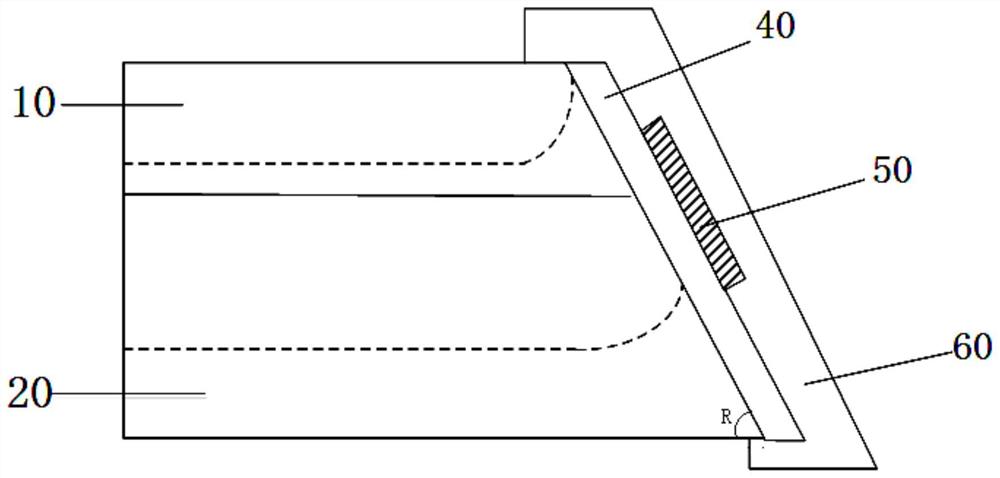

图1,本发明剖面结构示意图。

图2,完成内部制作工艺及台面磨角工艺的结构示意图。

图3,台面处沉积绝缘层结构示意图。

图4,制作沉积高介电常数材料层窗口结构示意图。

具体实施方式

针对上述技术方案,现举较佳实施例并结合图示进行具体说明。

本发明的半导体器件,包含有PN结。参看图1,器件内部结构至少包含一个P区10和一个与之相邻的N区20,P区和N区的接触面为PN结,PN结终止于器件边缘,器件边缘处是一个倾斜的侧面,倾斜的侧面即为台面30,边缘台面锐角角度R在10-70度间。

PN结两侧的虚线标记区域为耗尽区。倾斜的侧面使器件台面处的耗尽层比体内增加更多,但是在靠近台面表面处还是会存在一个峰值电场。

首先完成器件芯片的内部制作工艺形成PN结,然后在对其进行台面磨角工艺,制作出边缘为斜面的台面30,参看图2。由于本发明的半导体器件不仅限于二极管,只要是通过PN结耐压的并包含台面磨角工艺的器件,都可通过在台面绝缘层上增加覆盖电场峰值区域的高介电材料层降低峰值电场强度,包括并不限于晶闸管,IGBT,MOS管等。因此,器件芯片的内部制作工艺及台面磨角工艺采用各器件常规制备工艺制备即可。

在台面区域沉积一层绝缘层40,参看图1和图3,绝缘层材料为类金刚石材料,其厚度在0.00001-500um的范围之间。在绝缘层局部区域上还沉积有一层高介电常数材料层50,高介电常数材料指的是介电常数高于硅材料和绝缘层材料介电常数。一般高介电常数材料可以是HfO2、TiO2或Ta2O5。高介电常数材料层沉积区域满足覆盖台面处峰值电场所在区域。高介电常数材料层在峰值电场的作用下会产生感应电荷,这部分感应电荷的存在会吸引电荷线,从而削弱台面处峰值电场强度,使台面处的峰值电场降低。高介电常数材料层所起的作用与绝缘层厚度有关,绝缘层越薄,则高介电材料层感应的电荷数越多,台面处电场峰值降低越明显,器件耐压和可靠性更高。

在绝缘层40和高介电常数材料层50上涂布有一层保护层60,保护层包覆台面区域边缘角度。保护层材料为橡胶材质,起到电场隔离和保护的作用。

高介电常数材料层的沉积采用在P区和N区与台面相邻的两面设置挡板70,台面边缘处设置挡板70,参看图4,通过三面的挡板遮挡保护,并在台面区域留出高介电常数材料沉积的窗口,通过该窗口进行高介电常数材料沉积形成高介电常数材料层50。然后撤去挡板,在绝缘层和高介电常数材料层的表面制作保护层60,保护层需包覆台面边缘处两边角,并延伸至P区和N区与台面区域相邻的部分表面,形成图1中的器件芯片内部的台面耐压结构。

本发明通过在台面处的绝缘层与保护层间增加高介电常数材料层形成耐压结构,其优势如下:

首先,可以有效改善台面区的电场分布,降低台面区的电场峰值;其次,引入高介电常数层,可以弥补台面磨角工艺误差引入的不利影响,保证器件的成品率,提升器件可靠性。

- 一种提高半导体器件台面耐压结构及制备方法

- 一种提高器件纵向耐压能力的半导体装置封装结构