驱动电路

文献发布时间:2023-06-19 13:45:04

技术领域

本发明是关于一种驱动电路,特别是关于一种设置栅极节点驱动电路与控制节点驱动电路,使得节点充电过程不会受到多工器电路顺序的影响的驱动电路。

背景技术

在利用多工器来减少周边电路空间的方式已成为各种显示装置常见的设计趋势,其通过控制信号时序上的差异,使得数据电压能在不同时间点输入至像素当中。现有的多工器电路在不同顺序的多工器电路当中,因为栅极节点是通过多工器信号开启后由多工器电路的连接方式来回复节点的电压,在多工器电路开启的顺序上,最后开启的已无足够时间将电压回拉到预设标准,其造成未足补偿的电压差会使得像素产生亮度不均或色偏的问题。

另一方面,在重设的操作状态下,电路将控制节点重设置数据电压的最高值,将栅极节点重设至参考电压,使得后续的补偿与数据写入功能能正常执行,但这样的操作造成高电压源往参考电压源的漏电路径,使得画面的亮度被扯动而产生闪烁的问题。

综观前所述,现有的驱动电路在电路的设计上仍然具有相当的缺陷,因此,本发明通过设计一种驱动电路,针对现有技术的缺失加以改善,以解决现有技术的问题,进而增进产业上的实施利用。

发明内容

有鉴于上述现有技术的问题,本发明的目的在于提供一种驱动电路,解决栅极节点回拉时间不够及漏电路径的问题。

根据上述目的,本发明的实施例提出一种驱动电路,其包含像素驱动电路、栅极节点驱动电路、驱动电容、控制节点驱动电路以及多工器电路。其中,像素驱动电路包含驱动晶体管,驱动晶体管的第一端耦接于高电压源,驱动晶体管的第二端耦接于发光元件,驱动晶体管的控制端耦接于栅极节点。栅极节点驱动电路耦接于栅极节点,下拉栅极节点的电压。驱动电容的一端耦接于栅极节点,另一端耦接于控制节点。控制节点驱动电路耦接于控制节点,上拉控制节点的电压。多工器电路包含数据晶体管及数据线电容,数据晶体管的第一端耦接于控制节点,数据晶体管的第二端耦接于数据线电容。

在本发明的实施例中,像素驱动电路可包含发光晶体管,发光晶体管的第一端耦接于驱动晶体管的第二端,发光晶体管的第二端耦接于发光元件,发光晶体管的控制端接收发光信号以控制发光元件发光。栅极节点驱动电路可包含第一晶体管,第一晶体管的第一端耦接于第一参考电压,第一晶体管的第二端耦接于栅极节点。控制节点驱动电路可包含第二晶体管,第二晶体管的第一端耦接于第二参考电压,第二晶体管的第二端耦接于控制节点。

在本发明的实施例中,第一晶体管的控制端接收当级第一信号以下拉栅极节点的电压,第二晶体管的控制端接收外接信号以上拉控制节点电压,外接信号包含当级第一信号及后极发光信号。

在本发明的实施例中,第一晶体管的控制端接收前级第一信号以下拉栅极节点的电压,第二晶体管的控制端接收外接信号以上拉控制节点电压,外接信号包含前级第一信号、当级第一信号及发光信号。

在本发明的实施例中,控制节点驱动电路可进一步包含第三晶体管,第三晶体管的第一端耦接于第二参考电压及第二晶体管的第一端,第三晶体管的第二端耦接于控制节点及第二晶体管的第二端。

在本发明的实施例中,第一晶体管的控制端接收当级第一信号以下拉栅极节点的电压,第二晶体管的控制端接收当级第一信号及第三晶体管的控制端接收发光信号以上拉控制节点电压。

在本发明的实施例中,控制节点驱动电路可进一步包含第三晶体管,第三晶体管的第一端耦接于第二参考电压及第二晶体管的第一端,第三晶体管的第二端耦接于控制节点及第二晶体管的第二端,栅极节点驱动电路可进一步包含第四晶体管,第四晶体管的第一端耦接于第一参考电压,第四晶体管的第二端耦接于第一晶体管的第一端。

在本发明的实施例中,第一晶体管的控制端接收当级第一信号及第四晶体管的控制端接收前级第一信号以下拉栅极节点的电压,第二晶体管的控制端接收当级第一信号及第三晶体管的控制端接收发光信号以上拉控制节点电压。

在本发明的实施例中,数据晶体管的控制端接收第二信号以控制数据晶体管,数据晶体管关闭时,多工器电路将数据电压储存于数据线电容,数据晶体管开启时,多工器电路将数据电压耦合至控制节点。

承上所述,本发明的驱动电路,可通过栅极节点驱动电路与控制节点驱动电路的设置,使得预充的操作由上述驱动电路执行而非原本的多工器电路。预充操作与多工器数据写入的操作为分开独立的操作路径,可同时进行以避免预充操作的时间不足而影响节点电压的问题。此外,电路重设的状态不需要在第一信号与第二信号同时开启晶体管的情况下进行,避免产生高电压源至参考电压源的漏电路径,防止显示装置的画面产生闪烁的问题。

附图说明

为使本发明的技术特征、内容与优点及其所能达成的功效更为显而易见,兹将本发明配合附图,并以实施例的表达形式详细说明如下:

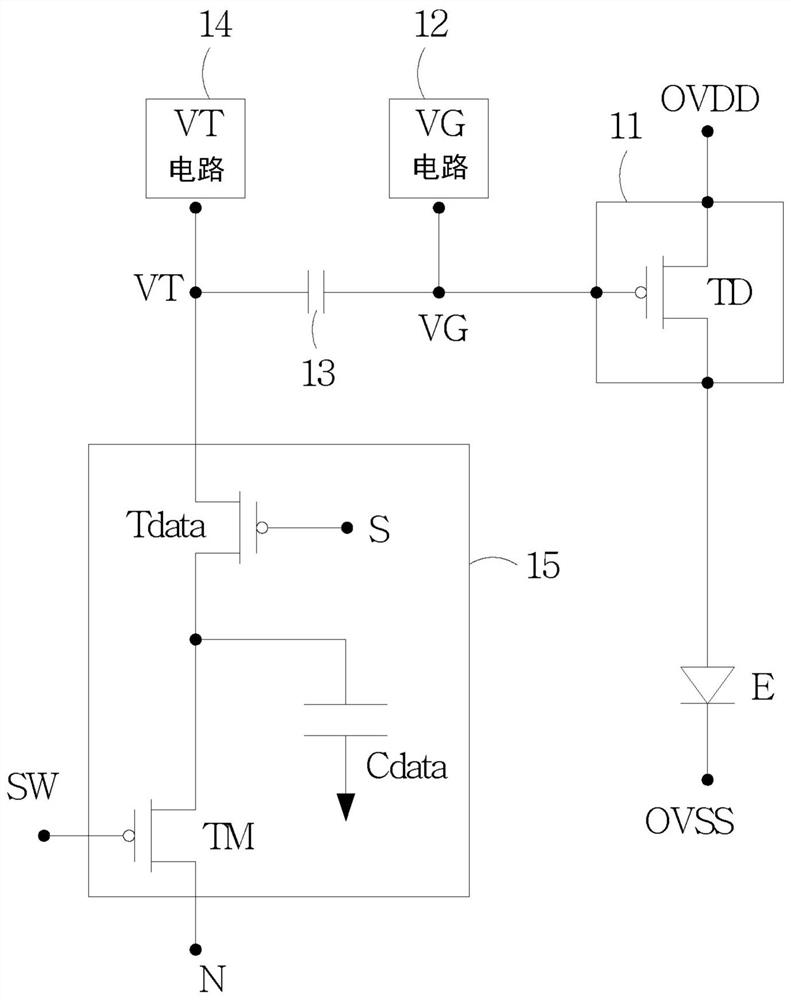

图1为本发明实施例的驱动电路的示意图。

图2A为本发明第一实施例的驱动电路的电路示意图。

图2B为本发明第一实施例的驱动电路的波形示意图。

图3A为本发明第二实施例的驱动电路的电路示意图。

图3B为本发明第二实施例的驱动电路的波形示意图。

图4A为本发明第三实施例的驱动电路的电路示意图。

图4B为本发明第三实施例的驱动电路的波形示意图。

图5A为本发明第四实施例的驱动电路的电路示意图。

图5B为本发明第四实施例的驱动电路的波形示意图。

其中,附图标记说明如下:

10,20,30,40,50:驱动电路

11,21,31,41,51:像素驱动电路

12,22,32,42,52:栅极节点驱动电路

13,23,33,43,53:驱动电容

14,24,34,44,54:控制节点驱动电路

15,25,35,45,55:多工器电路

Cdata:数据线电容

E:发光元件

EM:发光信号

EM2,n:外接信号

MUX,n:多工器信号

N:节点

OVDD:高电压源

OVSS:低电压源

S:信号线

SW:控制线

S1,n:当级第一信号

S1,n+1:后级第一信号

S1,n-1:前级第一信号

S2,n:当级第二信号

TD:驱动晶体管

TE:发光晶体管

TM:多工器晶体管

Tdata:数据晶体管

T1,T2:晶体管

T21,T31,T41,T51:第一晶体管

T22,T32,T42,T52:第二晶体管

VG:栅极节点

VT:控制节点

Vref N:第一参考电压

Vref P:第二参考电压

具体实施方式

为利了解本发明的技术特征、内容与优点及其所能达成的功效,兹将本发明配合附图,并以实施例的表达形式详细说明如下,而其中所使用的图式,其主旨仅为示意及辅助说明书之用,未必为本发明实施后的真实比例与精准配置,故不应就所附的图式的比例与配置关系解读、局限本发明于实际实施上的权利范围,合先叙明。

在附图中,为了淸楚起见,放大了基板、面板、区域、线路等的厚度或宽度。在整个说明书中,相同的附图标记表示相同的元件。应当理解,当诸如基板、面板、区域或线路的元件被称为在另一元件「上」或「连接到」另一元件时,其可以直接在另一元件上或与另一元件连接,或者中间元件可以也存在。相反地,当元件被称为「直接在另一元件上」或「直接连接到」另一元件时,不存在中间元件。如本文所使用的「连接」,其可以指物理及/或电性的连接。再者,「电性连接」、「耦合」或「耦接」是可为二元件间存在其它元件。此外,应当理解,尽管术语「第一」、「第二」、「第三」在本文中可以用于描述各种元件、部件、区域、层及/或部分,其是用于将一个元件、部件、区域、层及/或部分与另一个元件、部件、区域、层及/或部分区分开。因此,仅用于描述目的,而不能将其理解为指示或暗示相对重要性或者其顺序关系。

除非另有定义,本文所使用的所有术语具有与本发明所属技术领域的通常知识者通常理解的含义。将进一步理解的是,诸如在通常使用的字典中定义的那些术语应当被解释为具有与它们在相关技术和本发明的上下文中的含义一致的含义,并且将不被解释为理想化的或过度正式的意义,除非本文中明确地如此定义。

请参阅图1,其为本发明实施例的驱动电路的示意图。如图所示,驱动电路10包含像素驱动电路11、栅极节点驱动电路12、驱动电容13、控制节点驱动电路14以及多工器电路15。像素驱动电路11包含驱动晶体管TD,驱动晶体管TD的第一端耦接于高电压源OVDD,驱动晶体管TD的第二端耦接于发光元件E,发光元件E耦接于低电压源OVSS,驱动晶体管TD的控制端耦接于栅极节点VG。栅极节点VG耦接于驱动电容13的一端,驱动电容13的另一端耦接于控制节点VT,驱动电容13通过栅极节点VG与控制节点VT之间的压差来提供控制驱动晶体管TD的驱动电压。栅极节点驱动电路12耦接于栅极节点VG,通过栅极节点驱动电路12下拉栅极节点VG的电压。控制节点驱动电路14耦接于控制节点VT,通过控制节点驱动电路14上拉控制节点VT的电压。

多工器电路15包含数据晶体管Tdata及数据线电容Cdata,数据晶体管Tdata的第一端耦接于控制节点VT,数据晶体管Tdata的第二端耦接于数据线电容Cdata,数据晶体管Tdata的控制端耦接于信号线S。数据线电容Cdata可以储存数据线所需要的电压,由信号线S控制数据晶体管Tdata开启来将储存的数据电压写入控制节点VT,由于每个像素行包含多个子像素,因此储存数据电压的数据线电容Cdata容量大于驱动电容13。数据晶体管Tdata的第二端还耦接于多工器晶体管TM的第一端,多工器晶体管TM的第一端耦接于节点N,多工器晶体管TM的控制端耦接于控制线SW。在显示器的显示像素当中,连接各个子像素的数据线所需的数据信号可通过多工器电路15提供,不同像素行可由同一个节点N提供数据信号,由控制线SW控制多工器晶体管TM开启来提供各个像素行所需的数据信号。多工器电路15的设置可以减少数据线传输节点的设置,减少驱动电路元件及所需的电路设置空间。

在以往的驱动结构设计上,不同像素行的多工器电路15是通过控制线SW的控制,使得多工器晶体管TM依序开启来提供数据信号,但在数据电压写入时间不同的情况下,对应于最末多工器电路当中的栅极节点VG在重设操作的过程中并无足够时间回拉至预设最高电压,导致未足补偿电压的产生,当数据电压写入时耦合电压增加,这样的状况使得控制驱动晶体管开启时,通过的电流增加而使发光元件E亮度增加,造成显示面板在显示时产生亮度不均或色偏的问题。此外,将栅极节点VG重设置预设最高电压的重设操作,在高电压源OVDD朝向设定的电压源方向产生漏电路径,同样造成显示画面的亮度改变,影响显示品质。在本公开的实施例中,通过栅极节点驱动电路12及控制节点驱动电路14的设置,让多工器电路15的写入不是直接透过数据线进到像素当中,而是先写入到数据线中,即数据线电容Cdata当中,再于同一个时间点进到驱动电容13,使得每个多工器电路15对应的补偿时间相同,避免不同多工器电路15在时间顺序上的差异造成电压差异,详细的电路设置结构于以下实施例中进一步说明。

请参阅图2A,其为本发明第一实施例的驱动电路的电路示意图。请同时参阅图2B,其为本发明第一实施例的驱动电路的波形示意图。在图2A中,驱动电路20包含像素驱动电路21、栅极节点驱动电路22、驱动电容23、控制节点驱动电路24以及多工器电路25。像素驱动电路21包含驱动晶体管TD及发光晶体管TE,驱动晶体管TD的第一端耦接于高电压源OVDD,驱动晶体管TD的第二端耦接于发光晶体管TE的第一端,驱动晶体管TD的控制端耦接于栅极节点VG。发光晶体管TE的第二端耦接于发光元件E,发光晶体管TE的控制端耦接于发光信号EM的信号源,发光信号EM开启发光晶体管TE而使得电流流至发光元件E,控制发光元件E发光。发光元件E的一端耦接于晶体管T1的第一端,晶体管T1的第二端与晶体管T1的控制端以二极体连接的方式耦接于后级第一信号S1,n+1的信号源,发光元件E的另一端耦接于低电压源OVSS。

栅极节点VG耦接于驱动电容23的一端,驱动电容23的另一端耦接于控制节点VT,栅极节点驱动电路22耦接于栅极节点VG,栅极节点驱动电路22包含第一晶体管T21,第一晶体管T21的第一端耦接于第一参考电压Vref N,第一晶体管T21的第二端耦接于栅极节点VG,第一晶体管T21的控制端接收当级第一信号S1,n以下拉栅极节点VG的电压。控制节点驱动电路24耦接于控制节点VT,控制节点驱动电路24包含第二晶体管T22,第二晶体管T22的第一端耦接于第二参考电压Vref P,第二晶体管T22的第二端耦接于控制节点VT,第二晶体管的T22控制端接收外接信号EM2,n以上拉控制节点VT的电压,外接信号EM2,n为结合当级第一信号S1,n及发光信号EM的波形而形成的信号。

多工器电路25包含数据晶体管Tdata、数据线电容Cdata及多工器晶体管TM,数据晶体管Tdata的第一端耦接于控制节点VT,数据晶体管Tdata的第二端耦接于数据线电容Cdata,数据晶体管Tdata的控制端耦接于当级第二信号线S2,n,当级第二信号线S2,n同时连接至晶体管T2的控制端,晶体管T2的第一端耦接于栅极节点VG,晶体管T2的第二端耦接于像素驱动电路21。

请参阅图2B,在第一条数据线的时序中,当级第一信号S1,n开启第一晶体管T21,通过第一参考电压Vref N下拉栅极节点VG的电压,同时外接信号EM2,n开启第二晶体管T22,通过第二参考电压Vref P上拉控制节点VT的电压。在多工器电路25部分,多工器信号MUX,n开启多工器晶体管TM,将数据线的电压写入至数据线电容Cdata当中,由于此时当级第二信号S2,n并未开启数据晶体管Tdata,数据线电压并未写入至驱动电容23,也因为数据晶体管Tdata是关闭状态,因此多工器电路25数据的写入程序与栅极节点驱动电路22及控制节点驱动电路24的预充程序可独立且同时进行,无须等到多工器信号MUX,n开启后才由多工器电路25来进行预充程序。让写入程序与预充程序以分开的程序同时执行,可以避免不同顺序的多工器造成补偿的时间不足而产生电压差,导致传送至像素的电压增加而影响显示亮度。

接续前述时序,当级第一信号S1,n转为高电位关闭第一晶体管T21,外接信号EM2,n也转为高电位关闭第二晶体管T22,当级第二信号S2,n开启数据晶体管Tdata,将数据电压耦合至该控制节点VT,即将数据线的电压信号由数据线电容Cdata写入到像素的驱动电容23。当级第一信号S1,n与当级第二信号S2,n的时序并未重迭,因此不会同时开启第一晶体管T21及晶体管T2,避免由高电压源OVDD朝向第一参考电压Vref N产生漏电路径,造成整面的显示亮度被扯动而有闪烁的问题。

另外,当进行到第二条数据线的时序中,控制节点驱动电路24的第二晶体管T22需要由外接信号EM2,n开启第二晶体管T22,将栅极节点VG与控制节点VT拉回至第二参考电压Vref P,因此,外接信号EM2,n必须包含后一级的发光信号EM。

请参阅图3A,其为本发明第二实施例的驱动电路的电路示意图。请同时参阅图3B,其为本发明第二实施例的驱动电路的波形示意图。在图3A中,驱动电路30包含像素驱动电路31、栅极节点驱动电路32、驱动电容33、控制节点驱动电路34以及多工器电路35。像素驱动电路31包含驱动晶体管TD及发光晶体管TE,驱动晶体管TD的第一端耦接于高电压源OVDD,驱动晶体管TD的第二端耦接于发光晶体管TE的第一端,驱动晶体管TD的控制端耦接于栅极节点VG。发光晶体管TE的第二端耦接于发光元件E,发光晶体管TE的控制端耦接于发光信号EM的信号源,发光信号EM开启发光晶体管TE而使得电流流至发光元件E,控制发光元件E发光。发光元件E的一端耦接于晶体管T1的第一端,晶体管T1的第二端与晶体管T1的控制端以二极体连接的方式耦接于当级第一信号S1,n的信号源,发光元件E的另一端耦接于低电压源OVSS。

栅极节点VG耦接于驱动电容33的一端,驱动电容33的另一端耦接于控制节点VT,栅极节点驱动电路32耦接于栅极节点VG,栅极节点驱动电路32包含第一晶体管T31,第一晶体管T31的第一端耦接于第一参考电压Vref N,第一晶体管T31的第二端耦接于栅极节点VG,第一晶体管T21的控制端接收前级第一信号S1,n-1以下拉栅极节点VG的电压。控制节点驱动电路34耦接于控制节点VT,控制节点驱动电路34包含第二晶体管T32,第二晶体管T32的第一端耦接于第二参考电压Vref P,第二晶体管T32的第二端耦接于控制节点VT,第二晶体管的T32控制端接收外接信号EM2,n以上拉控制节点VT的电压,外接信号EM2,n为结合前级第一信号S1,n-1、当级第一信号S1,n及发光信号EM的波形而形成的信号。

多工器电路35包含数据晶体管Tdata、数据线电容Cdata及多工器晶体管TM,数据晶体管Tdata的第一端耦接于控制节点VT,数据晶体管Tdata的第二端耦接于数据线电容Cdata,数据晶体管Tdata的控制端耦接于当级第二信号线S2,n,当级第二信号线S2,n同时连接至晶体管T2的控制端,晶体管T2的第一端耦接于栅极节点VG,晶体管T2的第二端耦接于像素驱动电路31。

请参阅图3B,在第一条数据线的时序中,前级第一信号S1,n-1开启第一晶体管T31,通过第一参考电压Vref N下拉栅极节点VG的电压,同时外接信号EM2,n开启第二晶体管T32,通过第二参考电压Vref P上拉控制节点VT的电压。在多工器电路35部分,多工器信号MUX,n开启多工器晶体管TM,将数据线的电压写入至数据线电容Cdata当中,由于此时当级第二信号S2,n并未开启数据晶体管Tdata,数据线电压并未写入至驱动电容33,也因为数据晶体管Tdata是关闭状态,因此多工器电路35数据的写入程序与栅极节点驱动电路32及控制节点驱动电路34的预充程序可独立且同时进行,无须等到多工器信号MUX,n开启后才由多工器电路35来进行预充程序。让写入程序与预充程序以分开的程序同时执行,可以避免不同顺序的多工器造成补偿的时间不足而产生电压差,导致传送至像素的电压增加而影响显示亮度。

接续前述时序,前级第一信号S1,n-1关闭第一晶体管T31,外接信号EM2,n也转为高电位关闭第二晶体管T32,当多工器信号MUX,n依序将数据电压写入完成后,当级第二信号S2,n开启数据晶体管Tdata,将数据电压耦合至该控制节点VT,即将数据线的电压信号由数据线电容Cdata写入到像素的驱动电容33。在本实施例中,第一晶体管T21及晶体管T2同样不会同时开启,避免由高电压源OVDD朝向第一参考电压Vref N产生漏电路径,造成整面的显示亮度被扯动而有闪烁的问题。

请参阅图4A,其为本发明第三实施例的驱动电路的电路示意图。请同时参阅图4B,其为本发明第三实施例的驱动电路的波形示意图。在图4A中,驱动电路40包含像素驱动电路41、栅极节点驱动电路42、驱动电容43、控制节点驱动电路44以及多工器电路45。像素驱动电路41包含驱动晶体管TD及发光晶体管TE,驱动晶体管TD的第一端耦接于高电压源OVDD,驱动晶体管TD的第二端耦接于发光晶体管TE的第一端,驱动晶体管TD的控制端耦接于栅极节点VG。发光晶体管TE的第二端耦接于发光元件E,发光晶体管TE的控制端耦接于发光信号EM的信号源,发光信号EM开启发光晶体管TE而使得电流流至发光元件E,控制发光元件E发光。发光元件E的一端耦接于晶体管T1的第一端,晶体管T1的第二端与晶体管T1的控制端以二极体连接的方式耦接于后级第一信号S1,n+1的信号源,发光元件E的另一端耦接于低电压源OVSS。

栅极节点VG耦接于驱动电容43的一端,驱动电容43的另一端耦接于控制节点VT,栅极节点驱动电路42耦接于栅极节点VG,栅极节点驱动电路42包含第一晶体管T41,第一晶体管T41的第一端耦接于第一参考电压Vref N,第一晶体管T41的第二端耦接于栅极节点VG,第一晶体管T41的控制端接收当级第一信号S1,n以下拉栅极节点VG的电压。控制节点驱动电路44耦接于控制节点VT,控制节点驱动电路44包含第二晶体管T42及第三晶体管T43,第二晶体管T42的第一端耦接于第二参考电压Vref P,第二晶体管T42的第二端耦接于控制节点VT,第三晶体管T43的第一端耦接于第二参考电压Vref P,第三晶体管T43的第二端耦接于控制节点VT。第二晶体管的T42控制端接收当级第一信号S1,n以上拉控制节点VT的电压,第三晶体管的T43控制端接收发光信号EM以下拉控制节点VT及闸级节点VG的电压。

多工器电路45包含数据晶体管Tdata、数据线电容Cdata及多工器晶体管TM,数据晶体管Tdata的第一端耦接于控制节点VT,数据晶体管Tdata的第二端耦接于数据线电容Cdata,数据晶体管Tdata的控制端耦接于当级第二信号线S2,n,当级第二信号线S2,n同时连接至晶体管T2的控制端,晶体管T2的第一端耦接于栅极节点VG,晶体管T2的第二端耦接于像素驱动电路41。

请参阅图4B,在第一条数据线的时序中,当级第一信号S1,n同时开启第一晶体管T31及第二晶体管T32,通过第一参考电压Vref N下拉栅极节点VG的电压,也通过第二参考电压Vref P上拉控制节点VT的电压。在多工器电路35部分,多工器信号MUX,n开启多工器晶体管TM,将数据线的电压写入至数据线电容Cdata当中,由于此时当级第二信号S2,n并未开启数据晶体管Tdata,数据线电压并未写入至驱动电容43,也因为数据晶体管Tdata是关闭状态,因此多工器电路45数据的写入程序与栅极节点驱动电路42及控制节点驱动电路44的预充程序可独立且同时进行,无须等到多工器信号MUX,n开启后才由多工器电路45来进行预充程序。让写入程序与预充程序以分开的程序同时执行,可以避免不同顺序的多工器造成补偿的时间不足而产生电压差,导致传送至像素的电压增加而影响显示亮度。

接续前述时序,当级第一信号S1,n转为高电位关闭第一晶体管T31及第二晶体管T32,当多工器信号MUX,n依序将数据电压写入完成后,当级第二信号S2,n开启数据晶体管Tdata,将数据电压耦合至该控制节点VT,即将数据线的电压信号由数据线电容Cdata写入到像素的驱动电容43。在本实施例中,第一晶体管T21及晶体管T2同样不会同时开启,避免由高电压源OVDD朝向第一参考电压Vref N产生漏电路径,造成整面的显示亮度被扯动而有闪烁的问题。

当进行到第二条数据线的时序中,控制节点驱动电路44的第二晶体管T43需要由发光信号EM开启第三晶体管T43,将栅极节点VG与控制节点VT拉回至第二参考电压Vref P,因此,发光信号EM必须设置于后一数据线的时序中。

请参阅图5A,其为本发明第四实施例的驱动电路的电路示意图。请同时参阅图5B,其为本发明第四实施例的驱动电路的波形示意图。在图4A中,驱动电路50包含像素驱动电路51、栅极节点驱动电路52、驱动电容53、控制节点驱动电路54以及多工器电路55。像素驱动电路51包含驱动晶体管TD及发光晶体管TE,驱动晶体管TD的第一端耦接于高电压源OVDD,驱动晶体管TD的第二端耦接于发光晶体管TE的第一端,驱动晶体管TD的控制端耦接于栅极节点VG。发光晶体管TE的第二端耦接于发光元件E,发光晶体管TE的控制端耦接于发光信号EM的信号源,发光信号EM开启发光晶体管TE而使得电流流至发光元件E,控制发光元件E发光。发光元件E的一端耦接于晶体管T1的第一端,晶体管T1的第二端与晶体管T1的控制端以二极体连接的方式耦接于当级第一信号S1,n的信号源,发光元件E的另一端耦接于低电压源OVSS。

栅极节点VG耦接于驱动电容53的一端,驱动电容53的另一端耦接于控制节点VT,栅极节点驱动电路52耦接于栅极节点VG,栅极节点驱动电路52包含第一晶体管T51及第四晶体管T54,控制节点驱动电路54包含第二晶体管T52及第三晶体管T53,第四晶体管T54的第一端耦接于的第一参考电压Vref N,第四晶体管T54的第二端耦接于第一晶体管T51的第一端,第一晶体管T51的第二端耦接于栅极节点VG,第一晶体管T51的控制端接收当级第一信号S1,n,第四晶体管T54的控制端接收前级第一信号S1,n-1,藉由同时开启第一晶体管T51及第四晶体管T54以下拉栅极节点VG的电压。控制节点驱动电路54耦接于控制节点VT,第二晶体管T52的第一端耦接于第二参考电压Vref P,第二晶体管T52的第二端耦接于控制节点VT,第三晶体管T53的第一端耦接于第二参考电压Vref P,第三晶体管T53的第二端耦接于控制节点VT。第二晶体管的T52控制端接收当级第一信号S1,n以上拉控制节点VT的电压,第三晶体管的T53控制端接收发光信号EM以下拉控制节点VT及闸级节点VG的电压。

请参阅图5B,在第一条数据线的时序中,前级第一信号S1,n-1与当级第一信号S1,n同时开启第一晶体管T51及第四晶体管T54,通过第一参考电压Vref N下拉栅极节点VG的电压,当级第一信号S1,n开启第二晶体管T52,通过第二参考电压Vref P上拉控制节点VT的电压。在多工器电路55部分,多工器信号MUX,n开启多工器晶体管TM,将数据线的电压写入至数据线电容Cdata当中,由于此时当级第二信号S2,n并未开启数据晶体管Tdata,数据线电压并未写入至驱动电容53,也因为数据晶体管Tdata是关闭状态,因此多工器电路55数据的写入程序与栅极节点驱动电路52及控制节点驱动电路54的预充程序可独立且同时进行,无须等到多工器信号MUX,n开启后才由多工器电路45来进行预充程序。让写入程序与预充程序以分开的程序同时执行,可以避免不同顺序的多工器造成补偿的时间不足而产生电压差,导致传送至像素的电压增加而影响显示亮度。

接续前述时序,当级第一信号S1,n转为高电位关闭第一晶体管T51及第二晶体管T52,当多工器信号MUX,n依序将数据电压写入完成后,当级第二信号S2,n开启数据晶体管Tdata,将数据电压耦合至该控制节点VT,即将数据线的电压信号由数据线电容Cdata写入到像素的驱动电容53。在本实施例中,第一晶体管T51及晶体管T2同样不会同时开启,避免由高电压源OVDD朝向第一参考电压Vref N产生漏电路径,造成整面的显示亮度被扯动而有闪烁的问题。

在前述实施例中,第一实施例及第二实施例虽然能省去设置晶体管的数量,但必须增加新的信号线路以控制晶体管,在实际实施时可考量显示装置的需求加以调整。通过栅极节点驱动电路及控制节点驱动电路的设置,可以避免多工器在信号依序传递时,栅极节点无足够时间回拉至预设电压的问题,使得显示装置显示时,不会亮度上的差异,例如最末多工器若对应于红色子像素,则画面有偏红的情况产生,当以本公开的驱动电路实施时,可有效降低颜色偏移的状况。

以上所述仅为举例性,而非为限制性者。任何未脱离本发明的精神与范畴,而对其进行的等效修改或变更,均应包含于后附的权利要求书中。