一种用于信号安全设备的输入电路

文献发布时间:2023-06-19 09:47:53

技术领域

本发明属于轨道交通信号技术领域,具体涉及一种用于信号安全设备的输入电路,可广泛用于轨道交通信号控制中的联锁、ATP等安全性要求SIL4的设备中。

背景技术

城市轨道信号设备对RAMS有着最高的要求,其中安全性指标明确规定为信号系统安全设备导向危险侧的概率为10

目前,在轨道交通设备中广泛使用的是采用脉冲经过被测试接点的方法,容易出现误判,本发明采用双向动态采集方法,同时对输出电路进行在线监测,使输入电路更加安全可靠。

发明内容

本发明所要解决的技术问题是针对上述现有技术的不足,提供一种用于信号安全设备的输入电路,提供了一种可用于轨道交通信号控制的动态采集实际电路,是一个可以应用在安全控制设备中的故障-安全电路。

为实现上述技术目的,本发明采取的技术方案为:

一种用于信号安全设备的输入电路,用于判断外部继电器接点是断开还是闭合,包括开关量存储模块、采集控制模块、第一收发检测模块和第二收发检测模块;

采集控制模块产生采集脉冲,第一收发检测模块和第二收发检测模块依次发送频率不同的脉冲,开关量存储模块根据第一收发检测模块和第二收发检测模块回读到脉冲信息的情况判断外部继电器的状态及第一收发检测模块和第二收发检测模块故障信息。

为优化上述技术方案,采取的具体措施还包括:

上述的采集控制模块上电后,循环产生32路采样脉冲,先送第0路,然后送第1路,一直到第31路;在每一路中,先送第一收发检测模块光耦500KHz,占空比为50%的脉冲;后送第二收发检测模块光耦400KHz,占空比为50%的脉冲,当循环完成后,开始下次循环,该标志用作产生开关量存储模块的轮询控制信号。

在32路轮询检测过程中,开关量存储模块对每次的检测结果采用多点平均平滑滤波算法进行平滑滤波,排除干扰引起误判的影响。

32路轮循发送采集脉冲过程中,采集控制模块同一时间只有一路在发送采集脉冲,而32路上第二收发检测模块接收持续实时不断采集,如出现非轮循的另外一路或几路在采集电路的第一收发检测模块、第二收发检测模块接收端收到脉冲,则视为干扰;

若是轮循第n路时,在m路总能接收到脉冲,则判定该两路发生内部混线,若检测到此类故障,则把故障路所对应的寄存器位置1,外部设备通过VME总线来读取读寄存器。

32路每一轮的检测结果均经过平滑滤波后通过VME通道传输至MPU。

每路检测发送脉冲时第一收发检测模块第二收发检测模块分时发送,每一路检测过程中每次发送脉冲的时间窗口为30us。

上述的开关量存储模块进行脉冲检测时,当检测到该路的轮询控制信号时,根据时序关系恢复通道控制信号,等待2us,开始检测输入脉冲;

若检测成功,则输出相应的判定标志,即有无脉冲标志,该标志用于真值表判定,共有32路脉冲检测。

上述的开关量存储模块包括第一FPGA、第二FPGA和第三FPGA,第一FPGA、第二FPGA和第三FPGA在收到启动信号后经过光耦延迟开始数脉冲沿,对第一收发检测模块接收信号和第二收发检测模块接收信号的沿计数落在设定门限范围内时,认为该检测模块回路已接收到发送脉冲,否则认为该检测模块回路未接收到发送脉冲。

上述的第一收发检测模块包括第一光耦和第二光耦,第一光耦为第一收发检测模块发送端,第二光耦为第一收发检测模块接收端,第一光耦和第二光耦组成第一检测回路;

所述第二收发检测模块包括第三光耦和第四光耦,第三光耦为第二收发检测模块发送端,第四光耦为第二收发检测模块接收端,第三光耦和第四光耦组成第二检测回路;

第一光耦和第三光耦通过发送脉冲各自独立检测回路的硬件电路的正确性;

如果第一收发检测模块第一光耦发送的脉冲,第二光耦接收不到脉冲,则第一收发检测模块回路有故障;

如果第二收发检测模块第三光耦发送的脉冲,第四光耦接收不到脉冲,则第二收发检测模块回路有故障;

只有在第一收发检测模块和第二收发检测模块电路都没有故障时,第一收发检测模块第一光耦发送脉冲,第二收发检测模块能接收,或者第二收发检测模块第三光耦发送脉冲,第一收发检测模块能收到,此时判断外部继电器触点已闭合,否则判断为外部继电器触点断开。

上述的第一收发检测模块和第二收发检测模块发送不同特定频率的脉冲,以排除单一频率持续干扰脉冲的影响。

本发明具有以下有益效果:

a)设计为内在式故障-安全电路,任何器件故障都不会导致危险侧的误判发生(不会将未闭合继电器触点判为闭合)。

b)采用上下对称式双重收发检测模式(即第一收发检测模块和第二收发检测模块),确保任何器件故障导致的功能丢失或功能错误都可被检测。

c)上端与下端(即第一收发检测模块和第二收发检测模块)发送采集脉冲采用不同频率及严格的频率检测,极大地降低由于外部、内部干扰而产生的危险侧误判的概率。

d)对采集判断结果进行滤波,可进一步降低由于干扰导致的偶然误判的概率。

e)采用32路采集脉冲轮循发送,32路实时接收的方式,采集功能可检测内部混线、干扰产生的故障。

附图说明

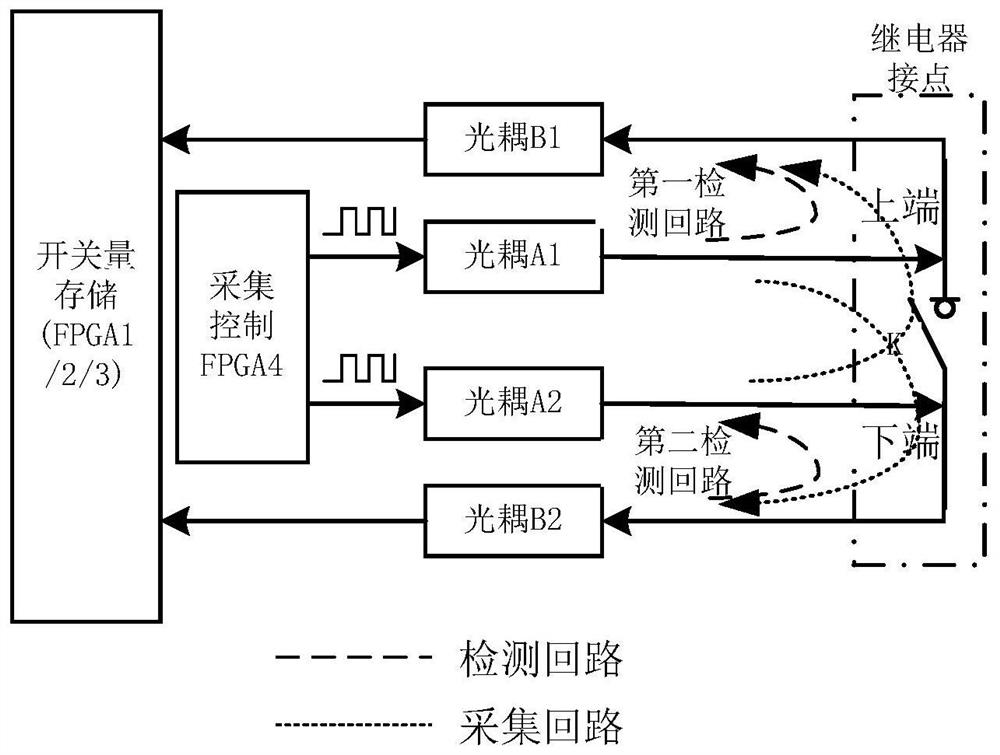

图1是本发明的结构示意图;

图2是本发明的实施例示意图。

其中的附图标记为:A1-第一光耦、B1-第二光耦、A2-第三光耦、B2-第四光耦。

具体实施方式

以下结合附图对本发明的实施例作进一步详细描述。

在通常的电子电路中,对开关K的闭合和断开采用输出电平直接判断的方法,存在开关实际状态是闭合,由于断线原因,读出来是断开;和开关实际状态是断开,由于混线或短路等原因,造成读取回来是闭合,对于安全相关设备不可用。本发明采用动态采集和脉冲检测的方法,可以有效解决上述问题。

参见图1,本发明的一种用于信号安全设备的输入电路,用于判断外部继电器接点是断开还是闭合,包括开关量存储模块、采集控制模块(实施例采用FPGA4)、第一收发检测模块(实施例中作为上端检测模块)和第二收发检测模块(实施例中作为下端检测模块);

实施例中,所述第一收发检测模块包括第一光耦A1和第二光耦B1,第一光耦A1为第一收发检测模块发送端,第二光耦B1为第一收发检测模块接收端,第一光耦A1和第二光耦B1组成第一检测回路;

所述第二收发检测模块包括第三光耦A2和第四光耦B2,第三光耦A2为第二收发检测模块发送端,第四光耦B2为第二收发检测模块接收端,第三光耦A2和第四光耦B2组成第二检测回路;

FPGA4负责产生脉冲,第一光耦A1和第三光耦A2通过发送脉冲各自独立检测回路的硬件电路的正确性;

如果第一收发检测模块第一光耦A1发送的脉冲,第二光耦B1接收不到脉冲,则第一收发检测模块回路有故障;

如果第二收发检测模块第三光耦A2发送的脉冲,第四光耦B2接收不到脉冲,则第二收发检测模块回路有故障;

只有在第一收发检测模块和第二收发检测模块电路都没有故障时,第一收发检测模块第一光耦A1发送脉冲,第二收发检测模块能接收,或者第二收发检测模块第三光耦A2发送脉冲,第一收发检测模块能收到,此时判断外部继电器触点已闭合,否则判断为外部继电器触点断开。详细继电器触点状态判定及故障判断真值表见表1。

表1电器状态及故障判断真值表

图2为采集功能模块中采集电路的具体实现,32路采集电路完全相同,图中表示单路。

由该图可见,发送路发送脉冲信号,只有对端接收到相同的脉冲信号才有可能判为外部继电器触点闭合,而任何器件故障(开路、短路等)只可能导致接收端收不到脉冲,采集功能模块设计为内在式故障-安全电路,任何器件故障都不会导致危险侧的误判发生(不会将未闭合继电器触点判为闭合)。

采集时,采集控制模块产生采集脉冲,第一收发检测模块和第二收发检测模块依次发送频率不同的脉冲,开关量存储模块根据第一收发检测模块和第二收发检测模块回读到脉冲信息的情况判断外部继电器的状态及第一收发检测模块和第二收发检测模块故障信息。

所述开关量存储模块包括第一FPGA、第二FPGA和第三FPGA(即图1中的FPGA1/2/3),第一FPGA、第二FPGA和第三FPGA在收到启动信号后经过5us(光耦延迟)开始数脉冲沿,对第一收发检测模块接收信号和第二收发检测模块接收信号的沿计数落在设定门限范围内时,认为该检测模块回路已接收到发送脉冲,否则认为该检测模块回路未接收到发送脉冲。

可见,判定脉冲接收的条件不仅仅要包括检测到脉冲,而且脉冲在一定采集周期内的数量必须符合一个既规定上限又规定下限的阈值范围。

由于第一收发检测模块、第二收发检测模块发送不同特定频率的脉冲,也会排除单一频率持续干扰脉冲的影响。第一收发检测模块与第二收发检测模块发送采集脉冲采用不同频率及严格的频率检测,极大地降低了外部干扰产生的危险侧的误判。

所述采集控制模块上电后,循环产生32路采样脉冲,先送第0路,然后送第1路,一直到第31路;在每一路中,先送第一收发检测模块光耦500KHz,占空比为50%的脉冲;后送第二收发检测模块光耦400KHz,占空比为50%的脉冲,当循环完成后,开始下次循环,该标志用作产生开关量存储模块的轮询控制信号。一次循环需要时间3.84ms。

由于判定“收到采集脉冲”的条件较为严格,FPGA1/2/3应当过滤掉由于干扰而导致的“未收到采集脉冲”此种误判,在32路轮询检测过程中,开关量存储模块对每次的检测结果采用多点平均平滑滤波算法进行平滑滤波,排除干扰引起误判的影响,滤波点数可配置。

32路轮循发送采集脉冲过程中,采集控制模块同一时间只有一路在发送采集脉冲,而32路上第二收发检测模块接收持续实时不断采集,如出现非轮循的另外一路或几路在采集电路的第一收发检测模块、第二收发检测模块接收端偶尔收到脉冲,则视为干扰;

若是轮循第n路时,在m路总能接收到脉冲,则判定该两路发生内部混线,若检测到此类故障,则把故障路所对应的寄存器位置1,外部设备通过VME总线来读取读寄存器。

32路每一轮的检测时间不超过10ms,每一轮的检测结果都将经过平滑滤波后通过VME通道传输至MPU。

滤波方案采取最简单的取平均值方案,初步设定平滑滤波的长度为7,则该滤波器的群延时为3个单位,即滤波器输出端的变化比实际检测的变化慢3轮。

每路检测发送脉冲时第一收发检测模块第二收发检测模块分时发送,每一路检测过程中每次发送脉冲的时间窗口为30us。

每路检测发送脉冲时第一收发检测模块第二收发检测模块需分时发送,由此计算,每一路检测过程中每次发送脉冲的时间窗口理论上最大为10ms/32/3/2≈50us。为留足裕量,实际脉冲发送时间约为理论最大负载值的70%左右,约为30us。由于脉冲检测采取脉冲计数的方法,所以每个发送周期内发送的脉冲数越多,系统由于收到干扰而将干扰误判为合法脉冲的概率越小。脉冲发送时间窗口的上限已经确定,故只能提高发送脉冲的频率。若FPGA4发送频率为500KHz的脉冲,在一个发送时间窗口内至少可发送15个脉冲。光耦的最大频率为1MHz,FPGA4发送脉冲的频率最大也不应超过1MHz。

在FPGA1/2/3接收端脉冲计数时,首先要考虑发送端与接受端由于线路长度而导致的延时,在发送脉冲为500KHz时,为使该延时不超过半个脉冲周期即1us,则继电器检测线路的最大长度为150m。因为有延时的存在,脉冲发送端应当多发送一个周期的脉冲。其次考虑脉冲计数的窗长。如果窗长恰好为15个脉冲周期,由于上跳沿对齐问题则接收到的脉冲数可能为14、15、16个;若窗长为15.5个周期,则接收到的脉冲数只可能为15或16个,判定条件可更严格。

该脉冲接收判定条件对于接收到脉冲的判定比较严格,将干扰误判为合法脉冲的概率很低。由于继电器判为断开为安全侧,该判定方法符合当收到干扰时判定倾向安全的原则。

FPGA1/2/3功能是进行脉冲检测时,当检测到该路的轮询控制信号时,根据时序关系恢复通道控制信号,等待2us,开始检测输入脉冲;

若检测成功,则输出相应的判定标志,即有无脉冲标志,该标志用于真值表判定,共有32路脉冲检测。

工作原理如下:

第一收发检测模块先发送500khz脉冲检测,FPGA开24.5x2us的时间窗,在该时间窗内,检测到24个或25个脉冲上升沿,则该路光耦接收到500khz的脉冲。

第二收发检测模块后发送400khz脉冲检测,FPGA开19.5x2.5us的时间窗,在该时间窗内,检测到19个或20个脉冲上升沿,则该路光接收到400khz的脉冲。

在一个通道中,500khz脉冲检测与400khz脉冲检测为独立的检测模块;约定FPGA4首先在第一收发检测模块光耦发送500khz脉冲,第二收发检测模块光耦发送高电平,因此FPGA1/2/3知道FPGA4的第一收发检测模块光耦在输出500k脉冲,此时500khz脉冲检测模块有效,若检测到400khz的脉冲,则会当成干扰;60us后FPGA4在第二收发检测模块光耦发送400khz脉冲,第一收发检测模块光耦发送高电平,因此FPGA1/2/3知道FPGA4的第二收发检测模块光耦在输出400k脉冲,此时400khz脉冲检测模块有效,若检测到500khz的脉冲,则会当成干扰。任何时刻,FPGA1/2/3均知道第几路的第一收发检测模块光耦还是第二收发检测模块光耦在发送脉冲,且知道应该是400khz还是500khz的脉冲,因此不会误判。

以上仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,应视为本发明的保护范围。

- 一种用于信号安全设备的输入电路

- 混频器电路、包括混频器电路的接收器、用于通过使输入信号与振荡器信号混频来产生输出信号的方法