晶圆及其制造方法

文献发布时间:2023-06-19 11:14:36

技术领域

本发明涉及存储器领域。具体而言,本发明涉及晶圆及其制造方法,其中焊盘引线从所述晶圆的背面引出。

背景技术

混合键合(Hybrid Bonding,HB)技术是近年来在CMOS图像传感器的基础上发展起来的一种晶圆级电子连接(Wafer Level Electrical Connection)技术。

现有技术中的芯片级电子连接(Wafer Level Electrical Connection)主要应用在输入输出接口(I/O Interface)互联中,而新出现的晶圆级电子连接主要应用于功能电路连接。

图1A至图1C示出了现有技术中混合键合的工艺步骤。图1A示出了分别在不同工艺中制作的逻辑晶圆(Logic Wafer)和动态随机存储器(DRAM)晶圆,其中示出的逻辑晶圆至少包括逻辑晶圆衬底和逻辑晶圆的顶层金属,DRAM晶圆至少包括DRAM晶圆衬底和DRAM晶圆的顶层金属。图1B中示出了在逻辑晶圆和DRAM晶圆上生长键合柱子,其中示出了在逻辑晶圆上生长逻辑晶圆的通孔以及逻辑晶圆的顶层金属与逻辑晶圆的通孔的连接部,在DRAM晶圆上生长DRAM晶圆的通孔以及DRAM晶圆的顶层金属与DRAM晶圆的通孔的连接部。图1C示出了图1A和图1B所示出的逻辑晶圆和DRAM晶圆的面对面键合。

图2示出了现有技术中所普遍采用的从晶圆的正面引出焊盘引线的一个例子。在图2中,从晶圆的顶层金属(在此为第三层金属)引出了焊盘引线。

在混合键合中,逻辑晶圆和DRAM晶圆在正面面对面键合之后,无法从正面引出与外部互连的信号线。此外,在现有技术诸如图2中从晶圆的正面引出焊盘引线时,芯片内部的信号通过离衬底最近的金属层(在图2中为第一层金属、第二层金属)等一直连接到顶层金属,多层金属的层叠,会让信号上的寄生电容很大,影响输出信号的质量,同时也会通过寄生的电容耦合,影响其他信号的质量。

因此,亟需解决现有技术中的上述技术问题。

发明内容

本发明涉及晶圆及其制造方法及对应的电子设备。在所述晶圆中,焊盘引线从距离晶圆的衬底最近的第一层金属引出,解决了现有技术中晶圆正面混合键合之后无法引出焊盘引线的技术问题,同时不存在多层金属的层叠,使得输入输出焊盘电容较小,对输出信号以及其他信号的影响较小。

根据本发明的第一方面,提供了一种晶圆,所述晶圆至少包括:

衬底;以及,

位于衬底上的M层金属,所述M层金属与衬底的距离彼此不同;其特征在于,

焊盘引线,所述焊盘引线从距离所述衬底最近的第一层金属引出;

其中,M为大于或等于1的正整数。

根据本发明的晶圆的一个优选实施方案,所述晶圆为逻辑晶圆与存储器晶圆进行混合键合之后得到的组合晶圆。

根据本发明的晶圆的一个优选实施方案,所述焊盘引线从距离所述逻辑晶圆的衬底最近的第一层金属引出。

根据本发明的晶圆的一个优选实施方案,所述焊盘引线从距离所述存储器晶圆的衬底最近的第一层金属引出。

根据本发明的晶圆的一个优选实施方案,第一焊盘引线从距离所述逻辑晶圆的衬底最近的第一层金属引出,以及第二焊盘引线从距离所述存储器晶圆的衬底最近的第一层金属引出。

根据本发明的晶圆的一个优选实施方案,所述M层金属之间通过信号线进行通信。

根据本发明的晶圆的一个优选实施方案,所述焊盘引线从所述衬底中的衬底厚度相对薄的位置处引出,所述衬底厚度相对薄的位置是通过打磨工艺来得到的。

根据本发明的晶圆的一个优选实施方案,在所述衬底厚度相对薄的位置处存在孔,所述焊盘引线通过所述孔从所述第一层金属引出。

根据本发明的晶圆的一个优选实施方案,所述衬底厚度相对薄是指衬底厚度为3微米。

根据本发明的晶圆的一个优选实施方案,所述孔中存在第一背部焊盘。

根据本发明的晶圆的一个优选实施方案,所述第一背部焊盘连接所述第一层金属与第二背部焊盘,所述焊盘引线与所述第二背部焊盘连接。

根据本发明的晶圆的一个优选实施方案,所述第二背部焊盘是铝焊盘。

根据本发明的第二方面,提供了一种电子设备,所述电子设备包括根据上面任一实施方案所述的晶圆。

根据本发明的第三方面,提供了一种制造晶圆的方法,所述方法至少包括:

生产晶圆的衬底;

设置位于所述晶圆的衬底上的M层金属,其中所述M层金属与衬底的距离彼此不同;

从距离所述衬底最近的第一层金属引出焊盘引线;

其中,M为大于或等于1的正整数。

根据本发明的方法的一个优选实施方案,所述晶圆为逻辑晶圆与存储器晶圆进行混合键合之后得到的组合晶圆。

根据本发明的方法的一个优选实施方案,所述方法还包括:

从距离所述逻辑晶圆的衬底最近的第一层金属引出所述焊盘引线。

根据本发明的方法的一个优选实施方案,所述方法还包括:

从距离所述存储器晶圆的衬底最近的第一层金属引出所述焊盘引线。

根据本发明的方法的一个优选实施方案,所述方法还包括:

从距离所述逻辑晶圆的衬底最近的第一层金属引出第一焊盘引线,以及从距离所述存储器晶圆的衬底最近的第一层金属引出第二焊盘引线。

根据本发明的方法的一个优选实施方案,所述方法还包括:

所述M层金属之间通过信号线进行通信。

根据本发明的方法的一个优选实施方案,所述方法还包括:

从所述衬底中的衬底厚度相对薄的位置处引出所述焊盘引线,通过打磨工艺得到所述衬底厚度相对薄的位置。

根据本发明的方法的一个优选实施方案,所述方法还包括:

在所述衬底厚度相对薄的位置处设置孔,以及通过所述孔从所述第一层金属引出所述焊盘引线。

根据本发明的方法的一个优选实施方案,所述方法还包括:

将相对薄的衬底厚度设置成3微米的衬底厚度。

根据本发明的方法的一个优选实施方案,所述方法还包括:

在所述孔中设置第一背部焊盘。

根据本发明的方法的一个优选实施方案,所述方法还包括:

所述第一背部焊盘连接所述第一层金属与第二背部焊盘,所述焊盘引线与所述第二背部焊盘连接。

根据本发明的方法的一个优选实施方案,所述方法还包括:

将所述第二背部焊盘设置成铝焊盘。

根据本发明的第四方面,提供了一种电子设备,所述电子设备包括根据上面任一项所述的方法制造的晶圆。

附图说明

通过下文结合对附图的说明,将更容易理解本发明,其中:

图1A至图1C示出了现有技术中混合键合的工艺步骤。

图2示出了现有技术中从晶圆的正面引出焊盘引线的一个例子。

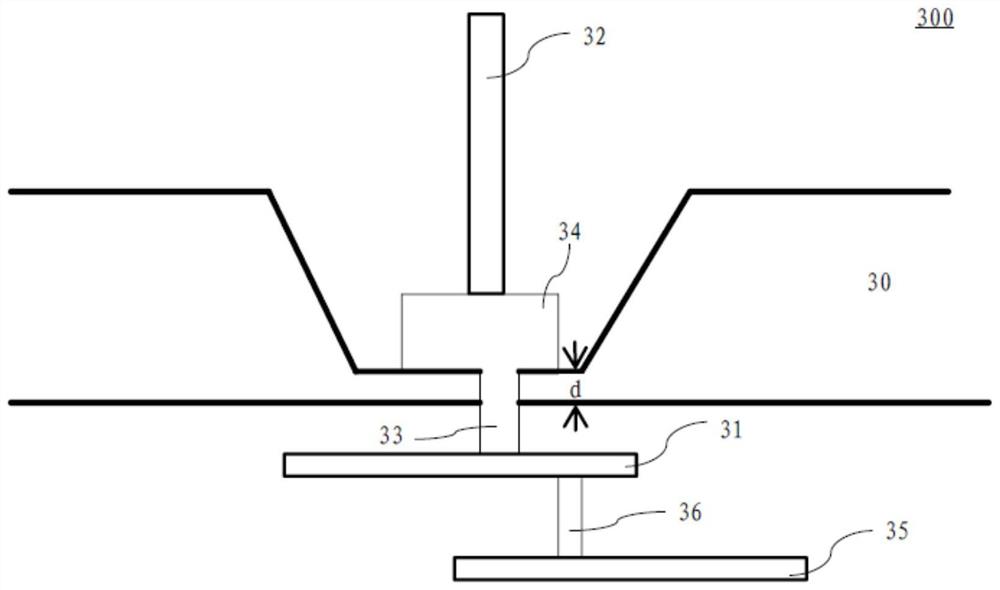

图3示出了在根据本发明的晶圆中引出焊盘引线的总体示意截面图。

图4是根据本发明的一个实施方案的晶圆截面的示意图。

图5是根据本发明的另一实施方案的晶圆截面的示意图。

图6是根据本发明的又一实施方案的晶圆截面的示意图。

图7是根据本发明的制造晶圆的方法的一个实施方案的流程图。

具体实施方式

下面将结合附图来对本发明的实施方案进行进一步详述。

图3示出了根据本发明的晶圆中引出焊盘引线的总体示意截面图。

图3中所示出的晶圆300可以是逻辑晶圆,也可以是存储器晶圆诸如DRAM晶圆,还可以是逻辑晶圆与存储器晶圆混合键合之后所得到的组合晶圆。

在本文中,逻辑晶圆指的是实现逻辑功能的晶圆,存储器晶圆是实现存储功能的晶圆。

如图3所示,晶圆300包括:衬底30;以及,位于衬底30上的第一层金属31和第二层金属35。

本领域技术人员应理解,晶圆300中的第一层金属31和第二层金属35都是在衬底30上制备的。晶圆300的衬底可以由诸如现有技术中已知的半导体单晶材料制成,金属层可以由诸如现有技术中已知的铝材料制成。

另外,由于本发明中的焊盘引线32是从衬底30的背面引出的,为更清楚地阐释本发明的主旨,图3中示出了晶圆300经过翻转之后的截面图。此外,为避免模糊本发明的主旨,图3中仅示出了晶圆的一部分,本领域技术人员应当知晓晶圆300还包括图3中未示出的一些构件。

在图3中,第一层金属31和第二层金属35与衬底30的距离彼此不同,第一层金属31距离衬底30较近,第二层金属35距离衬底30较远。应理解,出于解释的目的,图3中仅示出了两层金属。事实上,晶圆300可以包括多层金属。在晶圆300包括多层金属的情况下,多层金属与衬底30的距离彼此不同。

如图3所示,晶圆300中的焊盘引线32从距离衬底30最近的第一层金属31引出。如果内部信号来自第二层金属35或者更高层金属,则第二层金属35或者更高层金属通过较细的信号线诸如信号线36而被连接至第一层金属31。

这样,解决了现有技术中逻辑晶圆和存储器晶圆在正面面对面混合键合之后无法引出与外部互连的焊盘引线的技术问题。另外,由于焊盘引线32从第一层金属31引出,不存在多层金属的层叠,使得输入输出焊盘电容较小,对输出信号以及其他信号的影响较小。

下面结合图3进一步详述引出焊盘引线32的具体操作步骤。

第一步,将晶圆300的衬底30打磨薄,使得衬底30的厚度d(如图3中所示出的)为约3微米。此处所使用的打磨工艺可以是现有技术中任何一种,只要能够将衬底打磨薄即可。

另外,应理解,此处提及的衬底厚度为3微米是优选的,并非必须为此数值。此数值可以随着技术的发展而变化。

第二步,通过蚀刻,在厚度d为约3微米的位置进行蚀刻开孔。

应注意,开孔的深度需要达到第一层金属31,以使得焊盘引线32能够从第一层金属31引出。

此处所提及的蚀刻工艺可以采用现有技术中已知的任何蚀刻工艺,诸如可以先在表面涂敷一层光致抗蚀剂,然后透过掩模对抗蚀剂层进行选择性曝光,由于抗蚀剂层的已曝光部分和未曝光部分在显影液中的溶解速度不同,经过显影后在衬底表面留下了抗蚀剂图形,以此为掩模就可对衬底表面进行选择性腐蚀。

第三步,在孔中蚀刻出第一背部焊盘33,所述第一背部焊盘33可以是铝焊盘。

第四步,在第一背部焊盘33上生长第二背部焊盘34,焊盘引线32连接至第二背部焊盘34。所述第二背部焊盘34也可以是铝焊盘。此处所提及的生长工艺是现有技术中已知的金属生长工艺。

这样就实现了从晶圆300的衬底上的第一层金属31引出焊盘引线32。

图4是根据本发明的一个实施方案的晶圆截面的示意图。

图4中所示出的晶圆400是逻辑晶圆和存储器晶圆混合键合之后所得到的组合晶圆。图4中示出的虚线上半部分是逻辑晶圆,虚线下半部分是存储器晶圆。逻辑晶圆经翻转之后与存储器晶圆进行混合键合。在此,为避免模糊本发明的主旨,未对混合键合工艺进行进一步详述。

在图4中示出的晶圆400中,焊盘引线42从逻辑晶圆的衬底40上的第一层金属41引出。为了清楚地展示焊盘引线42的引出,图4中示出的逻辑晶圆包括:衬底40;第一层金属41;焊盘引线42;第一背部焊盘43;第二背部焊盘44。

由于图4中未从存储器晶圆引出焊盘引线,所以仅示意性地示出了存储器晶圆包括衬底40’和第一层金属41’。

图5是根据本发明的另一实施方案的晶圆截面的示意图。

图5中所示出的晶圆500是逻辑晶圆和存储器晶圆混合键合之后所得到的组合晶圆。图5中示出的虚线上半部分是逻辑晶圆,虚线下半部分是存储器晶圆。逻辑晶圆经翻转之后与存储器晶圆进行混合键合。再次,为避免模糊本发明的主旨,未对混合键合工艺进行进一步详述。

在图5中示出的晶圆500中,焊盘引线52从逻辑晶圆中的第一层金属51引出。为了清楚地展示焊盘引线52的引出,图5中示出的逻辑晶圆包括:衬底50;第一层金属51;焊盘引线52;第一背部焊盘53;第二背部焊盘54。

另外,在图5中示出的晶圆500中,焊盘引线52’从存储器晶圆中的第一层金属51’引出。为了清楚地展示焊盘引线52’的引出,图5中示出的存储器晶圆包括:衬底50’;第一层金属51’;焊盘引线52’;第一背部焊盘53’;第二背部焊盘54’。

图6是根据本发明的一个实施方案的晶圆截面的示意图。

图6中所示出的晶圆600是逻辑晶圆和存储器晶圆混合键合之后所得到的组合晶圆。图6中示出的虚线上半部分是逻辑晶圆,虚线下半部分是存储器晶圆。逻辑晶圆经翻转之后与存储器晶圆进行混合键合。在此,为避免模糊本发明的主旨,未对混合键合工艺进行进一步详述。

在图4中示出的晶圆600中,焊盘引线62’从存储器晶圆的衬底60’上的第一层金属61’引出。为了清楚地展示焊盘引线62’的引出,图6中示出的存储器晶圆包括:衬底60’;第一层金属61’;焊盘引线62’;第一背部焊盘63’;第二背部焊盘64’。

由于图6中未从逻辑晶圆引出焊盘引线,所以仅示意性地示出了逻辑晶圆包括衬底60和第一层金属61。

图7是根据本发明的制造晶圆的方法的一个实施方案的流程图。

步骤701:生产晶圆的衬底。

步骤702:设置位于所述晶圆的衬底上的M层金属,其中所述M层金属与衬底的距离彼此不同;其中,M为大于或等于1的正整数。

步骤703:从距离所述衬底最近的第一层金属引出焊盘引线。

应注意,上文所提及的实施方案例示而非限制本发明,且在不脱离所附权利要求的范围的前提下,本领域技术人员将能够设计许多替代实施方案。应理解,本发明的范围由权利要求限定。

- 接合晶圆及其制造方法、弹性波器件的制造方法、压电材料晶圆及非压电材料晶圆

- 晶圆组、晶圆的制造装置及晶圆的制造方法