芯片封装结构及其形成方法

文献发布时间:2023-06-19 11:49:09

技术领域

本公开实施例涉及芯片封装结构及其形成方法,特别是涉及具有环形结构的芯片封装结构及其形成方法。

背景技术

半导体装置用于各种不同的电子应用,例如个人电脑、手机、数码相机、以及其他电子设备。半导体装置的制造通常是通过依序沉积绝缘层或介电层、导线层、以及半导体层于半导体基底之上,并且使用微影制程和蚀刻制程图案化各种不同的材料层,以形成电路组件和元件于其上。

通常,在半导体晶圆上制造许多集成电路(integrated circuit,IC),集成电路材料和设计的技术进步已经产生了几代集成电路。每一代电路都比上一代电路更小、更复杂。晶圆的晶粒(die)的处理和封装可采用芯片级(wafer-level)进行,并且已经开发了用于芯片级封装的各种技术。由于芯片封装结构可能需要包含具有多种功能的多个芯片,因此要形成具有多个芯片的可靠芯片封装结构仍充满挑战。

发明内容

本公开实施例提供芯片封装结构的形成方法。此方法包含设置第一芯片结构和第二芯片结构于线路基板之上。第一芯片结构与第二芯片相隔一间隙。此方法还包含设置环形结构于线路基板之上。环形结构具有第一开口,第一芯片结构和第二芯片结构位于第一开口中,第一开口具有第一内壁,第一内壁具有第一凹陷,且间隙朝向第一凹陷延伸。

本公开实施例提供芯片封装结构的形成方法。此方法包含设置第一芯片结构和第二芯片结构于线路基板之上。第一芯片结构与第二芯片结构相隔一间隙。此方法还包含设置环形结构于线路基板之上。环形结构围绕第一芯片结构和第二芯片结构,环形结构包含彼此连接的第一较薄部分和第一较厚部分,且间隙靠近第一较薄部分。

本公开实施例提供芯片封装结构。此芯片封装结构包含线路基板。此芯片封装结构包含位于线路基板之上的第一芯片结构和第二芯片结构。第一芯片结构与第二芯片结构相隔一间隙。此芯片封装结构包含位于线路基板之上的环形结构。线路基板具有开口,第一芯片结构和第二芯片结构位于开口中,开口具有内壁,内壁具有凹陷,且间隙朝向凹陷延伸。

附图说明

通过以下的详细描述配合所附图示,可以更加理解本公开实施例的内容。需强调的是,根据产业上的标准惯例,许多部件(feature)并未按照比例绘制。事实上,为了能清楚地讨论,各种部件的尺寸可能被任意地增加或减少。

图1A-图1E是根据一些实施例的形成芯片封装结构的制程在各个阶段的剖面示意图。

图1A-1是根据一些实施例的图1A的芯片封装结构的上视示意图。

图1B-1是根据一些实施例的图1B的芯片封装结构的上视示意图。

图1C-1是根据一些实施例的图1C的芯片封装结构的上视示意图。

图1D-1是根据一些实施例的图1D的芯片封装结构的上视示意图。

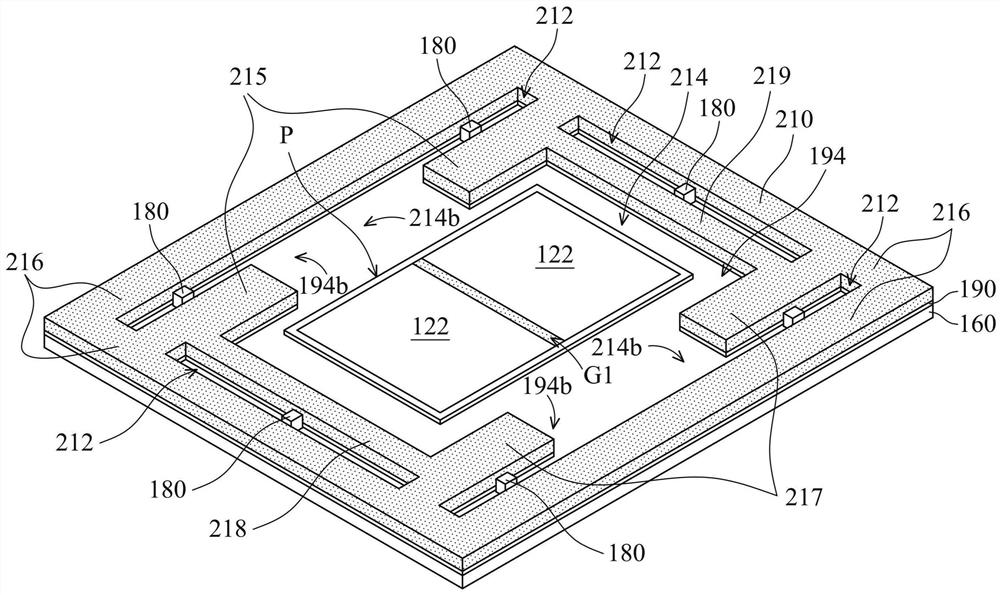

图1D-2是根据一些实施例的图1D的芯片封装结构的透视示意图。

图1D-3是根据一些实施例的图1D的芯片封装结构的环形结构的上视示意图。

图1E-1是根据一些实施例的图1E的芯片封装结构的上视示意图。

图1E-2是根据一些实施例的图1E的芯片封装结构的透视示意图。

图2A是根据一些实施例,显示芯片封装结构的剖面示意图。

图2B是根据一些实施例,显示图2A的芯片封装结构的上视示意图。

图2C是根据一些实施例,显示图2A的芯片封装结构的透视示意图。

图2D是根据一些实施例,显示图2A的环形结构的透视示意图。

图2E是根据一些实施例,显示图2A的芯片封装结构但没有环形结构的上视示意图。

图3A是根据一些实施例,显示芯片封装结构的透视示意图。

图3B是根据一些实施例,显示图3A的芯片封装结构但没有环形结构的上视示意图。

图4A是根据一些实施例,显示芯片封装结构的剖面示意图。

图4B是根据一些实施例,显示图4A的芯片封装结构的上视示意图。

图4C是根据一些实施例,显示图4A的芯片封装结构的透视示意图。

图4D是根据一些实施例,显示图4A的芯片封装结构但没有环形结构的上视示意图。

图4E是根据一些实施例,显示图4A的环形结构和粘着层的展开示意图。

图5是根据一些实施例,显示芯片封装结构的上视示意图。

图6是根据一些实施例,显示芯片封装结构的上视示意图。

图7是根据一些实施例,显示芯片封装结构的上视示意图。

图8是根据一些实施例,显示芯片封装结构的上视示意图。

图9是根据一些实施例,显示芯片封装结构的剖面示意图。

图10是根据一些实施例,显示芯片封装结构的剖面示意图。

其中,附图标记说明如下:

100:芯片封装结构

108:导电柱

110:重布线结构

111:底面

112:线路层

114:导电通孔

116:介电层

122:芯片结构

122a:侧壁

124:导电柱

130:底部填充层

140:模塑层

150:焊料凸块

160:线路基板

162:介电层

164:导电垫

166:线路层

168:导电通孔

170:底部填充层

180:装置

190:粘着层

192:沟槽

194:开口

194a:内壁

194b:凹陷

196:侧壁

200:芯片封装结构

210:环形结构

210A:较低部分

210B:较上部分

211:底面

211A:部分

212:沟槽

212A:沟槽

213:侧壁

214:开口

214a:内壁

214b:凹陷

214b1:内壁

214A:凹陷

215:条状部分

215a:端

216:外环

216a:顶面

216b:顶面

216A:较薄部分

216C:较薄部分

216B:较厚部分

216D:较厚部分

217:条状部分

217a:端

218:条状部分

219:条状部分

220:盖件

300:芯片封装结构

400:芯片封装结构

410:粘着层

412:沟槽

414:开口

414a:内壁

414b:凹陷

500:芯片封装结构

510:环形结构

510A:较窄部分

510B:较宽部分

512:开口

512a:内壁

512b:凹陷

600:芯片封装结构

612:部分

614:部分

616:间隙

700:芯片封装结构

800:芯片封装结构

A:粘着层

D1:距离

D2:距离

D3:横向距离

G1:间隙

G2:间隙

P:封装结构

W122:宽度

W220:宽度

W510A:线宽

W510B:线宽

具体实施方式

以下内容提供了很多不同的实施例或范例,用于实现本公开实施例的不同部件。组件和配置的具体实施例或范例描述如下,以简化本公开实施例。当然,这些仅仅是范例,并非用以限定本公开实施例。举例来说,叙述中若提及第一部件形成于第二部件之上,可能包含形成第一和第二部件直接接触的实施例,也可能包含额外的部件形成于第一和第二部件之间,使得第一和第二部件不直接接触的实施例。为了简洁和明确起见,各种不同的部件可以不同尺寸任意显示。另外,本公开实施例可能在许多范例中重复元件符号及/或字母。这些重复是为了简化和清楚的目的,其本身并非代表所讨论各种实施例及/或配置之间有特定的关系。

此外,此处可能使用空间上的相关用语,例如“在…之下”、“在…下方”、“下方的”、“在…上方”、“上方的”和其他类似的用语可用于此,以便描述如图所示的一元件或部件与其他元件或部件之间的关系。此空间上的相关用语除了包含图示显示的方位外,也包含使用或操作中的装置的不同方位。当装置被转至其他方位时(旋转90度或其他方位),则在此所使用的空间相对描述可同样依旋转后的方位来解读。

在叙述中,用语“大致上(substantially)”,例如“大致上平坦”或“大致上共平面”将被本领域中的通常知识者所理解。在一些实施例中,基本上可将形容词移除。在适用的情况下,用语“大致上”也可包含具有“完整地(entirely)”、“完全地(completely)”、“所有地(all)”的实施例。在适用的情况下,用语“大致上”也可涉及90%或更多,例如95%或更多,尤其是99%或更多,或包含100%。再者,用语“大致平行”或“大致垂直”将被解读为不排除与特定排列的微小偏差,并且可包含,例如高达10°的偏差。用语“大致上”不排除“完全地”,例如,“大致上不含(substantially free)”Y的组成X,可以是完全地不含Y。

用语“大约(about)”,其与特定距离或尺寸连用,应被解读为不排除与特定距离或尺寸的微小偏差,并且可包含,例如高达10°的偏差。用语“大约”与数值x的关系可以表示x±5或10%。

本文公开一些实施例。在这些实施例所提及的阶段之前、期间、或之后可提供额外的步骤。对于不同的实施例,可以置换或删减所述的一些阶段。可增加额外的部件至半导体装置结构。对于不同的实施例,可以置换或删减以下所述的一些部件。尽管一些实施例是以特定顺序进行的步骤来讨论,但这些步骤可以其他符合逻辑的顺序来进行。

也可包含其他部件或制程。举例而言,可以包含测试结构,以帮助3D封装或3D-IC装置进行验证测试。测试结构可以包含,例如,形成于重布线(redistribution)层或基板上的测试垫(testing pad),其使3D封装或3D-IC进行测试、探针(probe)或探针卡(probecard)得以使用等等。可对中间结构和最终结构进行验证测试。另外,本文公开的结构和方法可与测试方法结合使用,这整合辨识良好晶粒(good die)的中间验证,以提高良率并降低成本。

图1A-图1E是根据一些实施例的形成芯片封装结构的制程在各个阶段的剖面示意图。图1A-1是根据一些实施例的图1A的芯片封装结构的上视示意图。

根据一些实施例,提供封装体P,如图1A和图1A-1所示。根据一些实施例,封装体P包含重布线结构110、芯片结构122、导电柱(conductive pillar)124、底部填充(underfill)层130、以及模塑(molding)层140。根据一些实施例,重布线结构110包含线路(wiring)层112、导电通孔(via)114、以及介电层116。

根据一些实施例,线路层112和导电通孔114形成于介电层116中。根据一些实施例,导电通孔114在不同的线路层112之间电性连接,如图1A所示。根据一些实施例,为了简洁,图1A仅显示两个线路层112。

根据一些实施例,介电层116由绝缘材料形成,例如聚合物材料(例如,聚苯并

根据一些实施例,使用沉积制程(例如,化学气相沉积制程或物理气相沉积制程)、微影制程、以及蚀刻制程,形成介电层116。根据一些实施例,线路层112和导电通孔114由导电材料形成,例如金属(例如,铜、铝、或钨)、或前述的合金。

根据一些实施例,芯片结构122通过导电柱124接合至重布线结构110。根据一些实施例,芯片结构122彼此隔开一间隙G1。根据一些实施例,导电柱124物理上且电性上连接于芯片结构122与重布线结构110之间。根据一些实施例,每一个芯片结构122包含芯片,例如系统上芯片(system on chip,SoC)。

根据一些实施例,芯片包含基底。在一些实施例中,基底由元素半导体材料形成,其包含单晶结构、多晶结构、或非晶结构的硅或锗。在其他一些实施例中,基底由化合物半导体形成(例如,碳化硅、砷化镓、磷化镓、磷化铟、或砷化铟)、合金半导体(例如,SiGe、或GaAsP)、或前述的组合。基底也可包含多层半导体、绝缘体上覆半导体(semiconductor oninsulator,SOI,例如绝缘体上覆硅、或绝缘体上覆锗)、或前述的组合。

在一些实施例中,基底包含各种装置元件。在一些实施例中,各种装置元件形成于基底中及/或于基底上。为了简洁明确,装置元件未显示于图示中。示范的各种装置元件包含主动元件、被动元件、其他适合元件、或前述的组合。主动元件可包含形成于基底表面处的晶体管或二极管(未显示)。被动元件可包含电阻、电容、或其他适合被动元件。

举例而言,晶体管可以是金属氧化物半导体场效晶体管(metal oxidesemiconductor field effect transistors,MOSFET)、互补式金属氧化物半导体(complementary metal oxide semiconductor,CMOS)晶体管、双接面晶体管(bipolarjunction transistors,BJT)、高压晶体管、高频晶体管、p通道及/或n通道场效晶体管(pFETs/nFETs)等。可进行各种制程(例如,前段(front-end-of-line,FEOL)半导体制造制程),以形成各种装置元件。前段半导体制造制程可包含沉积、蚀刻、植入、微影、退火、平坦化、一或多其他适用制程、或前述的组合。

在一些实施例中,隔离部件(未显示)形成于基底中。隔离部件用以定义主动区,并且电性隔离各种装置元件,装置元件形成于主动区中且于基底中及/或基底上。在一些实施例中,隔离部件包含浅沟槽隔离(shallow trench isolation,STI)部件、硅局部氧化物(local oxidation of silicon,LOCOS)部件、其他适合隔离部件、或前述的组合。

在其他一些实施例中,芯片结构122包含芯片封装结构。在一些实施例中,芯片封装结构包含一个芯片。在其他一些实施例中,芯片封装结构包含多个芯片,这些芯片并列或彼此堆叠(例如3D封装或3DIC装置)。

根据一些实施例,导电柱124由导电材料形成,例如铜(Cu)、铝(Al)、钨(W)、钴(Co)、镍(Ni)、或锌(Sn)。根据一些实施例,使用镀制制程形成导电柱124,例如电镀(electroplating)制程。

根据一些实施例,底部填充层130介于芯片结构122与重布线结构110之间,如图1A和图1A-1所示。根据一些实施例,底部填充层130围绕导电柱124和芯片结构122。

根据一些实施例,底部填充层130延伸至间隙G1中。根据一些实施例,间隙G1被底部填充层130填充。根据一些实施例,底部填充层130由绝缘材料形成,例如聚合物材料。

根据一些实施例,塑模层140形成于重布线结构110和底部填充层130之上,如图1A和图1A-1所示。根据一些实施例,塑模层140围绕芯片结构122、导电柱124、以及底部填充层130。根据一些实施例,塑模层140由绝缘材料形成,例如环氧树脂(epoxy)。

根据一些实施例,导电柱108形成于重布线结构110的底面111之上,如图1A和图1A-1所示。根据一些实施例,导电柱108由导电材料形成,例如铜(Cu)、铝(Al)、钨(W)、钴(Co)、镍(Ni)、或锌(Sn)。根据一些实施例,使用镀制制程形成导电柱108,例如电镀(electroplating)制程。

根据一些实施例,形成焊料凸块(solder bump)150于导电柱108之上,如图1A和图1A-1所示。根据一些实施例,焊料凸块150由锡(Sin)或熔点低于导电柱108的熔点的其他适合导电材料形成。根据一些实施例,使用镀制制程形成焊料凸块150,例如电镀(electroplating)制程。

图1B-1是根据一些实施例的图1B的芯片封装结构。根据一些实施例,通过焊料凸块150,将封装结构P接合至线路基板(wiring substrate)160,如图1B和图1B-1所示。根据一些实施例,线路基板160包含介电层162、导电垫(pad)164、线路层166和导电通孔168。

根据一些实施例,导电垫164形成于介电层162之上。根据一些实施例,焊料凸块150接合至导电垫164。根据一些实施例,线路层166和导电通孔168形成于介电层162中。

根据一些实施例,导电通孔168电性连接于不同的线路层166之间,并且连接于线路层166与导电垫164之间。根据一些实施例,为了简洁,图1B仅显示两个线路层166。

根据一些实施例,介电层162由绝缘材料形成,例如聚合物材料(例如,聚苯并

根据一些实施例,导电垫164由导电材料形成,例如金属(例如,铜、铝、或钨)、或前述的合金。根据一些实施例,线路层166由导电材料形成,例如金属(例如,铜、铝、或钨)、或前述的合金。根据一些实施例,导电通孔168由导电材料形成,例如金属(例如,铜、铝、或钨)、或前述的合金。

在一些实施例中,导电垫164、线路层166和导电通孔168由相同材料形成。在其他一些实施例中,导电垫164、线路层166和导电通孔168由不同材料形成。

根据一些实施例,形成底部填充层170于封装体P与线路基板160之间,如图1B和图1B-1所示。根据一些实施例,填充层170围绕导电柱108、焊料凸块150以及封装体P。根据一些实施例,底部填充层170由绝缘材料形成,例如聚合物材料。

根据一些实施例,将装置180接合至线路基板160,例如通过表面安装技术(surface mount technology,SMT),如图1B和图1B-1所示。装置180包含被动装置、其他适合装置、或前述的组合。被动装置包含电阻、电容、电感、或其他适合被动装置。

图1C-1是根据一些实施例的图1C的芯片封装结构的上视示意图。根据一些实施例,形成粘着层190于线路基板160之上,如图1C和1C-1所示。根据一些实施例,粘着层190具有沟槽192和开口194。根据一些实施例,装置180位于沟槽192中。根据一些实施例,封装体P位于开口194中。

根据一些实施例,沟槽192围绕开口194。根据一些实施例,开口194具有内壁194a。根据一些实施例,内壁194a具有凹陷194b。根据一些实施例,每一个凹陷194b与对应的沟槽192连通。根据一些实施例,间隙G1朝向凹陷194b延伸。根据一些实施例,粘着层190由聚合物材料形成,例如环氧树脂(epoxy)或硅树脂(silicone)。

图1D-1是根据一些实施例的图1D的芯片封装结构的上视示意图。图1D-2是根据一些实施例之图1D的芯片封装结构的透视示意图。为了简洁,图1D-2省略底部填充层170。

根据一些实施例,设置环形结构210于粘着层190之上,如图1D、图1D-1和图1D-2所示。图1D-3是根据一些实施例的图1D的芯片封装结构的环形结构210的上视示意图。根据一些实施例,环形结构210具有沟槽212和开口214,如图1D、图1D-1、图1D-2和图1D-3所示。根据一些实施例,沟槽212围绕开口214。

根据一些实施例,沟槽212具有大致长方形形状。根据一些实施例,开口214具有大致长方形形状。根据一些实施例,沟槽212分别相邻于开口214的四个内壁214a。根据一些实施例,装置180位于沟槽212中。根据一些实施例,使用铣削(milling)制程或线切割制程,形成沟槽212和开口214。

根据一些实施例,粘着层190的开口194位于开口214下方,如图1D、图1D-1和图1D-2所示。根据一些实施例,封装体P位于开口214中。这些内壁214a中的两个具有凹陷214b。根据一些实施例,每一个凹陷214b与对应的沟槽212和开口214连通。根据一些实施例,凹陷214b具有大致长方形形状。

根据一些实施例,间隙G1朝向凹陷214b延伸。根据一些实施例,粘着层190的凹陷194b位于凹陷214b下方。根据一些实施例,凹陷214b和194b具有大致相同宽度W1。

根据一些实施例,环形结构210具有外环216和条状部分215、217、218和219。根据一些实施例,条状部分215、217、218和219也称为肋(rib)。根据一些实施例,条状部分215、217、218和219被外环216围绕。

根据一些实施例,条状部分215具有大致长方形形状。根据一些实施例,条状部分215具有连接至外环216的相对两端215a。根据一些实施例,凹陷214b位于条状部分215中。根据一些实施例,凹陷214b通过条状部分215。

根据一些实施例,条状部分217具有大致长方形形状。根据一些实施例,条状部分217具有连接至外环216的相对两端217a。根据一些实施例,凹陷214b位于条状部分217中。根据一些实施例,凹陷214b通过条状部分217。

根据一些实施例,条状部分218具有大致长方形形状。根据一些实施例,条状部分218介于条状部分215和条状部分217之间。根据一些实施例,条状部分218连接至条状部分215和条状部分217。

根据一些实施例,条状部分219具有大致长方形形状。根据一些实施例,条状部分219介于条状部分215和条状部分217之间。根据一些实施例,条状部分219连接至条状部分215和条状部分217。因此,根据一些实施例,条状部分218、215和217共同形成第一I形结构,并且条状部分219、215和217共同形成第二I形结构。根据一些实施例,这两个I形结构设置于封装体P的相对两侧。

在一些实施例中,芯片结构122与条状部分215之间的距离D1范围在约7厘米(mm)至约20mm。根据一些实施例,如果距离D1小于约7mm,芯片角落处的应力较大,这是不期望的。根据一些实施例,如果距离D1大于约20mm,环形结构210的尺寸较大,这占据线路基板160太多表面区域。

在一些实施例中,芯片结构122与条状部分218之间的距离D2范围在约7mm至约20mm。根据一些实施例,如果距离D2小于约7mm,芯片角落处的应力较大,这是不期望的。根据一些实施例,如果距离D2大于约20mm,环形结构210的尺寸较大,这占据线路基板160太多表面区域。

根据一些实施例,芯片结构122具有宽度W122。根据一些实施例,每一个芯片结构122具有面向间隙G1的侧壁122a。在一些实施例中,横向距离D3介于侧壁122a与凹陷214b的内壁214b1之间。在一些实施例中,横向距离D3对宽度W122的比值范围在约0.3至约0.7。根据一些实施例,比值(D3/W122)范围在约0.5至约0.7。在一些实施例中,侧壁122a之间的距离D4范围在约40纳米(nm)至约120nm。

根据一些实施例,环形结构210由刚性材料形成,例如金属(例如,铜或铁)、前述的合金(例如,不锈钢)、或是比线路基板160硬的其他适合材料。

图1E-1是根据一些实施例的图1E的芯片封装结构的上视示意图。图1E-2是根据一些实施例的图1E的芯片封装结构的透视示意图。为了简洁,图1E-2省略底部填充层170和粘着层A。

根据一些实施例,分别设置盖件(lid)220于芯片结构122之上,如图1E、图1E-1和图1E-2所示。根据一些实施例,在此步骤中,基本上形成芯片封装结构100。根据一些实施例,盖件220比下方的芯片结构122窄。也就是说,根据一些实施例,盖件220的宽度W220小于芯片结构122的宽度W122。

根据一些实施例,盖件220由高热导性材料形成,例如金属材料(例如,铝或铜)、合金材料(例如,不锈钢)、或碳化铝硅(aluminum-silicon carbide,AlSiC)。

在一些实施例中,形成粘着层A于盖件220与芯片结构122之间,如图1E所示。根据一些实施例,粘着层A由导电聚合物与金属(例如,银胶)或聚合物(例如,例如环氧树脂(epoxy)或硅树脂(silicone)形成。为了简洁,图1E-2省略底部填充层170和粘着层A。

根据一些实施例,当使用环状结构来降低线路基板160的翘曲(warpage)时,应力容易集中在间隙G1中的底部填充层130。根据一些实施例,应力容易在间隙G1中的底部填充层130中引起裂痕(crack)或脱层(delamination)。因此,根据一些实施例,本公开实施例的方法移除环形结构210靠近间隙G1的部分,以降低环形结构210靠近间隙G1的抗翘曲能力。如此,根据一些实施例,集中于间隙G1中的底部填充层130的应力得以降低。根据一些实施例,因为本公开实施例的方法仅移除环形结构210靠近间隙G1的部分,整个环形结构210的抗翘曲能力大致维持在可接受的范围内。根据一些实施例,因此改善芯片封装结构100的良率。

根据一些实施例,盖件220能降低芯片结构122的翘曲,这可降低线路基板160的翘曲。根据一些实施例,因此改善芯片封装结构100。

在一些实施例中,粘着层190的侧壁196对准于或与环形结构210的侧壁213共平面。在其他一些实施例中,粘着层190的侧壁196从环形结构210的侧壁213凹入,如图9所示。在另一些实施例中,粘着层190的侧壁196从环形结构210的侧壁213突出,如图10所示。

图2A是根据一些实施例,显示芯片封装结构200。图2B是根据一些实施例,显示图2A的芯片封装结构200的上视示意图。图2C是根据一些实施例,显示图2A的芯片封装结构200的透视示意图。为了简洁,图2C省略底部填充层170和粘着层A。

图2D是根据一些实施例,显示图2A的环形结构210的透视示意图。根据一些实施例,图2D是由环形结构210的底面211观察。图2E是根据一些实施例,显示图2A的芯片封装结构200但没有环形结构210的上视示意图

根据一些实施例,芯片封装结构200相似于图1E的芯片封装结构100,除了环形结构210具有较低部分210A和较上部分210B,且两者具有不同结构,如图2A、图2B、图2C、图2D和图2E所示。根据一些实施例,环形结构210具有开口214。根据一些实施例,封装体P位于开口214中。

根据一些实施例,较下部分210A的结构与图1E的环形结构210相似。根据一些实施例,较下部分210A具有沟槽212A和凹陷214A,如第2B和2D图所示。根据一些实施例,沟槽212A围绕开口214。根据一些实施例,每一个凹陷214A与对应的沟槽212A和开口214连通。根据一些实施例,装置180位于沟槽212A中,如图2A所示。

根据一些实施例,较上部分210B是一块连续的板子,其位于较下部分210A之上并且覆盖沟槽212A和凹陷214A,如图2A、图2B和图2D所示。根据一些实施例,较上部分210B比较下部分210A薄。

根据一些实施例,环形结构210包含较薄部分216A和216C和较厚部分216B和216D,如图2A、图2B和图2D所示。根据一些实施例,较薄部分216A相对于较薄部分216C。根据一些实施例,较薄部分216A连接于较厚部分216B和216D之间。根据一些实施例,较薄部分216C连接于较厚部分216B和216D之间。

根据一些实施例,芯片结构122之间的间隙G1朝向较薄部分216A和216C延伸,如图2B、图2C所示。根据一些实施例,间隙G1靠近较薄部分216A和216C。根据一些实施例,较薄部分216A的顶面216a与较厚部分216B的顶面216b大致共平面,如图2C所示。

图3A是根据一些实施例之芯片封装结构300的透视示意图。图3B是根据一些实施例,显示图3A的芯片封装结构300但没有环形结构210的上视示意图。为了简洁,图3A省略底部填充层170和粘着层A。

根据一些实施例,芯片封装结构300相似于图2C和图2E的芯片封装结构200,除了图3A和图3B的粘着层190的凹陷194b比图2C和图2E的粘着层190的凹陷194b宽,如图3A和图3B所示。

根据一些实施例,凹陷194b比较下部分210A的凹陷214A宽,如图3A和图3B所示。因此,根据一些实施例,较下部分210A的部分211A未通过粘着层190接合到线路基板160。根据一些实施例,在部分211A与线路基板160之间有间隙G2。

图4A是根据一些实施例,显示芯片封装结构400的剖面示意图。图4B是根据一些实施例,显示图4A的芯片封装结构400的上视示意图。

图4C是根据一些实施例的图4A的芯片封装结构400的透视示意图。为了简洁,图4C省略底部填充层170和粘着层A。图4D是根据一些实施例,显示图4A的芯片封装结构400但没有环形结构210的上视示意图。图4E是根据一些实施例,显示图4A的环形结构210和粘着层190的展开示意图。

根据一些实施例,芯片封装结构400相似于图2A、图2B和图2C的芯片封装结构200,除了芯片封装结构400的环形结构210更具有位于较下部分210A与较上部分210B之间的粘着层410,如图4A、图4B和图4C所示。

根据一些实施例,粘着层410具有沟槽412和开口414,如图4D和图4E所示。根据一些实施例,装置180位于沟槽412中。根据一些实施例,沟槽412围绕开口414。根据一些实施例,开口414具有内壁414a。

根据一些实施例,内壁414a具有凹陷414b。根据一些实施例,每一个凹陷414b连通对应的沟槽412。根据一些实施例,间隙G1朝向凹陷414b延伸。根据一些实施例,粘着层410由聚合物材料形成,例如环氧树脂(epoxy)或硅树脂(silicone)。

图5是根据一些实施例,显示芯片封装结构500的上视示意图。根据一些实施例,芯片封装结构500相似于图1E-1的芯片封装结构100,除了芯片封装结构500的环形结构510没有图1E-1的芯片封装结构100的沟槽212,如图5所示。

根据一些实施例,环形结构510具有开口512。根据一些实施例,开口512具有内壁512a。根据一些实施例,内壁512a具有凹陷512b。根据一些实施例,凹陷512b彼此相对。根据一些实施例,芯片结构122之间的间隙G1朝向凹陷512b延伸。

根据一些实施例,环形结构510具有较窄部分510A和较宽部分510B。根据一些实施例,较窄部分510A的线宽W510A少于较宽部分510B的线宽W510B。根据一些实施例,芯片结构122之间的间隙G1朝向较窄部分510A延伸。

图6是根据一些实施例,显示芯片封装结构600的上视示意图。根据一些实施例,芯片封装结构600相似于图5的芯片封装结构500,除了芯片封装结构600的环形结构610被间隙616分割为部分612和614,如图6所示。根据一些实施例,部分612和614彼此隔开。根据一些实施例,间隙G1朝向间隙616延伸。

图7是根据一些实施例,显示芯片封装结构700的上视示意图。根据一些实施例,芯片封装结构700相似于图1E-1的芯片封装结构100,除了凹陷194b没有穿过条状部分215和217,如图7所示。

图8是根据一些实施例,显示芯片封装结构800的上视示意图。根据一些实施例,芯片封装结构800相似于图1E-1的芯片封装结构100,除了凹陷194b更延伸至外环216中,如图8所示。

用于形成芯片封装结构200、300、400、500、600、700和800制程和材料可相似于或同等于用于形成芯片封装结构100的制程和材料。

根据一些实施例,提供芯片封装结构及其形成方法。形成芯片封装结构的方法移除抗翘曲环形结构靠近芯片结构间的间隙处的一部分,以降低环形结构在靠近芯片结构间的间隙处的抗翘曲能力。由此,集中在底部填充层的应力得以降低。因为此方法仅移除环形结构靠近间隙的部分,所以整个环形结构的抗翘曲能力大致维持在可接受的范围。因此,改善芯片封装结构的良率。

此方法设置盖件于芯片结构之上,以降低芯片结构的翘曲,这降低承载芯片结构的线路基板的翘曲。因此,改善芯片封装结构的良率。

在一些实施例中,提供芯片封装结构的形成方法。此方法包含设置第一芯片结构和第二芯片结构于线路基板之上。第一芯片结构与第二芯片相隔一间隙。此方法还包含设置环形结构于线路基板之上。环形结构具有第一开口,第一芯片结构和第二芯片结构位于第一开口中,第一开口具有第一内壁,第一内壁具有第一凹陷,且间隙朝向第一凹陷延伸。在一些实施例中,设置第一芯片结构和第二芯片结构于线路基板之上的步骤包含设置封装体于线路基板之上。封装体包含重布线结构、以及位于重布线结构之上的第一芯片结构、第二芯片结构和底部填充层。底部填充层位于间隙中、介于第一芯片结构与重布线结构之间、且介于第二芯片结构与重布线结构之间。在一些实施例中,此方法还包含在设置环形结构于线路基板之上之前,形成粘着层于线路基板之上。芯片结构位于粘着层之上。在一些实施例中,粘着层具有在第一开口下方的第二开口,第二开口具有第二内壁,且第二内壁具有在第一凹陷下方的第二凹陷。在一些实施例中,第一凹陷和第二凹陷具有大致相同的宽度。在一些实施例中,第二凹陷比第一凹陷宽。在一些实施例中,环形结构具有较上部分和较下部分,且第一凹陷位于较下部分中。在一些实施例中,环形结构还包含介于较上部分与较下部分之间的粘着层。在一些实施例中,此方法还包含设置盖件于第一芯片结构之上。在一些实施例中,盖件比第一芯片结构窄。

在一些实施例中,提供芯片封装结构的形成方法。此方法包含设置第一芯片结构和第二芯片结构于线路基板之上。第一芯片结构与第二芯片结构相隔一间隙。此方法还包含设置环形结构于线路基板之上。环形结构围绕第一芯片结构和第二芯片结构,环形结构包含彼此连接的第一较薄部分和第一较厚部分,且间隙靠近第一较薄部分。在一些实施例中,环形结构包含第二较薄部分和第二较厚部分,第一较薄部分介于第一较厚部分和第二较厚部分之间且连接至第一较厚部分和第二较厚部分,并且第二较薄部分介于第一较厚部分和第二较厚部分之间且连接至第一较厚部分和第二较厚部分。在一些实施例中,间隙靠近第二较薄部分。在一些实施例中,第一较薄部分相对于第二较薄部分。在一些实施例中,第一较薄部分的第一顶面与第一较厚部分的第二顶面大致共平面。

在一些实施例中,提供芯片封装结构。此芯片封装结构包含线路基板。此芯片封装结构包含位于线路基板之上的第一芯片结构和第二芯片结构。第一芯片结构与第二芯片结构相隔一间隙。此芯片封装结构包含位于线路基板之上的环形结构。线路基板具有开口,第一芯片结构和第二芯片结构位于开口中,开口具有内壁,内壁具有凹陷,且间隙朝向凹陷延伸。在一些实施例中,环形结构具有外环和围绕外环的第一条状部分,第一条状部分具有连接至外环的第一端和第二端,且凹陷位于第一条状部分中。在一些实施例中,凹陷穿过第一条状部分。在一些实施例中,环形结构具有较上部分和较下部分,且凹陷位于较下部分中。在一些实施例中,环形结构还包含介于较上部分与较下部分之间的粘着层。

以上概述数个实施例的部件,以便在本公开所属技术领域中具有通常知识者可以更加理解本公开实施例的观点。在本公开所属技术领域中具有通常知识者应理解,他们能轻易地以本公开实施例为基础,设计或修改其他制程和结构,以达到与在此介绍的实施例相同的目的及/或优势。在本公开所属技术领域中具有通常知识者也应理解,此类等效的结构并无悖离本公开的精神与范围,且他们能在不违背本公开之精神和范围下,做各式各样的改变、取代和替换。因此,本公开之保护范围当视后附的权利要求所界定为准。

- 芯片封装结构及芯片封装结构及其形成方法

- 非导电膜及其形成方法、芯片封装结构及方法