一种CMOS超宽带低噪声放大器

文献发布时间:2023-06-19 11:52:33

技术领域

本发明涉及集成电路设计技术领域,具体涉及一种CMOS超宽带低噪声放大器。

背景技术

随着无线技术的飞速发展,移动通信技术的发展向着更高频、更宽带的方向发展,各种无线标准(例如Bluetooth,Zigbee,WLAN,WiFi,UWB,GPS和2G/3G/4G/5G蜂窝电话)的使用一直在不断增加。然而频谱资源是有限的,为了满足人们对更高速、更大容量的通信需求,能够兼容多个通信标准的超宽带通信技术逐渐成为重要的研究方向。

超宽带低噪声放大电路是超宽带接收机的核心电路模块,作为超宽带接收链路的第一级放大电路,根据噪声级联公式,超宽带低噪声放大器的噪声基本决定接收链路的整体噪声;此外,超宽带低噪声放大器还有增益、匹配、功耗、带宽及线性度等指标要求,而且这些指标存在着相互折中的关系,低噪声放大器电路设计需要根据应用要求规划相应的指标。

常用的宽带低噪声放大器结构包括分布式结构、电阻并联反馈结构、共栅放大器结构和源极电感退化结构。分布式放大器结构采用多级放大结构,利用延迟传输线来实现宽带,且需要较大功耗,不适于集成和低功耗应用。在电阻并联反馈结构中,并联反馈电阻连接于晶体管的栅极和漏极,使输入阻抗的Q值降低,能够实现宽带的输入匹配,但该结构由于反馈电阻的引入会使噪声性能变差。在共栅放大器结构中,输入阻抗近似为1/gm,由于共栅结构的输入阻抗为常数,因此具有其它结构无可比拟的宽带匹配性能,且不存在反馈电容,具有较好的隔离性、稳定性、较高的线性度和低功耗等特点,但该结构噪声系数较高,需要采取其它途径来降低噪声。在源级电感退化结构中通过调节源极电感和栅源电容Cgs来实现噪声和输入匹配,但这种方法只能满足一定频率范围,为了拓展该结构在频带内噪声和匹配的优良特性,常采用加入额外的电感、电容元件共同构成带通滤波器来实现宽带的匹配,通过该方法能够在很宽的频带内实现良好的输入匹配、噪声性能,然而过多的电感和电容使用,导致面积较大。

发明内容

本发明解决的是背景技术中所存在的超宽频带、低噪声、低功耗等方面问题,提供一种CMOS超宽带低噪声放大器。

为解决上述问题,本发明通过以下技术方案实现:

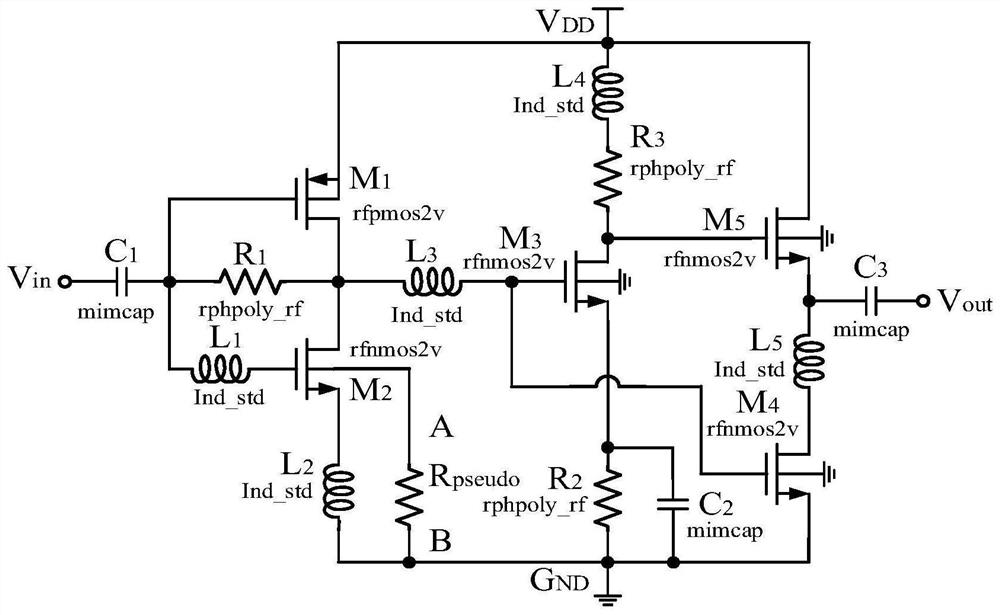

一种CMOS超宽带低噪声放大器,包括输入级互补共源电路、中间级共源负反馈电路和输出级共源buffer电路。

输入级互补共源电路包括PMOS晶体管M1,NMOS晶体管M2,耦合电容C1,反馈电阻R1,峰化电感L1,源极退化电感L2,峰化电感L3和伪电阻R

中间级共源负反馈电路包括NMOS晶体管M3-M4,并联峰化电感L4,负反馈电阻R2,负载电阻R3和电容C2;NMOS晶体管M3漏极通过串联的负载电阻R3和并联峰化电感L4与电源VDD相连;NMOS晶体管M3的栅极通过峰化电感L3与PMOS晶体管M1的漏极相连;NMOS晶体管M3的源极通过并联的负反馈电阻R2和电容C2接地;NMOS管M3的衬底接地;NMOS晶体管M4的栅极与NMOS晶体管M3的栅极相连;NMOS晶体管M4的源极和衬底接地。

输出级共源buffer电路包括NMOS晶体管M5,耦合电容C3和电感L5;NMOS晶体管M5的漏极与电源VDD相连;NMOS晶体管M5的栅极与NMOS晶体管M3的漏极相连;NMOS晶体管M5的源极通过耦合电容C3与输出端Vout相连、以及通过电感L5与NMOS晶体管M4的漏极相连;NMOS晶体管M5的衬底接地。

上述方案中,伪电阻R

与现有技术相比,本发明具有如下特点:

1、本发明创新性地在互补共源级基础上引入电阻反馈,电感峰化技术、源极退化电感技术和伪电阻结构,同时结合共源负反馈电路,共源buffer电路和电流复用技术,使得整体电路具有宽带宽的同时、达到良好的增益、噪声系数和功耗等指标。

2、本发明超宽带低噪声放大器所引入的伪电阻结构,能有效地减少电路的噪声系数。

3、本发明能够工作在0.15~11GHz频带内,覆盖了5G中低频段范围(450MHz~6GHz)以及IMT业务在6GHz候选频段(5925~7125MHz)范围,同时也兼容UWB标准频段(3.1~10.6GHz)。

附图说明

图1为一种CMOS超宽带低噪声放大器的电路图;

图2为一种CMOS超宽带低噪声放大器中所用伪电阻电路图;

图3为一种CMOS超宽带低噪声放大器的S参数仿真结果;

图4为一种CMOS超宽带低噪声放大器的噪声仿真结果;

图5为一种CMOS超宽带低噪声放大器的稳定性仿真结果。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚,下面结合实施方式和附图,对本发明做进一步地详细描述。

一种CMOS超宽带低噪声放大器,如图1所示,采用单端输入输出结构,并由输入级互补共源电路、中间级共源负反馈电路和输出级共源buffer电路组成。输入级互补共源电路与中间级共源负反馈电路连接,中间级共源负反馈电路的输出端与输出级共源buffer电路连接。

所述输入级互补共源电路包括PMOS晶体管M1,NMOS晶体管M2,输入耦合电容C1,反馈电阻R1,峰化电感L1,源极退化电感L2,峰化电感L3和伪电阻R

所述中间级共源负反馈电路包括NMOS晶体管M3-M4,并联峰化电感L4,负反馈电阻R2,负载电阻R3和电容C2。NMOS晶体管M3漏极通过串联的负载电阻R3和并联峰化电感L4与电源VDD相连。NMOS晶体管M3的栅极通过峰化电感L3与PMOS晶体管M1的漏极相连。NMOS晶体管M3的源极通过并联的负反馈电阻R2和电容C2接地。NMOS管M3的衬底接地。NMOS晶体管M4的栅极与NMOS晶体管M3的栅极相连。NMOS晶体管M4的源极和衬底接地。中间级中的信号通过两个路径,包括上方路径M3和M5和下方路径M4。第一级的输出寄生电容和第二级的输入寄生电容与引入电感L3构成π型匹配网络,可实现级间匹配。电感L4和电阻R3构成并联峰化结构,用于扩展电路的带宽,源极负反馈结构由电阻R2和电容C2组成,用于扩展电路的带宽和稳定电路。M4为辅助放大级,用于增加中间级的增益。

所述输出级共源buffer电路包括NMOS晶体管M5,输出耦合电容C3和电感L5。NMOS晶体管M5的漏极与电源VDD相连。NMOS晶体管M5的栅极与NMOS晶体管M3的漏极相连。NMOS晶体管M5的源极通过输出耦合电容C3与输出端Vout相连、以及通过电感L5与NMOS晶体管M4的漏极相连。NMOS晶体管M5的衬底接地。输出耦合电容C3起到隔离直流分量的作用。输出级共源buffer电路用于实现宽带输出匹配。

本实施例采用TSMC 0.18um RF CMOS工艺实现CMOS超宽带低噪声放大器。图3给出了本实施例的S参数仿真结果,从图中可以看出,本CMOS超宽带低噪声放大器的3dB带宽达到11.9GHz。在0.15~11GHz频带范围内增益为13.8~14.5dB,带内增益平坦性良好,S11和S22均小于-10dB,达到良好的输入输出匹配效果,S12小于-25dB达到较好的反向隔离效果。图4给出了本实施例的噪声仿真结果,从图中可以看出,本CMOS超宽带低噪声放大器在0.15~11GHz频率范围噪声系数为≤3dB,并给出引入伪电阻前后的噪声对比,从图中可以看出,引入伪电阻后电路的噪声系数明显优化了,经计算,电路的平均噪声优化了0.37dB,优化效果达到13%。图5给出了本实施例的稳定性仿真结果,从图中可以看出,本CMOS超宽带低噪声放大器在0.15~11GHz频率范围稳定系数大于1。在供电电压为1.5V情况下,电路整体功耗为6.4mW。综上所述,在TSMC 0.18um RF CMOS工艺下,本发明可实现0.15~11GHz的工作带宽,S11和S22均小于-10dB,增益为13.8~14.5dB,噪声系数2.7~3dB,功耗为6.4mW,这些仿真结果说明了本发明的有效性。

本发明所提出的CMOS超宽带低噪声放大器,采用电流复用结构,输入级在互补共源级的基础上引入电阻反馈、电感峰化技术、源极退化电感技术和伪电阻结构,可拓展电路带宽并提高电路的增益及降低电路噪声。中间级以带源极负反馈的共源级为基础引入增益辅助级和并联电感峰化技术,可拓展电路带宽并增加电路增益。输出级采用共源buffer电路,可实现宽带的输出匹配。

需要说明的是,尽管以上本发明所述的实施例是说明性的,但这并非是对本发明的限制,因此本发明并不局限于上述具体实施方式中。在不脱离本发明原理的情况下,凡是本领域技术人员在本发明的启示下获得的其它实施方式,均视为在本发明的保护之内。

- 一种超宽带CMOS低噪声放大器自动化设计方法及CMOS LNA设备

- 一种CMOS超宽带低噪声放大器