基于RISC-V的控制方法、系统、芯片及存储介质

文献发布时间:2023-06-19 19:27:02

技术领域

本发明涉及芯片控制技术领域,尤其涉及一种基于RISC-V的控制方法、系统、芯片及存储介质。

背景技术

随着芯片技术的不断发展,芯片在各个领域的使用也越来越频繁,基于现有对控制效率的追求,因而也对于芯片的输入输出的控制提出了更高的要求。

传统的芯片输入输出的控制方式是GPIO(General-purpose input/output,输入/输出端口)作为从设备,以内存映射的方式连接到SoC(System on Chip,系统级芯片)总线上;芯片内部的处理器作为主设备连接到SoC总线上;处理器通过发出内存读写指令控制GPIO模块中的控制寄存器,从而控制/读取芯片IO(input/output,输入/输出)管脚的电平,这种芯片输入输出的控制方式存在很大的缺陷,存在芯片处理器发出的内存读写指令需要经过总线逻辑之后才能到达GPIO的问题,即这种芯片输入输出的控制方式会由于读写指令需要经过总线逻辑之后才能实现输入/输出进而造成芯片输入输出的控制效率不高。

发明内容

本发明的主要目的在于提出一种基于RISC-V的控制方法、系统、芯片及存储介质,旨在提高芯片输入输出的控制效率。

为实现上述目的,本发明提供一种基于RISC-V的控制方法,所述基于RISC-V的控制方法应用于基于RISC-V的控制系统,所述基于RISC-V的控制系统包括指令解码单元、开源指令集RISC-V处理器和输入输出端口GPIO所述基于RISC-V的控制方法包括以下步骤:

通过指令解码单元获取RISC-V处理器读入的控制指令,并确定所述控制指令对应的解码指令;

根据所述解码指令和预存的历史切换信息确定方向切换信息;

确定所述方向切换信息对应的目标处理单元,通过所述目标处理单元根据所述解码指令对GPIO进行控制。

可选地,根据所述解码指令和预存的历史切换信息确定方向切换信息的步骤,包括:

确定所述解码指令对应的指令特征,检测所述指令特征是否与预设的方向切换指令特征匹配;

若所述指令特征与预设的方向切换指令特征不匹配,则确定预存的历史切换信息对应的传输方向,并将所述传输方向作为方向切换信息。

可选地,检测所述指令特征是否与预设的方向切换指令特征匹配的步骤之后,包括:

若所述指令特征与预设的方向切换指令特征匹配,则确定所述解码指令对应的方向指令;

通过方向切换单元根据所述方向指令控制GPIO进行方向切换,并基于方向切换后的GPIO执行所述通过指令解码单元获取RISC-V处理器读入的控制指令的步骤。

可选地,所述基于RISC-V的控制系统包括输入处理单元和输出处理单元,确定所述方向切换信息对应的目标处理单元的步骤,包括:

确定所述方向切换信息中的传输方向,检测所述传输方向是否与预设的输入方向匹配;

若所述传输方向与预设的输入方向匹配,则确定所述目标处理单元为输入处理单元;

若所述传输方向与预设的输入方向不匹配,则确定所述目标处理单元为输出处理单元。

可选地,通过所述目标处理单元根据所述解码指令对GPIO进行控制的步骤,包括:

若所述目标处理单元为输入处理单元,则确定所述解码指令对应的电平返回要求;

基于所述电平返回要求确定GPIO输入的原始电平对应的输入值,且/或确定所述解码指令对应的指令运算,基于所述指令运算确定所述原始电平与预设源操作数对应的返回值。

可选地,通过所述目标处理单元根据所述解码指令对GPIO进行控制的步骤,还包括:

若所述目标处理单元为输出处理单元,则确定所述解码指令中的输出数值指令;

基于所述输出数值指令和所述解码指令确定GPIO输出对应的输出值。

可选地,基于所述输出数值指令和所述解码指令确定GPIO输出对应的输出值的步骤,包括:

确定所述输出数值指令对应的第一源操作数值和第二源操作数值,并确定所述解码指令中的数值操作指令;

基于所述数值操作指令对所述第一源操作数值和所述第二源操作数值进行指令操作确定GPIO输出的输出值。

此外,为实现上述目的,本发明还提供一种基于RISC-V的控制系统,基于RISC-V的控制系统包括:

读入解码模块,用于通过指令解码单元获取RISC-V处理器读入的控制指令,并确定所述控制指令对应的解码指令;

方向切换模块,用于根据所述解码指令和预存的历史切换信息确定方向切换信息;

指令处理模块,用于确定所述方向切换信息对应的目标处理单元,通过所述目标处理单元根据所述解码指令对GPIO进行控制。

此外,为实现上述目的,本发明还提供一种基于RISC-V的控制芯片,包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的基于RISC-V的控制程序,所述基于RISC-V的控制程序被所述处理器执行时实现上所述的基于RISC-V的控制方法的步骤。

此外,为实现上述目的,本发明还提供一种基于RISC-V的控制存储介质,所述存储介质上存储有基于RISC-V的控制程序,所述基于RISC-V的控制程序被处理器执行时实现如上所述的基于RISC-V的控制方法的步骤。

本发明公开了一种基于RISC-V的控制方法,该方法包括通过指令解码单元获取RISC-V处理器读入的控制指令,并确定所述控制指令对应的解码指令;根据所述解码指令和预存的历史切换信息确定方向切换信息;确定所述方向切换信息对应的目标处理单元,通过所述目标处理单元根据所述解码指令对GPIO进行控制。通过指令解码单元获取RISC-V处理器读入的控制指令,进而实现对控制指令解码之后,确定方向切换信息对应的目标处理单元,进而通过目标处理单元根据解码指令对GPIO进行控制,以实现GPIO输入输出的控制。

从而,本发明避免了现有技术中芯片处理器发出的内存读写指令需要经过总线逻辑之后才能到达GPIO的现象发生,这种基于RISC-V的控制方法不仅通过RISC-V处理器读入的控制指令进而可以保证控制指令的开源性,增加了用户使用的指令修改与扩展功能,而且还通过目标处理单元根据解码指令对GPIO进行控制,进而提高了芯片输入输出的控制效率。

附图说明

图1是本发明实施例方案涉及的硬件运行环境的基于RISC-V的控制芯片结构示意图;

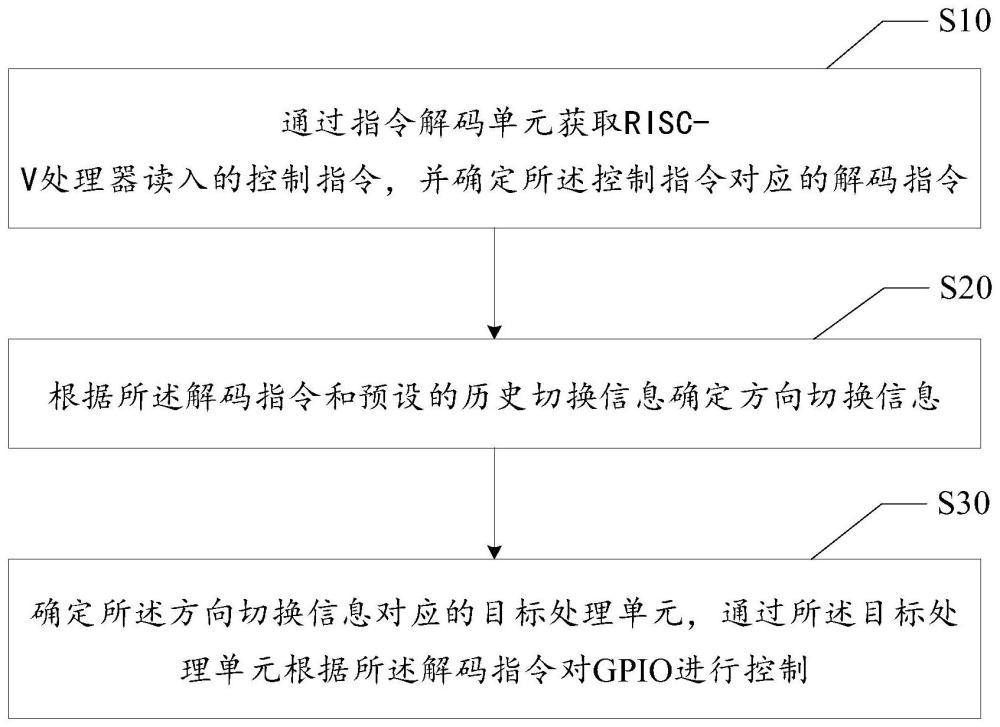

图2为本发明基于RISC-V的控制方法的流程示意图;

图3为本发明基于RISC-V的控制系统的结构示意图;

图4为本发明基于RISC-V的控制系统一实施例的示意图;

图5为现有GPIO控制结构示意图;

图6为基于RISC-V的控制系统模块示意图。

附图标号说明:

本发明目的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

参照图1,图1为本发明实施例方案涉及的硬件运行环境的基于RISC-V的控制芯片结构示意图。

如图1所示,该基于RISC-V的控制芯片可以包括:处理器0003,例如中央处理器(Central Processing Unit,CPU),通信总线0001、获取接口0002,处理接口0004,存储器0005。其中,通信总线0001用于实现这些组件之间的连接通信。获取接口0002可以包括信息采集装置、获取单元比如计算机,可选获取接口0002还可以包括标准的有线接口、无线接口。处理接口0004可选的可以包括标准的有线接口、无线接口。存储器0005可以是高速的随机存取存储器(Random Access Memory,RAM),也可以是稳定的非易失性存储器(Non-Volatile Memory,NVM),例如磁盘存储器。存储器0005可选的还可以是独立于前述处理器0003的存储装置。

本领域技术人员可以理解,图1中示出的结构并不构成对基于RISC-V的控制芯片的限定,可以包括比图示更多或更少的部件,或者组合某些部件,或者不同的部件布置。

如图1所示,作为一种存储介质的存储器0005中可以包括操作系统、获取接口模块、处理接口模块以及基于RISC-V的控制程序。

在图1所示的基于RISC-V的控制芯片中,通信总线0001主要用于实现组件之间的连接通信;获取接口0002主要用于连接后台服务器,与后台服务器进行数据通信;处理接口0004主要用于连接部署端(用户端),与部署端进行数据通信;本发明基于RISC-V的控制芯片中的处理器0003、存储器0005可以设置在基于RISC-V的控制芯片中,所述基于RISC-V的控制芯片通过处理器0003调用存储器0005中存储的基于RISC-V的控制程序,并执行本发明实施例提供的基于RISC-V的控制系统。

基于上述硬件结构,提出本发明基于RISC-V的控制方法实施例。

提出本发明基于RISC-V的控制方法的第一实施例,参照图2,图2为基于RISC-V的控制方法的流程示意图,基于RISC-V的控制方法包括:

步骤S10,通过指令解码单元获取RISC-V处理器读入的控制指令,并确定所述控制指令对应的解码指令;

在本实施例中,当RISC-V处理器根据用户输入的指令信息或者存储器内部的指令读入控制指令之后,就会通过指令解码单元获取RISC-V处理器读入的控制指令,并确定控制指令对应的解码指令。指令信息是指用户自定义输入的指令,会根据该指令在RISC-V处理器读入得到对应的控制指令。在得到控制指令之后,就会在指令解码单元进行解码得到解码指令,最终可以根据解码指令的内部指令特征将解码指令发送至对应的处理单元,进而可以保证处理指令的准确性。

步骤S20,根据所述解码指令和预存的历史切换信息确定方向切换信息;

在本实施例中,在得到解码指令之后,就会根据解码指令和预存的历史切换信息确定方向切换信息,预存的历史切换信息是指上一解码指令对应的方向信息,例如上一解码指令对应的方向信息是输出方向,则就会将输出方向作为预存的历史切换信息,方向切换信息是指切换GPIO的输入输出方向的切换信息。其中,根据所述解码指令和预存的历史切换信息确定方向切换信息的步骤,包括:

步骤A10,确定所述解码指令对应的指令特征,检测所述指令特征是否与预设的方向切换指令特征匹配;

在本实施例中,在确定方向切换信息时需要确定解码指令对应的指令特征,同时检测指令特征是否与预设的方向切换指令特征匹配,是因为解码指令存在至少三种情况,一种是切换方向的解码指令,一种是输入控制的解码指令,一种是输出控制的解码指令,指令特征是指经由指令解码单元进行解码得到解码指令的控制的特征,预设的方向切换指令特征是指方向切换指令的指令特征,通过检测指令特征是否与预设的方向切换指令特征匹配,进而可以确定解码指令是否为方向切换指令。其中,检测所述指令特征是否与预设的方向切换指令特征匹配的步骤之后,包括:

步骤B10,若所述指令特征与预设的方向切换指令特征匹配,则确定所述解码指令对应的方向指令;

步骤B20,通过方向切换单元根据所述方向指令控制GPIO进行方向切换,并基于方向切换后的GPIO执行所述通过指令解码单元获取RISC-V处理器读入的控制指令的步骤。

在本实施例中,当指令特征与预设的方向切换指令特征匹配,就会确定解码指令对应的方向指令,也就是确定解码指令是方向切换指令,方向指令是指切换GPIO输入或者输出方向的指令。例如,Io.set rs1=1,rd,定义为根据rs1的值为1切换GPIO输入方向;Io.set rs1=0,rd,定义为根据rs1的值为0切换GPIO输出方向,当执行将GPIO输出/输入方向后就会返回rd显示已经执行成功,rd的返回执行成功值可以用户进行自定义,也可以设置为默认值。当解码指令确定rs1的值之后,就会确定该值对应的指令特征,进而根据该值的指令特征确定是否为输入或者输出方向切换,也就是说实际是确定解码指令中的Io.setrs1=1,进而确定是否为方向切换指令特征,进而根据rs1的值确定是输入或者输出方向的切换指令。确定方向切换指令之后,就会将该解码指令发送至对应的方向切换单元,方向切换单元根据方向指令控制GPIO进行方向切换,同时还会将该方向指令作为预存的历史切换信息,并在切换之后的GPIO执行所述通过指令解码单元获取RISC-V处理器读入的控制指令的步骤,也就是说切换GPIO方向之后,会继续执行过指令解码单元获取RISC-V处理器读入的控制指令的步骤进而实现GPIO的输入输出控制,进一步的可以提高GPIO的输入输出控制的效率,不需要经过总线进行总线逻辑以及协议的传输过程,可以大大节约整个GPIO的输入输出的效率。

步骤A20,若所述指令特征与预设的方向切换指令特征不匹配,则确定预存的历史切换信息对应的传输方向,并将所述传输方向作为方向切换信息。

在本实施例中,当确定指令特征与预设的方向切换指令特征不匹配时,就会确定预存的历史切换信息对应的传输方向,并将该传输方向作为方向切换信息,也就是说指令特征与预设的方向切换指令特征不匹配时,可以知道该解码指令为输入或者输出控制指令,通过确定预存的历史切换信息对应的传输方向,进而确定该解码指令对应的传输方向,传输方向是指输入或者输出方向。也就是根据上一次解码指令确定本次解码指令的传输方向,因为上一次解码指令与本次解码指令之间为出现方向切换的指令,故本次解码指令还需要继续上一次解码指令的传输方向,当输入或者输出控制指令的传输方向与历史切换信息对应的传输方向不同时,则会执行指令失败,rd返回一个失败值。还有一方面就是确定解码指令之后,通过确定解码指令的指令特征是否与预设的输入方向指令特征,若匹配,进而确定输入方向为方向切换信息;反之则确定输出方向为方向切换信息,例如解码指令是Io.out.raw rs1,rd时,确定解码指令中的指令特征为out,进而确定与预设的输出方向指令特征匹配,反之解码指令是Io.in.tail1 rd时,确定解码指令中的指令特征为in,进而确定与预设的输入方向指令特征匹配,预设的输入/输出方向指令特征是指解码指令中的关于输入/输出的控制指令特征。通过确定方向切换信息进而可以确定解码指令需要发送的目的地,进而通过的解码指令控制的准确率。

步骤S30,确定所述方向切换信息对应的目标处理单元,通过所述目标处理单元根据所述解码指令对GPIO进行控制。

在本实施例中,当确定方向切换信息之后,就会确定方向切换信息对应的目标处理单元,最终将解码指令发送值目标处理单元进行GPIO的控制,目标处理单元是指指令对应的处理单元,可以是方向切换单元、输入处理单元或者输出处理单元。其中,确定所述方向切换信息对应的目标处理单元的步骤,包括:

步骤C10,确定所述方向切换信息中的传输方向,检测所述传输方向是否与预设的输入方向匹配;

步骤C20,若所述传输方向与预设的输入方向匹配,则确定所述目标处理单元为输入处理单元;

步骤C30,若所述传输方向与预设的输入方向不匹配,则确定所述目标处理单元为输出处理单元。

在本实施例中,通过确定方向切换信息中的传输方向,进而对传输方向进行检测,检测传输方向是否与预设的输入方向匹配,当两者匹配时,就会确定目标处理单元为输入处理单元,并将解码指令发送至输入处理单元,通过输入处理单元对GPIO进行控制,反之两者不匹配,则确定目标处理单元为输出处理单元,并将解码指令发送至输出处理单元,通过输出处理单元对GPIO进行控制。也可以是对传输方向是否与预设的输出方向匹配的检测,预设的输入/输出方向是指GPIO的输入/输出方向。其中,通过所述目标处理单元根据所述解码指令对GPIO进行控制的步骤,包括:

步骤D10,若所述目标处理单元为输入处理单元,则确定所述解码指令对应的电平返回要求;

步骤D20,基于所述电平返回要求确定GPIO输入的原始电平对应的输入值,且/或确定所述解码指令对应的指令运算,基于所述指令运算确定所述原始电平与预设源操作数对应的返回值。

在本实施例中,当目标处理单元为输入处理单元,就会确定解码指令对应的电平返回要求,进而根据电平返回要求确定GPIO输入的原始电平对应的输入值,且/或确定解码指令对应的指令运算,基于指令运算确定原始电平与预设源操作数对应的返回值,将返回值作为输入值,即:输入的原始电平值,可以执行一些运算(如计算前导0、计算1的个数,与源操作数rs2进行位运算等)之后再返回给RISC-V处理器,电平返回要求是指对输入电平的返回要求,原始电平是指GPIO输入的电平,输入值是指经过电平返回要求处理之后的原始电平对应的值。例如,解码指令为IO.in.raw/lead1/tail1/count1 rd,分别对应原始电平值作为输入值,原始电平值中的第一个比特1的位置的值作为输入值,原始电平值中的最后一个比特1的位置的值作为输入值,原始电平值中的比特1的个数作为输入值。也可以是定义源操作数作为输入值,通过确定解码指令对应的源操作数要求,基于所述源操作数要求确定GPIO输入的原始电平对应的输入值,源操作数要求是指对源操作数的返回要求,并非涉及输入的原始电平。例如,IO.in.bit rs1,rd是指确定rs1的指定比特位状态作为输入值,指定比特位可以将rs1=2,则确定第二位的比特位状态,通过解码指令对输入进行控制,不仅提高了控制多样性,而且还不同经过总线处理进而提高了输入的效率。

通过所述目标处理单元根据所述解码指令对GPIO进行控制的步骤,还包括:

步骤E10,若所述目标处理单元为输出处理单元,则确定所述解码指令中的输出数值指令;

步骤E20,基于所述输出数值指令和所述解码指令确定GPIO输出对应的输出值。

在本实施例中,当目标处理单元为输出处理单元,就会确定解码指令对应的输出数值指令,进而根据输出数值指令和解码指令确定GPIO输出对应的输出值,输出数值指令是指存储的源操作数数值,输出值是指经过输出数值指令和解码指令处理之后的输出值。例如,解码指令为Io.out.raw rs1,rd,对应使用rs1的值作为GPIO的输出值,Io.out.andrs1,rs2,rd是指使用rs1和rs2按位与的值作为GPIO的输出值,Io.out.set/clear rs1,rd是指GPIO中rs1指定位的状态设置为1/0,其他比特位保持原状态不变作为输出值,Io.out.not rs1,rd是指GPIO中rs1指定位的进行翻转,其他比特位保持原状态不变作为输出值。通过解码指令对输出进行控制,不仅提高了控制多样性,而且还不同经过总线处理进而提高了输出的效率。其中,基于所述输出数值指令和所述解码指令确定GPIO输出对应的输出值的步骤,包括:。

步骤F10,确定所述输出数值指令对应的第一源操作数值和第二源操作数值,并确定所述解码指令中的数值操作指令;

步骤F20,基于所述数值操作指令对所述第一源操作数值和所述第二源操作数值进行指令操作确定GPIO输出的输出值。

在本实施例中,对于GPIO输出的输出值控制主要依据寄存器堆存储的第一源操作数和第二源操作数,进而通过两个源操作数的数值以及指令定义的关系输出GPIO的输出值,通过确定输出数值指令对应的第一源操作数值和第二源操作数值,第一源操作数值是指第一源操作的值,第二源操作数值是指第二源操作的值,进而确定解码指令中的数值操作指令,数值操作指令是指对两个源操作数的值进行操作的指令,可以是按位与,按位或,取反等指令,并通过数值操作指令对第一源操作数值和第二源操作数值进行指令操作确定GPIO输出的输出值,指令操作是指指令中对两个数值进行指令操作的方式,可以是上述的按位与,按位或,取反等指令,也可以其他指令,进而可以确定GPIO输出的输出值,实现了GPIO输出控制,进而通过总线可以保证GPIO输出的效率。

进一步的,本实施例还提供了一种基于RISC-V的控制系统,参照图3,图3为本发明基于RISC-V的控制系统的结构示意图。

本实施例中,所述基于RISC-V的控制系统包括开源指令集RISC-V处理器10、指令解码单元20、方向切换单元30、输入处理单元40、输出处理单元50和输入输出端口GPIO60,所述RISC-V处理器10包括指令接口12和寄存器堆11;

所述指令接口12分别与所述寄存器堆11、所述指令解码单元20、所述输入处理单元40和所述输出处理单元50连接,所述指令接口12用于传输所述RISC-V处理器10生成的控制指令;

所述指令解码单元20分别与所述方向切换单元30、所述输入处理单元40和所述输出处理单元50连接,所述指令解码单元20用于根据所述控制指令确定解码指令,并基于所述解码指令确定方向切换信息;

所述GPIO60分别与所述方向切换单元30、所述输入处理单元40和所述输出处理单元50连接,所述输入处理单元40用于根据所述方向切换信息和所述解码指令控制所述GPIO60的输入,所述输出处理单元50用于根据所述方向切换信息和所述解码指令控制所述GPIO60的输出。

参照图5,图5为现有GPIO控制结构示意图,GPIO作为从设备,以内存映射的方式连接到SoC总线上;芯片处理器作为主设备连接到SoC总线上;处理器通过发出内存读写指令控制GPIO模块中的控制寄存器,从而控制/读取芯片IO管脚来自外设的电平。因为总线的存在,使GPIO的控制延时较大,从芯片处理器发出的内存读写指令需要经过总线逻辑之后才能到达GPIO模块,因此延迟较大。故在对IO响应速度有要求的场景下不能满足要求;还有一方面就是,计算与控制分离。通常芯片处理器控制GPIO的输出值,来自于之前指令的计算。比如,先对变量a、b做运算(加减乘除等),得到结果c,再将c写入GPIO的输出控制寄存器控制芯片IO管脚电平。这个过程至少需要由两条指令实现,第一条指令对a、b做运算,第二条指令将c的值写入控制寄存器。计算与控制分离也会影响IO的响应速度,降低系统的实时性;最后一点就是IO方向切换慢。GPIO方向的切换也是通过挂在总线上的寄存器来控制的,同样存在总线延迟大的问题。,因而就上述问题提出了本申请的技术方案,以解决芯片控制的可操作性以及提高芯片输入输出的控制效率。

在本实施例中,开源指令集RISC-V处理器10中的指令生成单元用于生成控制指令,控制指令是指控制方向切换单元30进行方向切换、或输入处理单元40进行输入控制、或输出处理单元50进行输出控制的指令,寄存器堆11用于储存控制指令需要使用到的源操作数,以及控制指令执行完之后的返回值。当开源指令集RISC-V处理器10生成控制指令之后就会经过指令接口12发送至指令解码单元20进行解码得到解码指令,并之后确定解码指令对应的方向切换信息,最终将方向切换信息和解码指令发送至方向切换单元30、输入处理单元40、输出处理单元50,进而实现对输入输出端口GPIO60的方向以及输入输出控制。其中,解码指令是指对控制指令进行解码之后的指令,解码可以是指确定控制指令的控制目标以及指令的控制原理的解码,方向切换信息是指输入输出端口GPIO60对应的输入方向或者输出方向。通过确定方向切换信息和解码指令进而可以通过方向切换单元30实现输入输出端口GPIO60的方向切换,或者通过输入处理单元40实现输入输出端口GPIO60的输入控制,或者通过输出处理单元50实现输入输出端口GPIO60的输出控制。还有一方面就是,开源指令集RISC-V处理器10本身的特性,因为指令集的开源性,可以使用户对控制指令进行自定义以及增加了用户使用的指令修改与扩展功能。值得说明的一点是方向切换单元、输入/输出处理单元可以是一个执行指令的微型单片机芯片,也可以是直接由开源指令集RISC-V处理器10执行控制,寄存器堆是指开源指令集RISC-V处理器10内部存储源操作数的存储位置,指令接口可以是指传输指令的端口。通过上述控制方式还可以避免芯片处理器发出的内存读写指令需要经过总线逻辑之后才能到达GPIO的现象发生,通过方向切换单元进行GPIO的输入输出方向切换控制,或者输入处理单元进行GPIO的输入控制,或者输出处理单元进行GPIO的输出控制,提高了芯片输入输出的控制效率。

本发明通过指令解码单元获取RISC-V处理器读入的控制指令,并确定所述控制指令对应的解码指令;根据所述解码指令和预存的历史切换信息确定方向切换信息;确定所述方向切换信息对应的目标处理单元,通过所述目标处理单元根据所述解码指令对GPIO进行控制。通过指令解码单元获取RISC-V处理器读入的控制指令,进而实现对控制指令解码之后,确定方向切换信息对应的目标处理单元,进而通过目标处理单元根据解码指令对GPIO进行控制,以实现GPIO输入输出的控制。

从而,本发明避免了现有技术中芯片处理器发出的内存读写指令需要经过总线逻辑之后才能到达GPIO的现象发生,这种基于RISC-V的控制方法不仅通过RISC-V处理器读入的控制指令进而可以保证控制指令的开源性,增加了用户使用的指令修改与扩展功能,而且还通过目标处理单元根据解码指令对GPIO进行控制,进而提高了芯片输入输出的控制效率。

本发明还提供一种基于RISC-V的控制系统模块示意图,参照图6,所述基于RISC-V的控制系统包括:

读入解码模块A01,用于通过指令解码单元获取RISC-V处理器读入的控制指令,并确定所述控制指令对应的解码指令;

方向切换模块A02,用于根据所述解码指令和预存的历史切换信息确定方向切换信息;

指令处理模块A03,用于确定所述方向切换信息对应的目标处理单元,通过所述目标处理单元根据所述解码指令对GPIO进行控制。

可选地,方向切换模块A02,还用于:

确定所述解码指令对应的指令特征,检测所述指令特征是否与预设的方向切换指令特征匹配;

若所述指令特征与预设的方向切换指令特征不匹配,则确定预存的历史切换信息对应的传输方向,并将所述传输方向作为方向切换信息。

可选地,方向切换模块A02,还用于:

若所述指令特征与预设的方向切换指令特征匹配,则确定所述解码指令对应的方向指令;

通过方向切换单元根据所述方向指令控制GPIO进行方向切换,并基于方向切换后的GPIO执行所述通过指令解码单元获取RISC-V处理器读入的控制指令的步骤。

可选地,指令处理模块A03,还用于:

确定所述方向切换信息中的传输方向,检测所述传输方向是否与预设的输入方向匹配;

若所述传输方向与预设的输入方向匹配,则确定所述目标处理单元为输入处理单元;

若所述传输方向与预设的输入方向不匹配,则确定所述目标处理单元为输出处理单元。

可选地,指令处理模块A03,还用于:

若所述目标处理单元为输入处理单元,则确定所述解码指令对应的电平返回要求;

基于所述电平返回要求确定GPIO输入的原始电平对应的输入值,且/或确定所述解码指令对应的指令运算,基于所述指令运算确定所述原始电平与预设源操作数对应的返回值。

可选地,指令处理模块A03,还用于:

若所述目标处理单元为输出处理单元,则确定所述解码指令中的输出数值指令;

基于所述输出数值指令和所述解码指令确定GPIO输出对应的输出值。

可选地,指令处理模块A03,还用于:

确定所述输出数值指令对应的第一源操作数值和第二源操作数值,并确定所述解码指令中的数值操作指令;

基于所述数值操作指令对所述第一源操作数值和所述第二源操作数值进行指令操作确定GPIO输出的输出值。

进一步的,基于上述基于RISC-V的控制系统的第一实施例,

本发明还提供一种基于RISC-V的控制芯片。

本发明芯片包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的基于RISC-V的控制程序,所述基于RISC-V的控制程序被处理器执行时实现如上所述的基于RISC-V的控制方法的步骤。

本发明还提供一种存储介质。

本发明存储介质上存储有基于RISC-V的控制程序,所述基于RISC-V的控制程序被处理器执行时实现如上所述的基于RISC-V的控制方法的步骤。

其中,在所述处理器上运行的基于RISC-V的控制程序被执行时所实现的方法可参照本发明基于RISC-V的控制方法各个实施例,此处不再赘述。

需要说明的是,在本文中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者系统不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者系统所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括该要素的过程、方法、物品或者系统中还存在另外的相同要素。

上述本发明实施例序号仅仅为了描述,不代表实施例的优劣。

通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到上述实施例方法可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件,但很多情况下前者是更佳的实施方式。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品存储在如上所述的一个存储介质(如ROM/RAM、磁碟、光盘)中,包括若干指令用以使得一台终端设备(可以是手机,计算机,服务器,或者网络设备等)执行本发明各个实施例所述的方法。

以上仅为本发明的优选实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

- 显示控制芯片的行扫控制方法及存储介质

- 芯片离线烧录方法、装置、系统及计算机可读存储介质

- 芯片离线烧录方法、装置、系统、计算机存储介质及设备

- 基于二维码的景区闸机控制方法、设备、系统及存储介质

- 基于深度强化学习的信号灯控制方法、系统和存储介质

- 基于RISC-V处理器的芯片验证方法、设备及存储介质

- 基于RISC-V处理器的芯片验证方法、设备及存储介质