减少封装集成电路中的脱层

文献发布时间:2023-06-19 19:37:02

相关申请的交叉引用

本申请要求2020年7月30日提交的标题为“减少封装集成电路中的脱层(REDUCINGDELAMINATION IN A PACKAGED INTEGRATED CIRCUIT)”的美国专利申请序列号16/943,445的优先权,其全部内容通过引用明确并入本文。

技术领域

本发明涉及微机电系统(micro-electrical-mechanical systems,MEMS)装置,且尤其涉及用于MEMS装置的封装。

背景技术

封装集成电路(IC)组件可例如通过提供用于该集成电路的组件的容器来促进该集成电路组件的使用。在某些实施例中,可通过提供输入及输出的整合安置的封装以及将封装的组件保持在一起并运作的不同方式来促进这种使用,例如,IC封装可具有维持封装的组件的安置的结构元件,并有利于消散组件所产生的热量。

然而,当IC封装未提供现代IC组件的要求时,例如在某些实施例中,微机电系统(MEMS)可在不同于传统IC组件的条件下最佳地运行,则可能出现问题。在某些情况下,这些问题可能导致IC组件封装降解(degradtion)或失效。因此,用于封装IC组件的常规方法可能具有某些缺点,而某些缺点可参考本文所述的各种实施例来指出。

发明内容

为了提供对实施例的基本理解,以下给出了本发明的一个或更多实施例的简化总结。该总结不是本文中描述的实施例的广泛概要,例如,其既不旨在识别该实施例的关键或重要元素,也不旨在描绘实施例或权利要求的任何范围。该总结的目的是以简化形式呈现实施例的一些概念,作为稍后将呈现的更详细描述的序言。再者,应当理解,除了在发明内容部分中所描述的实施例之外,详细描述可包含其他或替代实施例。

一般而言,在至少某些实施例中,本揭露认知到并解决了减少封装的IC组件的脱层(delamination)的问题。例如,在一个或更多实施例中,感测器可包括感测器晶粒(senordie),该感测器晶粒具有第一感测器表面(sensor surface)及相对于该第一感测器表面的第二感测器表面。该感测器可进一步包括晶粒垫组件,该晶粒垫组件具有第一垫表面(padsurface)及相对于该第一垫表面的第二垫表面,其中,该感测器晶粒与该晶粒垫组件以该第二感测器表面定向朝向该第一垫表面的方式垂直堆叠(stack)。该感测器可进一步包括引线架组件,该引线架组件具有第一框架表面(frame surface)及相对于该第一框架表面的第二框架表面,该晶粒垫组件可与该引线架组件垂直堆叠,其中,该第二垫表面可定向朝向该第一框架表面,该第二垫表面可与该第二框架表面隔离,且该引线架组件可电性连接至该感测器晶粒。

在感测器中,该第二垫表面可基于至少部分地包装在模制化合物(moldingcompound)中而与该第二框架表面隔离。在该感测器中,基于该第二垫表面没有暴露在该引线架组件的外部,可将该第二垫表面与该第二框架表面隔离。在该感测器中,该第二垫表面可与该第二框架表面隔离到基于防止该晶粒垫组件的脱层所需的隔离来选择的程度。

在该感测器中,该感测器晶粒可包含MEMS组件,该MEMS组件包括第一MEMS表面及相对于该第一MEMS表面的第二MEMS表面,其中,该第一感测器表面包括该第一MEMS表面。该感测器可进一步包含专用集成电路(application specific integrated circuit,ASIC)组件,该专用集成电路组件包括第一ASIC表面及相对于该第一ASIC表面的第二ASIC表面,其中,该MEMS组件可以该第二MEMS表面定向朝向该第一ASIC表面的方式与该MEMS组件垂直堆叠,并且其中该第二感测器表面包括该第二ASIC表面。在该感测器中,该MEMS组件可以是MEMS加速度计(MEMS accelerometer)或MEMS陀螺仪(MEMS gyroscope)。

在该感测器中,该第二框架表面可用于定向朝向并安装到电路板。在该感测器中,该第二垫表面可与该第二框架表面热隔离。在该感测器中,该第二垫表面可与该第二框架表面湿气隔离(moisture isolated)。在该感测器中,该第二垫表面可与该第二框架表面电性隔离。该感测器可进一步包含将该感测器组件电性耦合至该引线架组件的接合线(bondwire)。在该感测器中,该感测器组件及该晶粒垫组件可通过该引线架组件被封装在电路封装中。在该感测器中,该电路封装可以是四方扁平无引线封装(quad-flat no leadspackage)。

在该感测器中,该感测器组件及该晶粒垫组件可通过包括模制化合物的材料安装到该引线架组件。在该感测器中,该模制化合物通过包括在该第二垫表面及该第一框架表面之间配置该模制化合物的因数将该晶粒垫组件安装到该引线架组件,并且其中,该第二垫表面可基于该模制化合物而与该第二框架表面隔离。

在该感测器中,可基于该引线架组件中的开口及蚀刻工艺将该晶粒垫组件从该感测器去除,其中,该晶粒垫组件的去除将该第二感测器表面暴露于该感测器的外部。在该感测器中,该晶粒垫组件可通过该引线架组件而被包装,从而导致未暴露的晶粒垫组件。在该感测器中,该第二垫表面可与该第二框架表面隔离,以减少该晶粒垫组件暴露于像是湿度及温度的外部影响。该感测器可进一步包含设置在该第二感测器表面和该第一垫表面之间的粘着层(adhesive layer),从而使该感测器晶粒透过该粘着层固定到该晶粒垫组件。

本文还描述了一种减少IC封装的组件的脱层的方法。此方法可包含提供包括第一感测器表面及相对于该第一感测器表面的第二感测器表面的感测器晶粒。该方法可进一步包含提供包括第一框架表面和与第一感测器表面相对的第二框架表面的引线架封装组件。此外,该方法可以包含将该第二感测器表面固定至晶粒垫组件的第一垫表面,其中,该第一垫表面可与晶粒垫组件的第二垫表面相对,并且其中,在没有透过该引线架封装组件暴露时该第二垫表面可固定到该第一框架表面。

本文描述的另一种方法可以包含提供一感测器晶粒,以及将该感测器晶粒安装至晶粒垫组件,其中该晶粒垫组件被嵌入以从集成电路封装组件中暴露出作为暴露的晶粒垫组件。该方法可进一步包含将暴露的晶粒垫组件从嵌入中去除以从该集成电路封装组件中暴露出来。

在某些情况下,该方法可包含去除暴露的晶粒垫组件,该去除包括在将该感测器晶粒安装至该晶粒垫组件之后通过蚀刻工艺去除该暴露的晶粒垫组件。同时,将该感测器晶粒安装至该晶粒垫组件可基于设置在该第二感测器表面及该第一垫表面之间的接合层(bonding layer),从而导致该感测器晶粒透过该接合层固定到该晶粒垫组件。在该方法中,该接合层可为芯片附接膜黏着剂(film adhesive),且暴露的晶粒垫组件的该去除可导致该接合层被暴露。

以下描述及附图详细阐述了所揭露主题的某些说明性态样。然而,这些态样仅指示可采用所揭露的主题的原理的各种方式中的几种,并且所揭露的主题旨在包含所有这些态样及其等同物。当结合附图考虑时,根据对所揭露主题的以下详细描述,所揭露主题的其他优点及独特特征将变得显而易见。

附图说明

参考以下附图来描述本揭露的非限制性实施例,其中,除非另外指明,否则贯穿不同视图,相同的附图标记指代相同的部分:

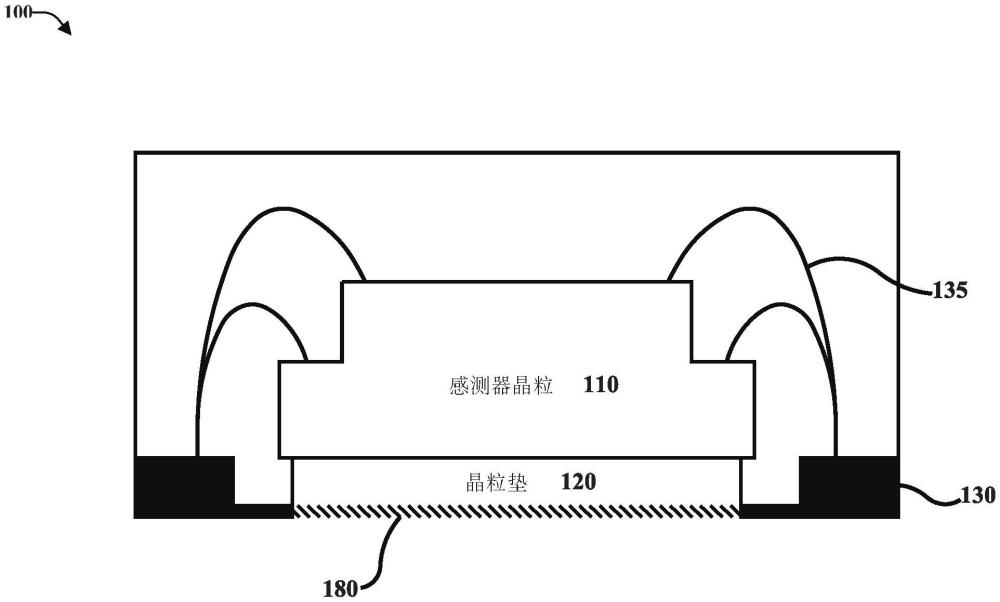

图1和图2示出了依据一个或更多实施例的示例系统的组件的不同视图,该示例系统可有助于封装IC感测器。

图3和图4示出了依据一个或更多实施例的示例系统的组件的不同视图,该示例系统可有助于封装IC感测器。

图5描绘了依据一个或更多实施例的封装在具有晶粒垫的引线架中的感测器晶粒的示例的非限制的展开截面图。

图6描绘了依据一个或更多实施例的图1至图5中描绘的IC封装的示例性实施例的另外的结构态样。

图7示出了依据一个或更多实施例的被设计为减少组件的脱层的IC封装的示例的非限制截面图。

图8和9示出了依据一个或更多实施例的感测器晶粒封装的示例和替代方法。为了简洁起见,省略了在其他实施例中采用的类似元件及/或过程的描述。

图10描绘了依据一个或更多实施例的可形成或实现具有减小脱层可能性的感测器的示例性方法的流程图。

具体实施方式

现在将在下文中参考示出了示例实施例的附图来更全面地描述本揭露的各态样。在以下的描述中,出于解释的目的,阐述了许多具体细节以便提供对各种实施例的透彻理解。然而,本揭露可以以许多不同的形式来体现,并且不应该被解释为限于这里阐述的示例实施例。

整篇说明对于“一个实施例”、“一实施例”或“一个或更多实施例”的参考是指连同该实施例所描述的特别特征、结构、或特性包含在至少一个实施例中。因此,在整篇本说明书的各种地方所出现的词语“在一个实施例中”、“在一实施例中”及“在一个或更多实施例中”并不必然全是指相同的实施例。此外,该特别的特征、结构或特性可在一个或更多个实施例中以任何适合的方式加以组合。

一般而言,在某些情况下,本文讨论的一个或多个实施例可减少IC封装的某些类型的结构故障的发生。可通过一个或更多实施例减少的结构故障的示例类型是基于热应力的该IC封装内部的表面脱层。如下所述,在一些情况下,一个或更多实施例可以有利地降低IC封装脱层的可能性。

应当注意,尽管这里描述了该示例,但一个或更多实施例可改进各种其他类型的IC封装的操作,例如,本揭露的描述所描述和建议的不同的非限制性技术可应用于封装具有各种不同组件和结构的集成电路。

图1和图2示出了依据一个或更多实施例的示例系统的组件的不同视图,该示例系统可有助于封装IC感测器,其中图1依据一个或更多实施例示出了示例系统100的非限制性截面图,而图2依据一个或更多实施例示例示出的系统100的非限制性截面图的底视图200。出于简洁的目的,省略在其他实施例中采用的类似元件及/或过程的描述。

如图所示,系统100可以包含感测器晶粒110和引线架130,其包含晶粒垫组件120和引线135。在该示例中,感测器晶粒110垂直堆叠在晶粒垫组件120上且引线135以通信的方式耦合引线架130到感测器晶粒110的不同部分。

在图1中描绘的示例实施例中,晶粒垫组件120被并入引线架130中以减少晶粒垫组件120及安装到其上的感测器晶粒110暴露于热应力(thermal stress)。在引线架130的某些实施方式中,晶粒垫组件120可嵌入引线架130中以将晶粒垫组件120暴露到引线架130的外部,例如,在图1和图2中所描绘的晶粒垫暴露区域180处。在本文讨论的其他示例中,代替嵌入以暴露晶粒垫组件120于引线架130的外部,该晶粒垫组件120可为引线架130的一部分而不暴露于外部,例如,下面讨论的图3和图4。在另一个示例中,如下图7所讨论的,晶粒垫组件120和感测器晶粒110可以由环氧化合物封装,该化合物设置在晶粒垫组件120及引线架130之间。

在又一示例中,如下图8所讨论的,引线架130可以以初始形式使用,其中晶粒垫组件120被嵌入以便暴露来与引线架130的外部接触,例如,以这种方式从常规零件供应商处采购作为常规零件者。在该示例中,利用图8描述的过程可与一个或更多实施例一起使用以在感测器晶粒110已经安装到晶粒垫组件120之后,将晶粒垫组件120从嵌入中移除以从引线架130暴露,例如,在感测器晶粒110(例如,封装在环氧树脂模制材料中)及外部应力之间留下空的区域。

应当注意,这里对感测器晶粒110的描述是非限制性的,并且该IC感测器组件可广泛地包含可受益于这里描述的封装方法的任何感测器晶粒110。例如,在某些实施例中,感测器晶粒110可为一MEMS感测器与其他可用组件的组合。在另一示例中,感测器晶粒110可包括一MEMS晶粒,并且在另一示例中,感测器晶粒110可包含接合到一CMOS晶粒的MEMS晶粒。可受益于本文描述的不同方法的示例感测器包含但不限于使用MEMS实现的不同感测器,例如MEMS加速度计及MEMS陀螺仪。下面用图5进一步讨论感测器晶粒110的示例组件。

如图1所示,引线架130是可与一个或更多实施例一起使用的示例半导体封装。基于引线架的半导体装置封装是最广泛使用的IC封装。通常地,引线架可包含用于将IC晶粒或芯片附接到引线架的芯片安装垫(例如,晶粒垫组件120,也称为晶粒焊盘(diepaddle)),以及复数个导脚(lead finger)或导电区段(segment),它们提供该晶粒及外部电路之间的导电路径。

像一些其他半导体封装一样,引线架130可使用不同的表面安装方法将硅晶粒(例如,一ASIC和感测器组合)连接(物理及电性两者)到印刷电路板(PCB,未示出)。在示例性实施例中,引线架130可为四方扁平无引线(quad flat no-lead,QFN)半导体封装,其有助于在组装之后查看引线135的能力。

关于图1中描绘的实施例的制造,感测器晶粒110可使用各种不同的方法固定到晶粒垫组件120,例如粘合剂或糊剂(paste),以在有或没有附接组件之间的导电性的情况下将感测器晶粒110附接到晶粒垫组件120。另一个制造的态样包含将晶粒垫组件120附接到引线架130。

鉴于本文的描述,如本领域的技术人员将理解的,以类似于图1的实施例的方式封装的感测器晶粒在某些情况下可经受一个或更多构成组件之间的脱层(例如,感测器晶粒110及晶粒垫组件120之间的附着力损失),以及该组件及IC封装之间的脱层,例如晶粒垫组件120及引线架130之间的脱层。在有或没有例如IC封装破裂的IC结构损坏的情况下,脱层的结果可包含但不限于IC的功能丧失。如下文进一步讨论的,在某些情况下,一个或更多实施例可降低IC封装脱层的可能性。

应当注意,如图1所示,晶粒垫组件120邻接晶粒垫暴露区域180。另外,如图2所示,晶粒垫暴露区域180可通过引线架130包围。如下图3至6进一步讨论的,一个或更多实施例可在晶粒垫暴露区域180中应用不同的材料,以达到不同的效果,例如,限制晶粒垫组件120的暴露。晶粒垫暴露区域180部分地描绘在图2中,以识别出一区域可对应于与晶粒垫组件120相对的区域,其可暴露晶粒垫组件120。在引线架130的某些实施例中,此晶粒垫暴露区域180可对应于一开口,在该开口处晶粒垫组件120安置为在晶粒垫暴露区域180处暴露。例如,可采用这种安置来促进晶粒垫组件120和引线架130外部的环境之间的热转移(thermaltransfer)。

对于某些实施方式,这种热转移的一个效果有益地消散可在引线架130内产生的热量。然而如下所述,某些封装组件可具有与为其设计晶粒垫暴露区域180的组件不同的特性。由于下文描述的不同特性,一个或更多实施例可实施具有不同结构的引线架,例如改变引线架130的晶粒垫暴露区域180的态样以达到包含但不限于以下结果的结构,晶粒垫组件120与引线架130外部环境之间的热转移变化,以及减少进入引线架130的湿气。

图3和图4图示出了依据一个或更多实施例的示例系统的组件的不同视图,该示例系统可有助于封装IC感测器,图3示了在具有晶粒垫组件120的引线架330中封装的感测器晶粒110的示例300的非限制性截面图,以及图4描绘了依据一个或更多实施例的示例300的非限制性示例底视图400。出于简洁的目的,省略了在其他实施例中采用的类似元件及/或过程的描述。

示例300包括垂直堆叠在晶粒垫组件120上的感测器晶粒110,其中该组件的组合封装在引线架330中。为了描述示例300的不同特征,所描绘的组件的一些侧面被标记,例如,感测器晶粒110包含与第二感测器表面317相对的第一感测器表面315,晶粒垫组件120包含与第二垫表面334相对的第一垫表面325,并且引线架330包含与第二框架表面335相对的第一框架表面332。

现在用上面讨论的示例300的部分来讨论一些示例性实施例。在示例设备的一个或更多实施例中,感测器晶粒110可包括第一感测器表面315及相对于第一感测器表面315的第二感测器表面317,以及包第一垫表面325及相对于第一垫表面325的第二垫表面334的晶粒垫组件120,其中,感测器晶粒110与晶粒垫组件120垂直堆叠,并且第二感测器表面317定向朝向第一垫表面325。示例300可进一步包含引线架330,其包含第一框架表面332及相对于第一框架表面332的第二框架表面335,晶粒垫组件120与引线架330垂直堆叠,在某些示例中,第二垫表面334定向朝向第一框架表面332。

将图3及4与上面讨论的图1及2做对比说明。例如,如图3所示,引线架330的截面图包含用实线(solid line)代替的晶粒垫暴露区域180,该实线可指示晶粒垫组件120的第二垫表面334及晶粒垫组件120的外部暴露之间的屏障,此屏障是例如引线架330的一部分。在一个或更多实施例中,为了产生引线架330,引线架130的设计可被修改为去除用于晶粒垫暴露区域180的全部或部分开口。因此,如图所示,在此示例引线架330中,晶粒垫组件120的第二垫表面334邻接引线架130的第一框架表面332,并且引线架130在邻接外部表面的第一框架表面332之间具有固体屏障(solid barrier),例如PCB(未示出)。

回到一个或更多实施例的益处及操作,如上所述,与图1-4中所描绘的那些IC封装具有相似的IC封装(例如,彼此附着的组件及引线架130的堆叠层)在某些情况下可能会发生脱层。一个或更多实施例可降低某些类型的脱层的可能性。

更详细地考虑脱层,在装置测试或使用期间,感测器晶粒110及晶粒垫组件120可经历规则及不规则的温度变化循环。鉴于本文的揭露,如本领域技术人员将理解的,温度循环可在封装的感测器晶粒110的不同部分处造成热机械应力。示例应力点包含第二感测器表面317及第一垫表面325,以及该封装元件及引线架130之间的界面点(interfacepoint)。在某些情况下,不同层中使用的材料可加强这些应力,例如,不相似的材料可具有不同的热膨胀系数(CTE)造成材料以不同的速率膨胀及收缩。一些制造特征会加剧这些温度变化,例如下图5及图6所描述的元件的包装。

如上所述,由这些应力的重复示例引起的疲劳会导致封装元件的脱层。需要说明的是,脱层造成封装IC的结构失效代表通过脱层造成的极端失效,并且一个或更多实施例也可以降低脱层所造成的较小失效的可能性。

可加剧上述热机械应力的另一个因素是引线架330内部的湿气,例如进入引线架330封装的湿气。湿气进入的一种方式是经由暴露的晶粒垫组件120暴露,例如经由上述晶粒垫暴露区域180中的一开口。在某些情况下,湿气加剧的应力可能是由于内部湿气蒸发而形成的压力造成的,例如,在条件合格及其他时间的焊料回熔(solder reflow)期间。

为了解决脱层的这些示例原因,一个或更多实施例可以基于对封装元件的潜在散热要求的评估来确定导热性(例如,晶粒垫组件120和外部环境之间的)的降低是否可以是有利地内置于封装IC感测器的设计中。例如,在感测器晶粒110的一些实施例中(例如,使用如下所述的MEMS感测器组件),可具有比其他实施例更低的功率耗散,例如,与其他实施例相比,更少的通过操作产生的热量。

当基于热机械力(例如,预测的温度循环)将产生较少热量的这一评估与脱层的可能性一起考虑时,一个或更多实施例可利用图3和4中描绘的安置,例如用以增加晶粒垫组件120与外部温度波动的热隔离,通过例如物理地隔离晶粒垫组件120。通过晶粒垫组件120的物理隔离,还可以减少湿气和杂质经由晶粒垫暴露区域180的进入。至少基于晶粒垫组件120的这种热隔离以及防止湿气进入,一个或更多实施例可降低上述类型的脱层的可能性。

图5描绘了依据一个或更多实施例的在具有晶粒垫组件120的引线架330中封装感测器晶粒110的示例500的非限制的展开截面图。出于简洁的目的,省略了在其他实施例中采用的类似元件及/或过程的描述。扩展图3和4的示例300,图5的示例500进一步包含设置在第二感测器表面317及第一垫表面325之间的接合层550。

在一个或更多实施例中,接合层550可以包含不同的接合元件,包含但不限于接合膜(bonding film)、接合膏(bonging paste)、非导电接合元件(non-conductive bondingelement)和导电接合元件(conductive bonding element)。在示例性实施例中,接合层550可是晶粒附接膜(die attached film,DAF)粘着剂,例如将第一接合表面552附接到第二感测器表面317。对于一个或更多实施例可能有利的DAF的一些特性包含,特别是对于高钨(Tg)DAF,对脱层相对不敏感,例如,通过一个或更多实施例进一步减少脱层的可能性。

在组装时,第二接合层554可接合到第一垫表面325,例如,用以将感测器晶粒110固定到晶粒垫组件120。关于接合层550的附加细节在下面与感测器晶粒110的不同元件的讨论一起提供。

图6描绘了在图1至图5中依据一个或更多实施例描绘的IC封装的示例性实施例的另外的结构态样。出于简洁的目的,省略了在其他实施例中采用的类似元件及/或过程的描述。在一个或更多实施例中,如图6所示,MEMS组件610耦合至ASIC 620。在所描绘的额外细节中,引线接合件660可以将引线架130耦合至MEMS组件610及ASIC 620。

如图所示,在某些实施例中,感测器晶粒110可包括MEMS组件610及ASIC 620。在一个或更多实施例中,MEMS组件610生成的信号可传送到ASIC 620以进行处理,从而产生输出信号。在图3-5中讨论的表面的上下文中考虑这些组件,在某些实施例中,感测器晶粒110可具有第一MEMS表面615及与第一MEMS表面615相对的第二MEMS表面613,感测器晶粒110的第一感测器表面315对应于第一MEMS表面615。在另外的实施例中,专用集成电路(ASIC)620组件可包含第一ASIC表面616及与第一ASIC表面616相对的第二ASIC表面621,MEMS组件610与ASIC 620垂直堆叠,其中第二MEMS表面613定向朝向第一ASIC表面616,并且第二感测器表面对应于第二ASIC表面621。回到上面讨论的接合层550,应该注意的是,DAF可在组装的第一阶段附接到ASIC 620,例如,在晶片切割阶段(saw stage)之前,将DAF添加到IC的未切割晶片中。

ASIC 620可以包含电路组件及连接以促进基于通过MEMS组件610生成的信号的处理和生成输出。可并入于感测器晶粒110的一个或更多实施例中的示例MEMS组件610可以包含MEMS感测器,其可以包含,但不限于以上图3中所讨论的MEMS陀螺仪和MEMS加速度计,以及MEMS声学感测器(acoustic sensor)、MEMS电容式感测器(例如,电容式麦克风)、驻极体感测器(electret sensor)(例如,驻极体电容式麦克风(electret condensermicrophone,ECM))、电容式感测器和电容式天线。如本文所用,电路可以指任何基于类比及/或数位的装置,其包含用于执行与实施例相关联的功能的电路,包含但不限于电阻器、电容器、晶体管、二极管、电感器、存储器和可编程装置。

如图6所示,引线架130及感测器晶粒110之间的间隙可用附接到引线架330的接合线680桥接。在不同的实施例中,接合线680可由各种材料形成,包含但不限于,金、铜、铝及其合金。在引线架330内的组件组装之后,感测器晶粒110、接合线680及引线架330的部分可被包装在例如环氧树脂模制化合物(epoxy molding compound)690的模制化合物中。

如上所述,这种包装在某些情况下会进一步加剧热机械应力,例如,通过减少散热。然而,在一个或更多实施例中,包装可用于进一步将组件与潜在的破坏性温度变化隔离。例如,虽然图6描绘了贴靠第一框架表面332的晶粒垫组件120的第二垫表面334(与上面图5一起讨论),但是在一个或更多实施例中,晶粒垫组件120可在第二垫表面334和第一框架表面332之间设置有填充有环氧树脂模制化合物690的空间,例如,如下面图7所讨论的。

图7示出了依据一个或更多实施例的被设计为减少组件的脱层的IC封装的示例700的非限制横截面图。出于简洁的目的,省略了在其他实施例中采用的类似元件及/或过程的描述。

在一个或更多实施例中,引线架330可以是没有开口来暴露晶粒垫组件120的引线架组件(例如,引线架130)。晶粒垫组件120描绘为透过接合层550接合到感测器晶粒(例如,感测器晶粒110),该感测器晶粒包含接合到ASIC 620的MEMS组件610。

应当注意的是,在示例700的IC封装的组装过程中,在晶粒垫组件120及引线架330之间留下了一空间750。在一个或更多实施例中,晶粒垫组件120相对于引线架330的这种定位的这种安置可被称为具有反向向下设置的晶粒垫(也称为反向凹入的晶粒垫)的引线架。在一个或更多实施例中,该空间750可促进通过引线架330(例如通过环氧树脂模制化合物690)封装的部件的完全包装。

相关领域的技术人员将理解,鉴于本文的描述,所描述的完全包装在某些情况下可以进一步降低脱层的可能性,例如,至少通过以上描述的热结构应力及湿气应力。

图8和图9示出了依据一个或更多实施例的感测器晶粒封装的示例800和替代方法。为了简洁起见,省略了在其他实施例中采用的类似元件及/或过程的描述。

考虑到这些替代方法,应该注意的是,在某些情况下,一些传统的引线架(例如,带有暴露的晶粒垫组件)制造为将暴露的晶粒垫组件附接作为引线架的一部分,并且其他组件可固定在晶粒垫上。在上述替代实施例中,引线架(例如,图3的引线架330)的设计及制造可修改为具有不同的结构,例如不暴露晶粒垫组件。

在下面讨论的另一种替代方法中,代替重新设计的、不同制造的引线架,可使用传统的引线架(例如,具有预先放置的、暴露的晶粒垫组件),并在实施过程中进行变更以具有一些下面描述的实施例的特征。这种变更可在不同时间发生,在封装IC的组装期间执行示例性实施例。因此,在该示例中,代替使用诸如引线架330之类的没有用于暴露的晶粒垫的开口的引线架,使用具有晶粒垫已经设置在例如类似于图1所描述的晶粒垫暴露区域180的暴露位置(未示出)中的引线架830是可能有利的。在制造一个或更多实施例的一个方法中,感测器晶粒110可固定到引线架830的晶粒垫组件(未示出),并且可执行其他制造过程,然后可执行额外的蚀刻工艺,从引线架830去除晶粒垫组件,同时保留剩余的其他组件。

在本文给定的描述中,本领域的技术人员将理解到,可执行不同动作以将感测器晶粒组件及引线架830组装到封装IC中。在一个或更多实施例中,在组装期间,为了促进如上所述的晶粒垫组件的去除,可将化学蚀刻工艺添加到能够从引线架830去除晶粒垫的组装过程中。在某些实施例中,这种蚀刻步骤可以在放置其他组件之后执行,例如在MEMS 610垂直堆叠在ASIC 620上之后,并且在这些组件已经接合到该晶粒垫之后,设计额外的蚀刻工艺以去除晶粒垫,同时不影响到引线架830、ASIC 620或任何其他组件。在示例性实施例中,可在组装的第二阶段期间执行附加的蚀刻,例如在去毛边(deflashing)及去毛头(de-burring)之后,但在组件的激光标记(laser marking)之前。在本文给定的描述中,本领域的技术人员将理解到,实现特定的细节(例如,封装的组件、使用的材料)可造成组装过程中的另一点被有利地选择用于这种额外的蚀刻。

回到蚀刻工艺的结果,如上所述,在一个或更多实施例中,可以设计蚀刻工艺以去除晶粒垫组件,同时不影响到其他组件。可用于促进这种目标蚀刻的方法可涉及接合层550的使用。如上所述,可使用晶粒附接膜(DAF)粘着剂来实施接合层550。在某些情况下,通过额外蚀刻去除晶粒垫会暴露DAF粘着剂。例如,阴影区域860对应于在额外蚀刻工艺之后可保留的空的区域。这个包含的空的区域可产生不同的好处。

例如,在一个或更多实施例中,该空的区域可进一步降低感测器晶粒110所暴露的应力,因为此空间(例如,包含上述DAF和环氧树脂模制化合物)的CTE可小于去除的晶粒垫组件120。因此,在这些替代实施例中,还可以减轻可能造成封装IC脱层的外部应力,与可使用常规引线架830的其他实施例相比具有额外优势。

图10描绘了依据一个或更多实施例的可形成或实现具有减小脱层可能性的感测器的示例性方法1000的流程图。

应当理解及了解,关于特定装置、系统或方法所描述的组件(例如,晶粒垫组件、MEMS组件、ASIC组件、引线架组件及接合层)可包括与关于本文公开的其他装置、系统或方法所描述的相应组件(例如,分别命名的组件或相似命名的组件)相同的或相似的功能。

在步骤1002中,方法1000可包括提供感测器晶粒。例如,可以提供如图1所示的感测器晶粒110。在步骤1004,方法1000可包括将感测器晶粒安装到晶粒垫组件,该晶粒垫部件被嵌入以从集成电路封装组件暴露作为暴露的晶粒垫组件。例如,感测器晶粒110可安装到晶粒垫组件120,其中晶粒垫组件被嵌入以从集成电路封装组件(例如,引线架130)暴露作为暴露的晶粒垫组件120。

在步骤1006中,方法1000可包括从嵌入中去除暴露的晶粒垫组件,以从集成电路封装组件暴露。例如,可以通过在组装IC封装的其他部分之后执行的额外蚀刻工艺而将暴露的晶粒垫组件120从嵌入中去除以从引线架130暴露。该蚀刻可导致对应于空的区域的区域860,例如用于放置环氧树脂模制化合物690。

虽然各种实施例易于进行各种修改和替代构造,但在附图中示出其某些图示的实施方式并且已经在上面详细描述。然而,应当理解,并非意图将各种实施例限制于所揭露的特定形式,反之,意图是涵盖落入各种实施例的精神和范围内的所有修改、替代构造和等同物。此外,虽然各种实施例易于进行各种修改及替代构造,但是在附图中示出其某些图示的实施例并且已经在上面详细描述。然而,应当进一步理解,并非意图将各种实施例限制于所揭露的特定形式,反之,意图是涵盖落入本发明的各种实施例的精神和范围内的所有修改、替代构造和等同物。

就这方面而言,虽然该揭露的发明已经连同各种实施例和对应的图式加以描述,但在可应用处,应了解到也可使用其它相似的实施例、或可通过实施该揭露的发明的相同、类似、替代、或替换功能,而对该揭露的实施例作出修改和添加,而不致于从其偏离。因此,该揭露的发明不应被限制至本文所描述的任何单一实施例,反而应该依据以下附加的权利要求的广度(breadth)和范围加以解读。

上文所描述的包含主要揭露的示例。当然,为了描述该发明标的的目的,不可能描述组件及/或方法的每个想象得到的组合,但是应了解的是各种实施例的很多更进一步的组合及变更是可能的。因此,所主张的发明标的是意在含括落在附加的权利要求的精神及范畴内的所有此类的变更、修正及变化。尽管出于说明性目的在主题揭露中描述了特定实施例及示例,但是在此类实施例及示例的范围内考虑的各种修改是可能的,如本领域的技术人员可以认识到的。

本申请中使用的术语“组件”、“模块”、“装置”和“系统”旨在指代计算机相关实体,可以是硬件、硬件及软件的组合、软件或执行中的软件。作为一个示例,组件或模块可以是但不限于在处理器上运行的程序、处理器或其一部分、硬盘驱动器、多个存储驱动器(光及/或磁性存储介质的)、物件、执行档、执行绪、程序及/或计算机。举例来说,在伺服器上运行的应用程序及伺服器都可以是组件或模块。一个或更多组件或模块扫描驻留在程序及/或执行绪内,并且组件或模块可以定位在一个计算机或处理器上及/或分布在两个或更多计算机或处理器之间。

如本文所用,术语“推断(infer)”或“推论(inference)”通常是指从经由事件、信号及/或数据捕获的一组观察中推理或推断系统及/或环境的状态的过程。例如,可以使用推论来识别特定的上下文或动作,或者可产生状态的机率分布。推论可以是机率性的,也就是说,基于对数据和事件的考虑来计算感兴趣的状态的机率分布。推论还可以指用于从一组事件及/或数据组成更高级别事件的技术。这种推论导致从一组观察到的事件及/或存储的事件数据构建新的事件或动作,无论这些事件在时间上是否紧密相关,以及无论事件和数据是否来自一个或数个事件及数据来源。

此外,“示例”或“示例性”在本文中用于表示作为示例、实例或说明。再者,文字“示范的”及/或“展示的”在本文中是用作示例、实例或说明。为了避免起疑惑,本文所揭露的发明并不受限于这种范例。此外,在本文描述成“示范的”及/或“展示的”的任何态样或设计并不必然被解读为比其它态样或设计较佳或占优势的,它也不是指排除本领域中具有通常技术者已知的等效示范的结构及技术。

在本专利说明书中,用语“或”旨在意指包含的“或”而不是排外的“或”。亦即,除非另有说明,或从上下文可明白,“X使用A或B”旨在意指自然的包含性排列中的任一者。亦即,如果X使用A;X使用B;或X使用A与B两者,则以上任一示例都满足“X使用A或B”。此外,使用于本专利说明书及附图的冠词“一(a及an)”应大体被视为意指“一或多个”,除非另有说明,或从上下文可明白它是指向单数形式。

此外,虽然可能已经关于数个实施例中的仅一个实施例揭露了一个态样,但是这种特征可以与其他实施例的一个或更多其他特征组合,如对于任何给定或特定应用可能是期望的和有利的。此外,如果在实施方式或附加的权利要求中使用术语“包含”、“具有”、“含有”、其变体及其它类似词语,则这些术语是旨在以类似于术语“包括”作为开放性连接词(open transition word)的方式包含在内,而不排除任何额外或其它的元件。