半导体结构的制造方法

文献发布时间:2023-06-19 10:38:35

技术领域

本发明涉及一种半导体结构的制造方法,且特别是涉及一种具有绝缘层覆硅(silicon on insulator,SOI)结构的半导体结构的制造方法。

背景技术

由于SOI结构与基底高隔离及低接面电容的特性,其相关的半导体元件持续显现大有可为的潜力,如SOI鳍式场效晶体管(fin field-effect transistor,FINFET)、SOI无接面晶体管(junctionless transistor)、SOI纳米线等。然而,由于目前SOI结构的制造方法相当复杂且需要特殊工具进行制作,所以这些常规方法的制造成本相当高昂。

发明内容

本发明提供一种半导体结构的制造方法,其可有效地降低SOI结构的制作工艺复杂度与制造成本。

本发明提出一种半导体结构的制造方法,包括以下步骤。提供基底,其中基底包括SOI区。在基底上形成图案化硬掩模层。图案化硬掩模层的上视形状为网状。以图案化硬掩模层作为掩模,移除部分基底,而形成多个沟槽与位于多个沟槽之间的突出部,且使得基底包括基部与突出于基部的突出部。在SOI区的图案化硬掩模层的侧壁上与SOI区的突出部的侧壁上形成间隙壁。在SOI区中,以图案化硬掩模层与间隙壁作为掩模,对沟槽所暴露出的基底进行热氧化制作工艺,而在SOI区的基底中形成贯穿氧化物层。贯穿氧化物层延伸通过SOI区的沟槽下方与SOI区的突出部下方。

依照本发明的一实施例所述,在上述半导体结构的制造方法中,贯穿氧化物层可将SOI区的突出部与SOI区的基部进行隔离。

依照本发明的一实施例所述,在上述半导体结构的制造方法中,还可包括在间隙壁与突出部之间形成衬层。

依照本发明的一实施例所述,在上述半导体结构的制造方法中,间隙壁与衬层的形成方法可包括以下步骤。在突出部的侧壁上与基部上形成衬材料层。形成覆盖图案化硬掩模层与衬材料层的间隙壁材料层。移除部分间隙壁材料层与部分衬材料层,而形成间隙壁与衬层,且暴露出SOI区的图案化硬掩模层与SOI区的基部。

依照本发明的一实施例所述,在上述半导体结构的制造方法中,部分间隙壁材料层与部分衬材料层的移除方法例如是干式蚀刻法。

依照本发明的一实施例所述,在上述半导体结构的制造方法中,还可包括在形成间隙壁之后且在形成贯穿氧化物层之前,对SOI区的基部进行各向异性湿式蚀刻制作工艺,而在SOI区的基部中形成凹陷。

依照本发明的一实施例所述,在上述半导体结构的制造方法中,还可包括在形成贯穿氧化物层之后,移除部分突出部。

依照本发明的一实施例所述,在上述半导体结构的制造方法中,还可包括以下步骤。在形成贯穿氧化物层之后,形成填入沟槽且覆盖图案化硬掩模层与间隙壁的填充层。移除SOI区的部分填充层与SOI区的图案化硬掩模层,而暴露出SOI区的突出部的顶部。

依照本发明的一实施例所述,在上述半导体结构的制造方法中,还可包括以下步骤。移除至少部分填充层,而暴露出至少部分间隙壁。移除暴露出的至少部分间隙壁,而暴露出突出部的至少部分侧壁。

依照本发明的一实施例所述,在上述半导体结构的制造方法中,基底还可包括非SOI区。在形成贯穿氧化物层之后,非SOI区的突出部与非SOI区的基部可彼此相连。

基于上述,在本发明所提出的半导体结构的制造方法中,通过热氧化制作工艺形成贯穿氧化物层,而制作出SOI结构,因此可降低SOI结构的制作工艺复杂度与制造成本。此外,网状的图案化硬掩模层可具有局部对称网格(local symmetric mesh)。因此,在形成贯穿氧化物层时,网状的图案化硬掩模层的局部对称网格可将突出部两侧因氧化所产生的方向相反的应力相互抵消,以防止突出部产生歪斜。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附的附图作详细说明如下。

附图说明

图1A至图1M为本发明一实施例的半导体结构的制造流程剖视图;

图2A至图2D为本发明一些实施例的图案化掩模层的上视形状的示意图;

图3A至图3F为本发明一些实施例的经切割后的突出部的上视形状的示意图。

符号说明

100:基底

102、102a:缓冲层

104、104a:掩模层

106:定义层

108:图案化硬掩模层

110:衬材料层

110a:衬层

112:间隙壁材料层

112a:间隙壁

114、118:图案化光致抗蚀剂层

116:贯穿氧化物层

120:填充层

B:基部

P:突出部

R:凹陷

R1:SOI区

R2:非SOI区

T:沟槽

具体实施方式

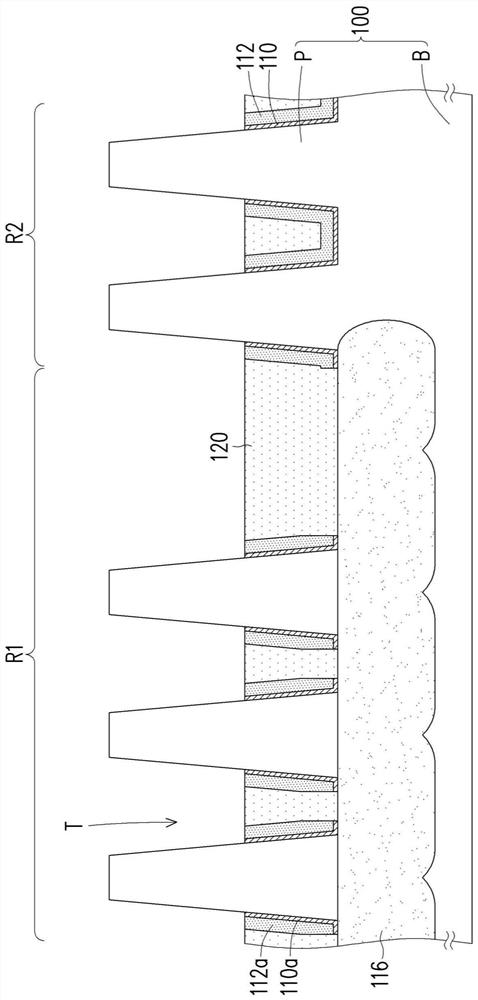

图1A至图1M为本发明一实施例的半导体结构的制造流程剖视图。图2A至图2D为本发明一些实施例的图案化掩模层的上视形状的示意图。图3A至图3F为本发明一些实施例的经切割后的突出部的上视形状的示意图。

请参照图1A,提供基底100,其中基底100包括SOI区R1。此外,基底100更可包括非SOI区R2,但本发明并不以此为限。在其他实施例中,根据产品需求,基底100也可不包括非SOI区R2。基底100可为半导体基底,如硅基底或砷化铝镓(AlGaAs)基底等。

接着,可在基底100上形成缓冲层102。缓冲层102的材料例如是氧化硅。缓冲层102的形成方法例如是热氧化法。

然后,可在缓冲层102罩上形成掩模层104。掩模层104的材料例如是氮化硅。掩模层104的形成方法例如是化学气相沉积制作工艺。

接下来,可在掩模层104上形成定义层106。定义层106的材料例如是非晶碳。定义层106例如是组合使用沉积制作工艺与图案化制作工艺所形成。图案化制作工艺可使用光刻制作工艺与蚀刻制作工艺来进行。在一些实施例中,为了获得更小的线宽,上述图案化制作工艺可采用自对准双重图案化(self-aligned double patterning,SADP)制作工艺、自对准四重图案化(self-aligned quadruple patterning,SAQP)制作工艺或自对准八重图案化(self-aligned octuple patterning SAOP)制作工艺。

请参照图1B,可利用定义层106作为掩模,移除部分掩模层104与部分缓冲层102,而形成掩模层104a与缓冲层102a。由此,可在基底100上形成图案化硬掩模层108。图案化硬掩模层108可包括缓冲层102a与掩模层104a。在本实施例中,图案化硬掩模层108是以多层结构为例,然而本发明的图案化硬掩模层108的结构与制造方法并不以此为限。在其他实施例中,图案化硬掩模层108可为单层结构或三层以上的多层结构。举例来说,图案化硬掩模层108可为仅包括掩模层104a的单层结构。

此外,请参照图2A至图2D,图案化硬掩模层108的上视形状为网状,且可具有局部对称网格。图2A至图2D中的图案化硬掩模层108的上视形状仅为举例说明,本发明的网状的图案化硬掩模层108的形状并不以此为限。只要网状的图案化硬掩模层108的形状具有局部对称网格,即属于本发明所涵盖的范围。

请参照图1C,移除定义层106。定义层106可通过灰化制作工艺进行移除。

接着,以图案化硬掩模层108作为掩模,移除部分基底100,而形成多个沟槽T与位于多个沟槽T之间的突出部P,且使得基底100包括基部B与突出于基部B的突出部P。突出部P可用以作为半导体元件的主动区。由于突出部P是利用网状的图案化硬掩模层108作为掩模而形成,因此图案化硬掩模层108的上视形状可为网状。部分基底100的移除方法例如是干式蚀刻法。

请参照图1D,可在突出部P的侧壁上与基部B上形成衬材料层110。衬材料层110的材料例如是氧化硅。衬材料层110的形成方法例如是热氧化法。

然后,可形成覆盖图案化硬掩模层108与衬材料层110的间隙壁材料层112。间隙壁材料层112的材料例如是氮化硅。间隙壁材料层112的形成方法例如是化学气相沉积法。

请参照图1E,可在非SOI区R2中形成图案化光致抗蚀剂层114。图案化光致抗蚀剂层114可覆盖非SOI区R2的间隙壁材料层112。图案化光致抗蚀剂层114可通过光刻制作工艺所形成。在其他实施例中,在基底100不包括非SOI区R2的情况下,可不形成图案化光致抗蚀剂层114。

接着,可移除部分间隙壁材料层112与部分衬材料层110,而形成间隙壁112a与衬层110a,且暴露出SOI区R1的图案化硬掩模层108与SOI区R1的基部B。由此,可在SOI区R1的图案化硬掩模层108的侧壁上与SOI区R1的突出部P的侧壁上形成间隙壁112a,且可在间隙壁112a与突出部P之间形成衬层110a,但本发明并不此为限。在其他实施例中,也可不形成衬层110a。部分间隙壁材料层112与部分衬材料层110的移除方法例如是干式蚀刻法。

此外,在形成间隙壁112a与衬层110a的制作工艺中,图案化光致抗蚀剂层114可用以保护非SOI区R2的间隙壁材料层112与非SOI区R2的衬材料层110。如此一来,在形成间隙壁112a与衬层110a之后,在非SOI区R2中仍保留间隙壁材料层112与衬材料层110。

请参照图1F,可对SOI区R1的基部B进行各向异性湿式蚀刻制作工艺,而在SOI区R1的基部B中形成凹陷R。通过对基部B进行各向异性湿式蚀刻制作工艺,可使得凹陷R所暴露出的基部B具有相同方向的晶格面。在其他实施例中,可不对基部B进行各向异性湿式蚀刻制作工艺。

请参照图1G,可移除图案化光致抗蚀剂层114。图案化光致抗蚀剂层114的移除方法例如是干式去光致抗蚀剂法(dry stripping)或湿式去光致抗蚀剂法(wet stripping)。在本实施例中,是以先通过各向异性湿式蚀刻制作工艺在SOI区R1的基部B中形成凹陷R,再移除图案化光致抗蚀剂层114为例,但本发明并不以此为限。在其他实施例中,可先移除图案化光致抗蚀剂层114,再通过各向异性湿式蚀刻制作工艺在SOI区R1的基部B中形成凹陷R。各向异性湿式蚀刻制作工艺所使用的蚀刻剂例如是四甲基氢氧化铵(tetramethylammonium hydroxide,TMAH)或氢氧化钾(KOH)。

接着,在SOI区R1中,以图案化硬掩模层108与间隙壁112a作为掩模,对沟槽T所暴露出的基底100进行热氧化制作工艺,而在SOI区R1的基底100中形成贯穿氧化物层116。举例来说,可通过热氧化法在突出部P两侧的基部B中形成氧化物(未示出),且突出部P两侧的氧化物可持续成长而彼此相连且合并(merge),以形成贯穿氧化物层116。在通过热氧化制作工艺形成贯穿氧化物层116时,网状的图案化硬掩模层108的局部对称网格可将突出部P两侧因氧化所产生的方向相反的应力相互抵消,以防止突出部P产生歪斜。在本实施例中,由于凹陷R所暴露出的基部B可具有相同方向的晶格面,由此可提升氧化速率的均匀性。此外,贯穿氧化物层116的剖面形状可具有波浪状的底部轮廓。

贯穿氧化物层116延伸通过SOI区R1的沟槽T下方与SOI区R1的突出部P下方,由此可在SOI区R1中形成SOI结构。此外,贯穿氧化物层116可将SOI区R1的突出部P与SOI区R1的基部B进行隔离。在进行上述热氧化制作工艺的过程中,由于间隙壁材料层112与衬材料层110覆盖非SOI区R2的基部B,因此贯穿氧化物层116不会延伸通过非SOI区R2的沟槽T下方与非SOI区R2的突出部P下方。如此一来,在形成贯穿氧化物层116之后,非SOI区R2的突出部P与非SOI区R2的基部B可彼此相连。

请参照图1H,可形成暴露出部分突出部P的图案化光致抗蚀剂层118。图案化光致抗蚀剂层118可暴露出SOI区R1及/或非SOI区R2的部分突出部P。在本实施例中,图案化光致抗蚀剂层118是以暴露出SOI区R1的部分突出部P为例来进行说明,但本发明并不以此为限。此外,图案化光致抗蚀剂层118可通过光刻制作工艺所形成。

请参照图1I,可利用图案化光致抗蚀剂层118作为掩模,移除图案化光致抗蚀剂层118所暴露出的部分图案化硬掩模层108与部分突出部P。通过进行图1H与图1I的步骤,可在SOI区R1及/或非SOI区R2中,对突出部P进行主动区切割制作工艺,而使得突出部P具有所需的主动区形状。在本实施例中,是以对SOI区R1的突出部P进行切割为例来进行说明,但本发明并不以此为限。请参照图3A至图3F,经切割后的突出部P的上视形状可包括点状(图3A)、条状(图3B)、方环状(图3C)、L形(图3D)、十字形(图3E)、圆环状(图3F)或其组合,但本发明并不以此为限。

请参照图1J,可移除图案化光致抗蚀剂层118。图案化光致抗蚀剂层118的移除方法例如是干式去光致抗蚀剂法或湿式去光致抗蚀剂法。

接着,形成填入沟槽T且覆盖图案化硬掩模层108与间隙壁112a的填充层120。此外,填充层120更可覆盖非SOI区R2的间隙壁材料层112。填充层120的材料例如是氧化硅。填充层120的形成方法例如是化学气相沉积法。

请参照图1K,可移除SOI区R1的部分填充层120与SOI区R1的图案化硬掩模层108,而暴露出SOI区R1的突出部P的顶部。在移除SOI区R1的部分填充层120与SOI区R1的图案化硬掩模层108的制作工艺中,可同时移除部分间隙壁112a。此外,可移除非SOI区R2的部分填充层120、非SOI区R2的部分间隙壁材料层112与非SOI区R2的图案化硬掩模层108,而暴露出非SOI区R2的突出部P的顶部。部分填充层120、部分间隙壁材料层112、图案化硬掩模层108与部分间隙壁112a可通过平坦化制作工艺进行移除。平坦化制作工艺例如是化学机械研磨制作工艺或是组合使用化学机械研磨制作工艺与湿式蚀刻制作工艺。

请参照图1L,可移除至少部分填充层120,而暴露出SOI区R1的至少部分间隙壁112a,且暴露出非SOI区R2的至少部分间隙壁材料层112。至少部分填充层120的移除方法例如是回蚀刻法。在本实施例中,是以移除部分填充层120,且暴露出部分间隙壁112a与部分间隙壁材料层112为例,但本发明并不以此为限。在其他实施例中,也可移除全部填充层120,而暴露出整个间隙壁112a与整个间隙壁材料层112。

请参照图1M,可移除暴露出的至少部分间隙壁112a与至少部分衬层110a,且可同时移除暴露出的至少部分间隙壁材料层112与至少部分衬材料层110,而暴露出突出部P的至少部分侧壁。至少部分间隙壁112a、至少部分衬层110a、至少部分间隙壁材料层112与至少部分衬材料层110的移除方法例如是湿式蚀刻法。在本实施例中,是以移除部分间隙壁112a、部分衬层110a、部分间隙壁材料层112与部分衬材料层110,且暴露出突出部P的部分侧壁为例,但本发明并不以此为限。在其他实施例中,也可移除全部间隙壁112a、全部衬层110a、全部间隙壁材料层112与全部衬材料层110,而暴露出突出部P的整个侧壁。

在暴露出突出部P的至少部分侧壁之后,可继续进行后续的栅极工程与元件工程,而完成半导体元件的制作。此外,后续的栅极工程与元件工程为所属技术领域具有通常知识者所周知的技术,于此不再说明。

基于上述实施例可知,在上述半导体结构的制造方法中,通过热氧化制作工艺形成贯穿氧化物层116,而制作出SOI结构,因此可降低SOI结构的制作工艺复杂度与制造成本。此外,网状的图案化硬掩模层108可具有局部对称网格。因此,在形成贯穿氧化物层116时,网状的图案化硬掩模层108的局部对称网格可将突出部P两侧因氧化所产生的方向相反的应力相互抵消,以防止突出部P产生歪斜。

综上所述,上述实施例的半导体结构的制造方法可采用低制作工艺复杂度与低制造成本的方式制作出SOI结构,且能够防止突出部产生歪斜。

虽然结合以上实施例公开了本发明,然而其并非用以限定本发明,任何所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,可作些许的更动与润饰,故本发明的保护范围应当以附上的权利要求所界定的为准。

- 氮化物半导体结构、氮化物半导体发光元件、氮化物半导体晶体管元件、氮化物半导体结构的制造方法以及氮化物半导体元件的制造方法

- 用于制造腔结构、制造用于半导体结构的腔结构的方法和使用该方法制造的半导体传声器