一种降低DC输出低频纹波的装置

文献发布时间:2023-06-19 10:43:23

技术领域

本申请属于低频纹波抑制电路领域,特别涉及一种降低DC输出低频纹波的电源或源载装置。

背景技术

低频纹波是指叠加在输出直流稳定量上的交流分量,一般是由电网里100HZ工频交流信号引起的。为降低该工频纹波,常用的一种方法是加大输出低频滤波的电感,电容参数,使低频纹波降低到所需的指标。例如:通过输出纹波与输出电容的关系式:vripple=Imax/(Co×f)可以看出,加大输出电容值可以减小纹波,然而这种方法会影响开关电源的响应速度。另一种方法是采用隔直前馈修正电路,利用电容隔直的特性,把DC-DC输入信号里的Vac信号给提取出来,但是由于隔直电容所得到的Vac跟实际的输入Vin中的交流分量有相位的偏差,这种方法会影响前馈性能。

因此,希望有一种技术方案来克服或至少减轻现有技术的至少一个上述缺陷。

发明内容

本申请的目的是提供了一种降低DC输出低频纹波的装置,以解决现有技术存在的至少一个问题。

本申请的技术方案是:

一种降低DC输出低频纹波的装置,包括:

一DC-DC变换主功率电路,用以将其输入端的直流电压调整成其输出端的直流电压,

一前馈采样电路,其输入端与所述DC-DC变换主功率电路的输入端连接,得到DC-DC变换主功率电路的输入电压Vin,

一前馈电路,与所述前馈采样电路的输出端连接,提取所述DC-DC变换主功率电路的输入电压Vin中交流分量Vac,

一模数转换器,与所述前馈电路的输出端连接,用于将所述前馈电路提取的交流分量Vac的模拟量转换为数字量,

一数字信号处理单元,用于根据所述模数转换器输出的交流分量Vac数字量调整PWM占空比,从而控制所述DC-DC变换主功率电路的输出。

可选地,所述前馈电路提取的DC-DC变换主功率电路的输入电压Vin中交流分量Vac与所述前馈采样电路所得到DC-DC变换主功率电路的输入电压Vin中的交流分量相位相同。

可选地,所述数字信号处理单元用于根据Vdc信号和Vac信号计算得到前馈系数FFk=Vdc/(Vdc+Vac),调整控制DC-DC变换主功率电路的PWM占空比D=D1*FFk,其中,所述Vdc信号为所述DC-DC变换主功率电路的输入电压Vin的直流分量,D1为环路计算的占空比。

可选地,所述前馈采样电路具有Vin+输出端和Vin-输出端,所述前馈采样电路用于将所述DC-DC变换主功率电路的输入电压Vin转换为差分信号Vin+和Vin-;

所述前馈电路具有Vin+输入端和Vin-输入端,分别与所述前馈采样电路的Vin+输出端和Vin-输出端对应连接,所述前馈电路具有Vdc输出端和Vac输出端,所述前馈电路用于根据差分信号Vin+和Vin-获取Vdc信号和Vac信号;

所述数字信号处理单元具有AD1引脚和AD2引脚,分别与所述前馈电路的Vdc输出端和Vac输出端对应连接,所述数字信号处理单元具有PWM输出端,所述数字信号处理单元用于根据Vdc信号和Vac信号计算得到前馈系数FFk=Vdc/(Vdc+Vac),以及占空比D=D1*FFk,从而获取携带有占空比信息的PWM信号,D1为环路计算的占空比;

所述数字信号处理单元的PWM输出端连接PWM信号隔离电路的输入端,数字信号处理单元根据PWM信号隔离驱动所述DC-DC变换主功率电路中的开关管。

可选地,所述前馈电路包括第一运放单元、第二运放单元以及第三运放单元,其中,

所述第一运放单元的同相输入端作为Vin+输入端与所述前馈采样电路的Vin+输出端连接,所述第一运放单元的反相输入端作为Vin-输入端与所述前馈采样电路的Vin-输出端连接;

所述第二运放单元的同相输入端与所述第三运放单元的反向输入端和输出端连接,所述第二运放单元的反相输入端与所述第一运放单元的输出端连接,所述第二运放单元的输出端作为Vac输出端与所述数字信号处理单元的AD2引脚连接;

所述第三运放单元的同相输入端与所述第一运放单元的输出端连接,所述第三运放单元的反相输入端与所述第二运放单元的同相输入端连接,所述第三运放单元的输出端作为Vdc输出端与所述数字信号处理单元的AD1引脚连接。

可选地,所述前馈采样电路具有Vin+输出端和Vin-输出端,所述前馈采样电路用于将所述DC-DC变换主功率电路的输入电压Vin转换为差分信号Vin+和Vin-;

所述前馈电路具有Vin+输入端和Vin-输入端,分别与所述前馈采样电路的Vin+输出端和Vin-输出端对应连接,所述前馈电路具有Vac输出端,所述前馈电路用于根据差分信号Vin+和Vin-获取Vac信号;

所述数字信号处理单元具有AD2引脚,与所述前馈电路的Vac输出端对应连接,所述数字信号处理单元具有PWM输出端,所述数字信号处理单元用于根据Vdc值和Vac信号计算得到前馈系数FFk=Vdc/(Vdc+Vac),以及占空比D=D1*FFk,从而获取携带有占空比信息的PWM信号;其中,所述Vdc值为DSP内的定值,D1为环路计算的占空比;

所述数字信号处理单元的PWM输出端连接PWM信号隔离电路的输入端,数字信号处理单元根据PWM信号隔离驱动所述DC-DC变换主功率电路中的开关管。

可选地,所述前馈电路包括第一运放单元、第二运放单元以及第三运放单元,其中,

所述第一运放单元的同相输入端作为Vin+输入端与所述前馈采样电路的Vin+输出端连接,所述第一运放单元的反相输入端作为Vin-输入端与所述前馈采样电路的Vin-输出端连接;

所述第二运放单元的同相输入端与所述第三运放单元的反向输入端和输出端连接,所述第二运放单元的反相输入端与所述第一运放单元的输出端连接,所述第二运放单元的输出端作为Vac输出端与所述数字信号处理单元的AD2引脚连接;

所述第三运放单元的同相输入端与所述第一运放单元的输出端连接,所述第三运放单元的反相输入端与所述第二运放单元的同相输入端连接。

可选地,还包括第二电阻、第三电阻、第四电阻、第五电阻、第三电容以及第四电容,其中,

所述第二电阻的第一端作为Vin+输入端,所述第二电阻的第二端与所述第一运放单元的同相输入端连接;

所述第三电阻与所述第三电容并联后,第一端分别与所述第一运放单元的同相输入端、所述第二电阻的第二端连接,第二端与所述第一运放单元的输出端连接;

所述第四电阻与所述第四电容并联后,第一端分别与所述第一运放单元的反相输入端、所述第五电阻的第二端连接,第二端接地;

所述第五电阻的第一端作为Vin-输入端,所述第五电阻的第二端与所述第一运放单元的反相输入端连接。

可选地,还包括RC滤波组件,所述RC滤波组件包括第六电阻以及第五电容,其中,

所述第六电阻的第一端与所述第一运放单元的输出端连接,所述第六电阻的第二端与所述第三运放单元的同相输入端连接;

所述第五电容的第一端分别与所述第三运放单元的同相输入端、所述第六电阻的第二端连接,所述第五电容的第二端接地。

可选地,还包括第七电阻,所述第七电阻的第一端与所述第三运放单元的输出端连接,所述第七电阻的第二端作为Vdc输出端。

可选地,还包括第八电阻、第九电阻、第十电阻、第十一电阻以及第十二电阻,其中,

所述第八电阻的第一端分别与所述第三运放单元的反向输入端、所述第七电阻的第二端连接,所述第八电阻的第二端与所述第二运放单元的同相输入端连接;

所述第九电阻的第一端分别与所述第二运放单元的同相输入端、所述第八电阻的第二端连接,所述第九电阻的第二端与基准电压Vref连接;

所述第十电阻的第一端分别与所述第二运放单元的同相输入端、所述第八电阻的第二端连接,所述第十电阻的第二端接地;

所述第十一电阻的第一端分别与所述第一运放单元的输出端、所述第六电阻的第一端连接,所述第十一电阻的第二端与所述第二运放单元的反相输入端连接;

所述第十二电阻的第一端与所述第二运放单元的输出端连接,所述第十二电阻的第二端作为Vac输出端。

可选地,还包括第十三电阻以及第十四电阻,其中,

所述第十三电阻的第一端与所述第二运放单元的反向输入端、所述第十一电阻的第二端连接,所述第十三电阻的第二端与所述第十二电阻的第二端连接;

所述第十四电阻的第一端分别与所述第二运放单元的反向输入端、所述第十一电阻的第二端、所述第十三电阻的第一端连接,所述第十四电阻的第二端接地。

发明至少存在以下有益技术效果:

本申请的降低DC输出低频纹波的电源,能够完全真实还原DC-DC变换主功率电路输入电压Vin中的交流分量,从而有效的对PFC功率因数校正电路带来的100HZ的交流分量进行调制,能够在不影响整体的功率密度的情况下,有效减小DC输出的低频纹波。

附图说明

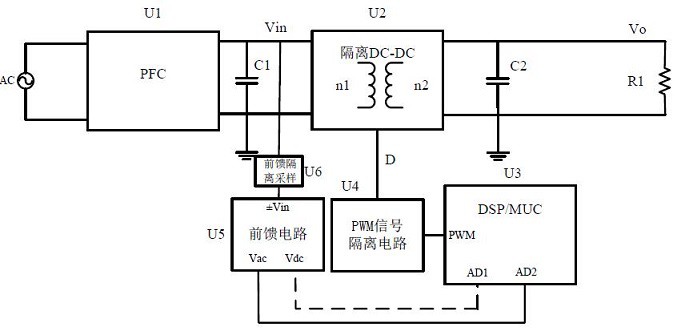

图1是本申请一个实施方式的降低DC输出低频纹波的电源示意图;

图2是本申请一个实施方式的前馈控制模块的前馈控制原理图;

图3是本申请一个实施方式的降低DC输出低频纹波的电源的前馈电路示意图。

具体实施方式

为使本申请实施的目的、技术方案和优点更加清楚,下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行更加详细的描述。在附图中,自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。所描述的实施例是本申请一部分实施例,而不是全部的实施例。下面通过参考附图描述的实施例是示例性的,旨在用于解释本申请,而不能理解为对本申请的限制。基于本申请中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。下面结合附图对本申请的实施例进行详细说明。

下面结合附图1至图3对本申请做进一步详细说明。

本实施例提供了一种降低DC输出低频纹波的电源,包括:PFC功率因数校正电路U1、DC-DC变换主功率电路U2以及前馈控制模块。

具体的,如图1所示,PFC功率因数校正电路U1的输入端与AC交流端连接;DC-DC变换主功率电路U2的输入端与PFC功率因数校正电路U1的输出端连接,DC-DC变换主功率电路U2的输出端与负载R1连接;前馈控制模块的输入端与DC-DC变换主功率电路U 2的输入端连接,前馈控制模块的输出端与DC-DC变换主功率电路U 2中的开关管连接,前馈控制模块用于根据DC-DC变换主功率电路U2的输入电压Vin获取PWM信号,并根据PWM信号隔离驱动DC-DC变换主功率电路U2中的开关管。

其中,上述负载R1指的是广义的负载,主要用于把DC-DC变换主功率电路的能量消耗掉或者转换成其他能量的模块。

在本申请的一个优选实施例中,还设置有第一电容C1以及第二电容C2,第一电容C1的第一端与PFC功率因数校正电路U1的输出端连接,第一电容C1的第二端接地,第一电容C1为PFC直流母线滤波电容,用来对PFC工频纹波和高频纹波进行平滑滤波。第二电容C2的第一端与DC-DC变换主功率电路U2的输出端连接,第二电容C2的第二端接地,第二电容C2作为DC-DC输出滤波电容。

在本申请的一个优选实施例中,前馈控制模块包括前馈隔离采样电路U6、前馈电路U5、数字信号处理单元U3(DSP/MUC)以及PWM信号隔离电路U4。本实施例中,前馈隔离采样电路U6的输入端与DC-DC变换主功率电路U2的输入端连接,前馈隔离采样电路U6具有Vin+输出端和Vin-输出端,前馈隔离采样电路U6用于将DC-DC变换主功率电路U2的输入电压Vin转换为差分信号Vin+和Vin-;前馈电路U5具有Vin+输入端和Vin-输入端,分别与前馈隔离采样电路的Vin+输出端和Vin-输出端对应连接,前馈电路U5具有Vdc输出端和Vac输出端,前馈电路U5用于根据差分信号Vin+和Vin-获取Vdc信号和Vac信号;数字信号处理单元U3具有AD1引脚和AD2引脚,分别与前馈电路的Vdc输出端和Vac输出端对应连接,数字信号处理单元U3具有PWM输出端,数字信号处理单元U3用于根据Vdc信号和Vac信号计算得到前馈系数FFk=Vdc/(Vdc+Vac),以及占空比D=D1*FFk,从而获取携带有占空比信息的PWM信号;PWM信号隔离电路U4的输入端与数字信号处理单元U3的PWM输出端连接,用于根据PWM信号隔离驱动DC-DC变换主功率电路U2中的开关管。

本申请的降低DC输出低频纹波的电源,如图2所示,分别通过前馈控制模块的前馈隔离采样电路U6以及前馈电路U5将DC-DC变换主功率电路U2的输入端Vin(FPC输出端)采样分解成直流分量Vdc以及交流分量Vac,数字信号处理单元U3得到Vdc和Vac后,计算出前馈系数FFk=Vdc/(Vdc+Vac),计算出结果D=D1*FFk修正最终环路输出的控制占空比D的量来控制PWM输出,从而调节实际输出电压值Vo。假设DC-DC变换主功率电路U2的变压器原边与副边的匝比为n1/n2,常规的电压模式控制法占空比计算公式:D1=(Vo/Vin)*(n1/n2),则采用本申请的前馈调节,计算的占空比D=(Vo/Vin)*(n1/n2)*FFk。D1为环路计算的占空比,D为加入前馈后最终控制的占空比。

在本申请的一个实施方式中,如图3所示,前馈电路U5包括第一运放单元OP1、第二运放单元OP2以及第三运放单元OP3,其中,第一运放单元OP1的同相输入端作为Vin+输入端与前馈隔离采样电路U6的Vin+输出端连接,第一运放单元OP1的反相输入端作为Vin-输入端与前馈隔离采样电路U6的Vin-输出端连接;第二运放单元OP2的同相输入端与第三运放单元OP3的反向输入端和输出端连接,第二运放单元OP2的反相输入端与第一运放单元OP1的输出端连接,第二运放单元OP2的输出端作为Vac输出端与数字信号处理单元U3的AD2引脚连接;第三运放单元OP3的同相输入端与第一运放单元OP1的输出端连接,第三运放单元OP3的反相输入端与第二运放单元OP2的同相输入端连接,第三运放单元OP3的输出端作为Vdc输出端与数字信号处理单元U3的AD1引脚连接。

本实施例中,还包括第二电阻R2、第三电阻R3、第四电阻R4、第五电阻R5、第三电容C3以及第四电容C4,其中,第二电阻R2的第一端作为Vin+输入端,第二电阻R2的第二端与第一运放单元OP1的同相输入端连接;第三电阻R3与第三电容C3并联后,第一端分别与第一运放单元OP1的同相输入端、第二电阻R2的第二端连接,第二端与第一运放单元OP1的输出端连接;第四电阻R4与第四电容C4并联后,第一端分别与第一运放单元OP1的反相输入端、第五电阻R5的第二端连接,第二端接地;第五电阻R5的第一端作为Vin-输入端,第五电阻R5的第二端与第一运放单元OP1的反相输入端连接。

有利的是,本实施例中,还包括RC滤波组件,RC滤波组件包括第六电阻R6以及第五电容C5,其中,第六电阻R6的第一端与第一运放单元OP1的输出端连接,第六电阻R6的第二端与第三运放单元OP3的同相输入端连接;第五电容C5的第一端分别与第三运放单元OP3的同相输入端、第六电阻R6的第二端连接,第五电容C5的第二端接地。本实施例中,还包括第七电阻R7,第七电阻R7的第一端与第三运放单元OP3的输出端连接,第七电阻R7的第二端作为Vdc输出端。

进一步,本实施例中,还包括第八电阻R8、第九电阻R9、第十电阻R10、第十一电阻R11以及第十二电阻R12,其中,第八电阻R8的第一端分别与第三运放单元OP3的反向输入端、第七电阻R7的第二端连接,第八电阻R8的第二端与第二运放单元OP2的同相输入端连接;第九电阻R9的第一端分别与第二运放单元OP2的同相输入端、第八电阻R8的第二端连接,第九电阻R9的第二端与基准电压Vref连接;第十电阻R10的第一端分别与第二运放单元OP2的同相输入端、第八电阻R8的第二端连接,第十电阻R10的第二端接地;第十一电阻R11的第一端分别与第一运放单元OP1的输出端、第六电阻R6的第一端连接,第十一电阻R11的第二端与第二运放单元OP2的反相输入端连接;第十二电阻R12的第一端与第二运放单元OP2的输出端连接,第十二电阻R12的第二端作为Vac输出端。本实施例中,还可以包括第十三电阻R13以及第十四电阻R14,其中,第十三电阻R13的第一端与第二运放单元OP2的反向输入端、第十一电阻R11的第二端连接,第十三电阻R13的第二端与第十二电阻R12的第二端连接;第十四电阻R14的第一端分别与第二运放单元OP2的反向输入端、第十一电阻R11的第二端、第十三电阻R13的第一端连接,第十四电阻R14的第二端接地。

本申请的降低DC输出低频纹波的电源,通过前馈隔离采样电路U6把DC-DC变换主功率电路U2的输入电压Vin转换为差分信号Vin+和Vin-,将Vin+和Vin-送入前馈电路U5中,前馈电路U5将输入信号Vin+和Vin-通过第一运放单元OP1放大后分别送入第二运放单元OP2和第三运放单元OP3中,第一运放单元OP1输出信号经过RC滤波后送入第三运放单元OP3得到Vdc信号并送入数字信号处理单元U3的AD1引脚,进行AD采样,第一运放单元OP1输出信号和第三运放单元OP3的输出信号作为第二运放单元OP2的输入,经过第二运放单元OP2放大信号后得到Vac信号(包括Vref的偏置量)送入数字信号处理单元U3的AD2引脚,进行AD采样。数字信号处理单元U3经过AD采样得到信号Vac和Vdc,计算得到前馈系数FFk=Vdc/(Vdc+Vac),以及占空比D=(Vo/Vin)*(n1/n2)*FFk,从而根据该占空比控制对应的PWM送入PWM信号隔离电路U4中进行隔离驱动DC-DC变换主功率电路U2中的开关管,进行输出控制。

本申请的另一个优选实施例,与上述优选实施例不同点仅在于第三运放单元OP3得到Vdc信号并不送入数字信号处理单元U3的AD1引脚进行AD采样,在预先知道DC-DC变换主功率电路的输入电压Vin的值大小且值不变的情况下,数字信号处理单元U3的前馈系数FFK计算公式中Vdc是可以根据Vin确定的一个定值来进行计算,不需要一直采样,或者,当Vdc稳定工作后是固定值,可以不做采集。

本实施例中,前馈控制模块包括前馈隔离采样电路、前馈电路、数字信号处理单元以及PWM信号隔离电路,其中,前馈隔离采样电路的输入端与DC-DC变换主功率电路的输入端连接,前馈隔离采样电路具有Vin+输出端和Vin-输出端,前馈隔离采样电路用于将DC-DC变换主功率电路的输入电压Vin转换为差分信号Vin+和Vin-;前馈电路具有Vin+输入端和Vin-输入端,分别与前馈隔离采样电路的Vin+输出端和Vin-输出端对应连接,前馈控制电路具有Vac输出端,前馈控制电路用于根据差分信号Vin+和Vin-获取Vac信号;数字信号处理单元具有AD2引脚,与前馈电路的Vac输出端对应连接,数字信号处理单元具有PWM输出端,数字信号处理单元用于根据Vdc值和Vac信号计算得到前馈系数FFk=Vdc/(Vdc+Vac),以及占空比D=D1*FFk,从而获取携带有占空比信息的PWM信号;其中,Vdc值为DSP内的一个定值;PWM信号隔离电路的输入端与数字信号处理单元的PWM输出端连接,用于根据PWM信号隔离驱动DC-DC变换主功率电路中的开关管。

进一步,本实施例中,前馈电路包括第一运放单元、第二运放单元以及第三运放单元,其中,第一运放单元的同相输入端作为Vin+输入端与前馈隔离采样电路的Vin+输出端连接,第一运放单元的反相输入端作为Vin-输入端与前馈隔离采样电路的Vin-输出端连接;第二运放单元的同相输入端与第三运放单元的反向输入端和输出端连接,第二运放单元的反相输入端与第一运放单元的输出端连接,第二运放单元的输出端作为Vac输出端与数字信号处理单元的AD2引脚连接;第三运放单元的同相输入端与第一运放单元的输出端连接,第三运放单元的反相输入端与第二运放单元的同相输入端连接。

本申请的降低DC输出低频纹波的电源,由于电路中未用到隔直电容,为了得到DC-DC变换主功率电路的输入电压Vin中交流分量Vac,只是对Vin进行了隔离采样,差分放大,所以采样后的Vac完全真实还原了Vin中的交流分量,从而有效的对PFC功率因数校正电路带来的100HZ的交流分量进行调制,能够在不影响整体的功率密度的情况下,有效减小DC输出的低频纹波。

以上实施例仅以电源为例,电源可以是单向电源、也可以是双向电源,在双向电源时亦可作为源载或电子负载装置,既可以吸收功率也可以供应功率。采样电路不限于隔离还是不隔离,以上隔离采样电路是优选实施例。本实施例中DC-DC变换主功率电路为隔离DC-DC,仅为优选实施例,在其他实施例中,DC-DC变换主功率电路也可以是非隔离DC-DC。本实施例中,数字信号处理单元集成有模数转换器,在其他实施例中,模数转换器也可以独立于数字信号处理单元,数字信号处理也不限于数字信号处理器DSP,也可以是其它的MCU等作为信号处理单元。

以上所述,仅为本申请的具体实施方式,但本申请的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本申请揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本申请的保护范围之内。因此,本申请的保护范围应以所述权利要求的保护范围为准。

- 一种降低DC输出低频纹波的装置

- 一种降低纹波输出的双向DC-DC宽电压调制电路