存储器数据存取装置及其方法

文献发布时间:2023-06-19 11:29:13

技术领域

本发明涉及一种存储器数据存取装置及其方法,尤其是关于一种与高速缓存相关之存储器数据存取装置及其方法。

背景技术

在现有计算机架构中,高速缓存器(Cache Memory)主要设置于处理单元与一般存储器(例如:随机存取存储器)之间。当处理单元执行存储器读取指令时,可先至存取速度较快之高速缓存器中搜寻是否有相应之数据。若是,处理单元便可直接于高速缓存器中读取所需数据,换言之,处理单元无需至存取速度较慢之一般存储器中读取所需数据,以节省读取时间。若否,处理单元便需至存取速度较慢之一般存储器中读取所需数据。

考虑到高速缓存器成本较高,储存空间相对有限,因此,高速缓存器之使用方式及其储存之内容须妥善配置,方能提升整体存取效率。

发明内容

本发明的目的在于提供一种存储器数据存取方法,包括:执行存储器读取指令,其中,存储器读取指令包括存储器地址;判断在对高速缓存器的读取中未命中存储器地址;判断存储器地址位于存储器地址范围内,其中,存储器地址范围对应数据存取量;以及自存储器的存储器地址,读取对应于数据存取量之数据块。

本发明另提供一种存储器数据存取装置,包括高速缓存器以及处理单元。处理单元用以:执行存储器读取指令,其中,存储器读取指令包括存储器地址;判断在对高速缓存器之读取中未命中存储器地址;判断存储器地址位于存储器地址范围内,其中,存储器地址范围对应数据存取量;以及自存储器的该存储器地址,读取对应于数据存取量的数据块。

附图说明

结合附图阅读以下详细描述会最佳地理解本发明构思。应注意,各种特征可能未按比例绘制。事实上,可出于论述清楚起见,而任意地增大或减小各种特征之尺寸。

图1A为本发明之一些实施例之存储器数据存取装置之方块图。

图1B为本发明之一些实施例之存储器数据存取装置之方块图。

图1C为本发明之一些实施例之缓存器之示意图。

图1D为本发明之一些实施例之高速缓存器之高速缓存通路之示意图。

图1E至图1G为本发明之一些实施例之高速缓存器之使用示意图。

图2A为本发明之一些实施例之缓存器及高速缓存器之示意图。

图2B至图2F为本发明之一些实施例之缓存器及高速缓存器之使用示意图。

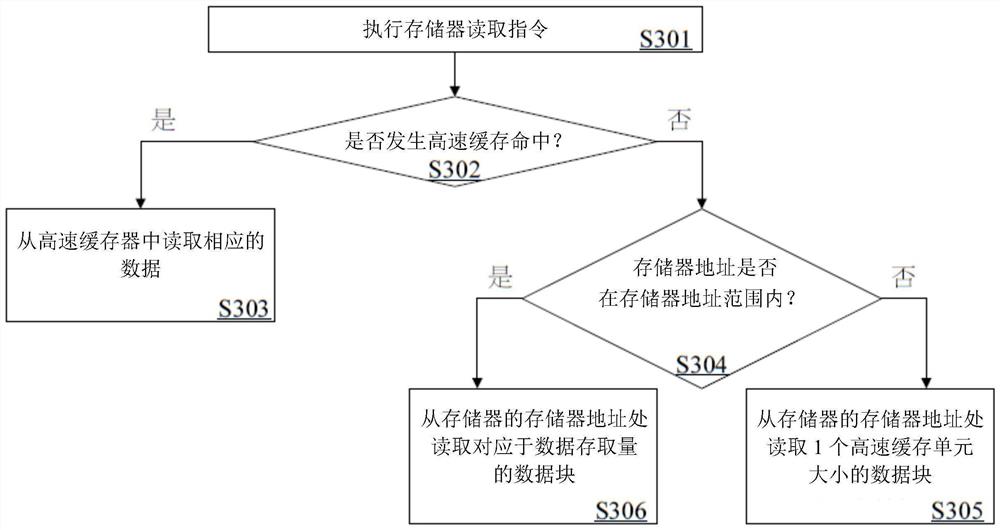

图3为本发明之一些实施例之存储器数据存取方法之流程图。

图4A至图4B为本发明之一些实施例之存储器数据存取方法之流程图。

具体实施方式

在下文更详细地论述本发明之实施例。然而,应了解,本发明提供可在多种特定情境中体现的许多适用的概念。所论述特定实施例仅为说明性的且并不限制本发明之范围。

在现有技术中,当高速缓存器之读取发生未命中(Cache Miss)时,将从一般存储器中读取固定大小之数据,使用上弹性较低。本发明提供一种存储器数据存取装置及方法,可依据需要动态地对一般存储器中所需读取数据之大小进行调整,以大幅地提升使用弹性。

请参阅图1A,其系本发明一些实施例之一存储器数据存取装置10之方块图。存储器数据存取装置10包括处理单元101以及高速缓存器103。在一些实施例中,处理单元101与高速缓存器103电连接,用以传递数据及信号。在一些实施例中,存储器数据存取装置10与存储器90电连接,用以传递数据及信号。相关存储器数据存取操作将于下文中进一步阐述。

具体而言,当处理单元101需要对存储器90中的数据进行存取时,处理单元101执行存储器读取指令100。其中,存储器读取指令100包括存储器地址ADDR。接着,在对存储器90进行存取前,处理单元101先判断存取速度较快之高速缓存器103中,是否具有相应于存储器地址ADDR之数据。若有,代表高速缓存器103之存取发生高速缓存命中(Cache Hit),则处理单元101直接从高速缓存器103中读取相应于存储器地址ADDR之数据。

另一方面,若处理单元101判断高速缓存器103中不具有相应于存储器地址ADDR之数据,代表高速缓存器103之存取发生高速缓存未命中(Cache Miss),换言之,即处理单元101判断在对高速缓存器的读取中未命中存储器地址ADDR,则处理单元101需进一步对存储器90进行读取操作。

详细来说,处理单元101先判断存储器地址ADDR是否位于存储器地址范围RAG内。若否,处理单元101将直接从存储器90之存储器地址ADDR处,读取一个高速缓存单元(CacheLine)大小的数据块DB,并将其写入至高速缓存器103中,以便处理单元101后续从高速缓存器103中存取与存储器地址ADDR相对应的数据。

另一方面,存储器地址范围RAG对应数据存取量AMT,若处理单元101判断存储器地址ADDR位于存储器地址范围内,处理单元101将从存储器90的存储器地址ADDR处,读取对应于数据存取量AMT之数据块DB,并将数据块DB写入至高速缓存器103中。在一些实施例中,数据存取量AMT为高速缓存单元大小之至少二倍。

在一些实施例中,存储器地址范围RAG及其对应之数据存取量AMT是预先设定的,并储存于至少一个缓存器中。请一并参考图1B,在一些实施例中,存储器数据存取装置10还包括电连接到处理单元101的缓存器101a以及缓存器101b。缓存器101a用以储存存储器地址范围RAG,缓存器101b用以储存数据存取量AMT。

请一并参考图1C,在一些实施例中,缓存器101a储存多组存储器地址范围RAG_1至RAG_N,缓存器101b储存多组数据存取量AMT_1至AMT_N。其中,多组存储器地址范围RAG_1至RAG_N与多组数据存取量AMT_1至AMT_N一一对应。据此,当处理单元101判断存储器地址ADDR落于存储器地址范围RAG_1至RAG_N时,处理单元101将从存储器90之存储器地址ADDR处,读取对应于数据存取量AMT_n之数据块DB。

在一些实施例中,将数据块DB写入至高速缓存器103还可以包括更详细之操作。请一并参考图1D,其系本发明一些实施例之高速缓存器103之高速缓存通路(Cache Way)示意图。其中,高速缓存器103包括多个高速缓存通路TAG_a至TAG_d,每个高速缓存通路具有0至7的字段。

当处理单元101判断存储器地址ADDR位于存储器地址范围RAG内时,处理单元101从多个高速缓存通路TAG_a至TAG_d中挑选高速缓存通路(例如:高速缓存通路TAG_b)。同时,处理单元101将数据块DB分为多个单元数据(Line Data)DB_1至DB_3。其中,每个单元数据之大小与高速缓存单元之大小相同,且单元数据DB_1至DB_3具有对应的存储器地址ADDR_1至ADDR_3。

接着,处理单元101依序判断是否将单元数据DB_1至DB_3写入高速缓存器103。详言之,针对每个单元数据,处理单元101判断对应的存储器地址是否储存于高速缓存器103中的任一高速缓存通路中。若否,则处理单元101将对应的存储器地址写入至所挑选之高速缓存通路,并将此单元数据写入至高速缓存器103中相应之位置。

若处理单元101判断对应的存储器地址储存于高速缓存器103中的某一高速缓存通路中,则处理单元101进一步判断对应的存储器地址是否储存于所挑选之高速缓存通路中。若是,则处理单元101丢弃此单元数据。若否,则处理单元101先从高速缓存器103中清除相应的高速缓存数据。接着,处理单元101将对应的存储器地址写入至所挑选之高速缓存通路中,并将此单元数据写入至高速缓存器103中相应之位置。

举例而言,请参考图1E,针对单元数据DB_1,处理单元101判断对应的存储器地址ADDR_1未储存于高速缓存器103之高速缓存通路中。因此,处理单元101将对应的存储器地址ADDR_1写入至所挑选之高速缓存通路中,并将单元数据DB_1写入至高速缓存器103中相应之位置。

举例而言,请参考图1F,针对单元数据DB_2,处理单元101判断对应之存储器地址ADDR_2储存于高速缓存器103之高速缓存通路中。因此,处理单元101进一步判断对应之存储器地址ADDR_2储存于所挑选之高速缓存通路中。据此,处理单元101丢弃单元数据DB_2。

举例而言,请参考图1G,针对单元数据DB_3,处理单元101判断对应之存储器地址ADDR_3储存于高速缓存器103之高速缓存通路中。因此,处理单元101进一步判断对应之存储器地址ADDR_3未储存于所挑选之高速缓存通路中。据此,处理单元101先从高速缓存器103中清除相应之高速缓存单元数据。接着,处理单元101将对应之存储器地址ADDR_3写入至所挑选之高速缓存通路中,并将单元数据DB_3写入至高速缓存器103中相应之位置。

以下将透过其他示例及示图,更为完整地例示本发明将数据块写入至高速缓存器之操作。请参考图2A,其系本发明之缓存器及高速缓存器之示意图。缓存器A储存存储器地址范围:0x2000至0x3ffff以及0x5000至0x6ffff,缓存器B储存数据存取量:2个高速缓存单元以及3个高速缓存单元。其中,存储器地址范围0x2000至0x3ffff对应数据存取量为2个高速缓存单元,存储器地址范围0x5000至0x6ffff对应数据存取量为3个高速缓存单元。

另一方面,高速缓存器C包括多个高速缓存通路Way-0至Way-3,每个高速缓存通路具有0至7的字段。其中,如图所示,高速缓存通路Way-0至Way-3已储存有多个存储器地址2000、8060、A080、51A0以及20C0。须说明,前述高速缓存通路所记录之存储器地址在高速缓存器C的其他部分具有相应的数据,为便于理解本发明之技术,并未绘出,但本领域技术人员应理解这一点。

请参考图2B,存储器读取指令包括存储器地址0x7040,处理单元判断存储器地址0x7040未位于存储器地址范围0x2000至0x3ffff或0x5000至0x6ffff间。据此,处理单元从存储器之存储器地址0x7040处,读取一个高速缓存单元大小之数据块。接着,处理单元挑选Way-1,并将对应之存储器地址0x7040写入至Way-1。同时,处理单元将相应于存储器地址0x7040之数据块写入至高速缓存器。

请参考图2C,存储器读取指令包括存储器地址0x2040,处理单元判断存储器地址0x2040位于存储器地址范围0x2000至0x3ffff间。据此,处理单元于存储器之存储器地址0x2040处,读取数据存取量为2个高速缓存单元大小之数据块。此数据块可分为起始地址为0x2040且大小为1个高速缓存单元之数据,以及起始地址为0x2060且大小为1个高速缓存单元之数据。

接着,处理单元挑选Way-0,并将对应之存储器地址0x2040写入至Way-0。同时,处理单元将相应于存储器地址0x2040之数据块写入至高速缓存器。随后,处理单元判断存储器地址0x2060并未存在于高速缓存器之任一高速缓存通路中,因此,处理单元将对应之存储器地址0x2060写入至Way-0。同时,处理单元将相应于存储器地址0x2060之数据块写入至高速缓存器。

请参考图2D,存储器读取指令包括存储器地址0x5000,处理单元判断存储器地址0x5000位于存储器地址范围0x5000至0x6ffff间。据此,处理单元从存储器之存储器地址0x5000处,读取数据存取量为3个高速缓存单元大小之数据块。此数据块可分为起始地址为0x5000且大小为1个高速缓存单元之数据、起始地址为0x5020且大小为1个高速缓存单元之数据以及起始地址为0x5040且大小为1个高速缓存单元之数据。

接着,处理单元挑选Way-2,并将对应之存储器地址0x5000写入至Way-2。同时,处理单元将相应于存储器地址0x5000之数据块写入至高速缓存器。随后,处理单元判断存储器地址0x5020并未存在于高速缓存器之任一高速缓存通路中,因此,处理单元将对应之存储器地址0x5020写入至Way-2。同时,处理单元将相应于存储器地址0x5020之数据块写入至高速缓存器。

接着,处理单元判断存储器地址0x5040并未存在于高速缓存器之任一高速缓存通路中,因此,处理单元将对应之存储器地址0x5040写入至Way-2。同时,处理单元将相应于存储器地址0x5040之数据块写入至高速缓存器。

请参考图2E,存储器读取指令包括存储器地址0x20A0,处理单元判断存储器地址0x20A0位于存储器地址范围0x2000至0x3ffff间。据此,处理单元于存储器之存储器地址0x20A0处,读取数据存取量为2个高速缓存单元大小之数据块。此数据块可分为起始地址为0x20A0且大小为1个高速缓存单元之数据,以及起始地址为0x20C0且大小为1个高速缓存单元之数据。

接着,处理单元挑选Way-2,并将对应之存储器地址0x20A0写入至Way-2。同时,处理单元将相应于存储器地址0x20A0之数据块写入至高速缓存器。随后,处理单元判断存储器地址0x20C0存在于高速缓存器之高速缓存通路Way-2中,因此,处理单元不再将存储器地址0x20C0重复写入至Way-2。同时,处理单元将相应于存储器地址0x20C0之数据块丢弃。

请参考图2F,存储器读取指令包括存储器地址0x5180,处理单元判断存储器地址0x5180位于存储器地址范围0x5000至0x6ffff间。据此,处理单元于存储器之存储器地址0x5180处,读取数据存取量为3个高速缓存单元大小之数据块。此数据块可分为起始地址为0x5180且大小为1个高速缓存单元之数据、起始地址为0x51A0且大小为1个高速缓存单元之数据以及起始地址为0x51C0且大小为1个高速缓存单元之数据。

接着,处理单元挑选高速缓存通路Way-3,并将对应之存储器地址0x5180写入至Way-3。同时,处理单元将相应于存储器地址0x5180之数据块写入至高速缓存器。随后,处理单元判断存储器地址0x51A0存在于高速缓存器之高速缓存通路Way-0中,接着,处理单元再进一步判断挑选之高速缓存通路Way-3与存储器地址0x51A0存在于高速缓存器之高速缓存通路Way-0不同后,清除高速缓存通路Way-0中之存储器地址0x51A0,并清除相应之高速缓存单元数据。接着,处理单元将对应之存储器地址0x51A0写入至Way-3。同时,处理单元将相应于存储器地址0x51A0之数据块写入至高速缓存器。

随后,处理单元判断存储器地址0x51C0并未存在于高速缓存器之任一高速缓存通路中,因此,处理单元将对应之存储器地址0x51C0写入至Way-2。同时,处理单元将相应于存储器地址0x51C0之数据块写入至高速缓存器。

本发明之一些实施例包括存储器数据存取方法,其流程图如图3所示。这些实施例之存储器数据存取方法由存储器数据存取装置(如前述实施例之存储器数据存取装置10)实施。方法之详细操作如下。

首先,执行步骤S301,执行存储器读取指令。其中,存储器读取指令包括存储器地址。接着,执行步骤S302,判断在对高速缓存器之读取中是否命中存储器地址。若命中,则执行步骤S303,于高速缓存器中读取相应之数据。若未命中,则执行步骤S304,判断存储器地址是否位于存储器地址范围内。其中,存储器地址范围对应数据存取量。

若存储器地址未位于存储器地址范围内,则执行步骤S305,自存储器之存储器地址读取一个高速缓存单元大小之数据块。若存储器地址位于存储器地址范围内,则执行步骤S306,自存储器之存储器地址读取对应于数据存取量之数据块。

本发明之一些实施例包括存储器数据存取方法,其流程图如图4A至4B所示。这些实施例之存储器数据存取方法由存储器数据存取装置(如前述实施例之存储器数据存取装置10)实施。方法之详细操作如下。

首先,执行步骤S401,执行存储器读取指令。其中,存储器读取指令包括存储器地址。接着,执行步骤S402,判断在对高速缓存器之读取中是否命中存储器地址。若命中,则执行步骤S403,于高速缓存器中读取相应之数据。若未命中,则执行步骤S404,判断存储器地址是否位于存储器地址范围内。其中,存储器地址范围对应数据存取量。

若存储器地址未位于存储器地址范围内,则执行步骤S405,自存储器之存储器地址读取一个高速缓存单元大小之数据块。执行步骤S407,将此数据块写入至高速缓存器。若存储器地址位于存储器地址范围内,则执行步骤S406,自存储器之存储器地址读取对应于数据存取量之数据块。执行步骤S407,将此数据块写入至高速缓存器。

在一些实施例中,步骤S407可进一步分为图4B之操作。详言之,执行步骤S407a,自高速缓存器之多个高速缓存通路中挑选用于储存数据之高速缓存通路。执行步骤S407b,将数据块分为多个单元数据。其中,每个单元数据之大小与高速缓存单元之大小相同。

针对每个单元数据,执行步骤S407c,判断此单元数据是否储存于高速缓存器,换言之,即是否与高速缓存器中之某一高速缓存单元数据相符。若否,则执行步骤S407d,将此单元数据写入至挑选之高速缓存器之高速缓存通路,并针对下一个单元数据重复执行步骤S407c。若是,执行步骤407e,判断此单元数据是否储存于所挑选之高速缓存器之高速缓存通路。

若判断此单元数据储存于所挑选之高速缓存器之高速缓存通路,执行步骤S407f,丢弃此单元数据,并针对下一个单元数据重复执行步骤S407c。若判断此单元数据储存于高速缓存器之其他高速缓存通路,执行步骤S407g,清除高速缓存器中相应于此单元数据之高速缓存单元数据。接着,执行步骤S407d,将此单元数据写入至挑选之高速缓存器之高速缓存通路,并针对下一个单元数据重复执行步骤S407c。重复执行步骤S407c至步骤S407g至到处理完所有单元数据。

须说明,在一些实施例中,前述存储器数据存取装置中的处理单元包括中央处理单元(Central Processing Unit,CPU)等可执行运算及指令之逻辑电路,相较于高速缓存器,一般存储器包括速度较慢之随机存取存储器(Random Access Memory,RAM),但本发明硬件组件的实现方式不限于此。

在一些实施例中,高速缓存器包括一级高速缓存器(L1 Cache memory)。在一些实施例中,高速缓存器包括二级高速缓存器(L2 Cache memory)。在一些实施例中,缓存器可为处理单元内置缓存器,但本发明硬件组件的实现方式不限于此。

上文的叙述简要地描述了本发明某些实施例之特征,从而使得本发明所属技术领域的普通技术人员能够更全面地理解本发明内容的多种情况。本发明所属技术领域的普通技术人员当理解,可容易地利用本发明内容为基础,来设计或更改其他制程与结构,以实现与本文所公开的实施方式相同的目的和/或达到相同的优点。本发明所属技术领域的普通技术人员应当明白,这些均等的实施方式仍包含在本发明内容之精神与范围内,且可对其进行各种变更、替代与更改变,而不会悖离本发明内容之精神与范围。

附图标记说明:

10:存储器数据存取装置

100:存储器读取指令

101:处理单元

101a:缓存器

101b:缓存器

103:高速缓存器

90:存储器

A~B:缓存器

C:高速缓存器

ADDR:存储器地址

ADDR_1~ADDR_3:存储器地址

AMT:数据存取量

AMT_1~AMT_N:资料存取量

DB:数据块

DB_1至DB_3:单元数据

RAG:存储器地址范围

RAG_1~RAG_N:存储器地址范围

TAG_a~TAG_d 高速缓存通路

Way-0~Way-3 高速缓存通路

S301~S306 步骤

S401~S407g 步骤

- 数据存取方法、存储器储存装置与存储器控制电路单元

- 数据存取方法、存储器控制电路单元及存储器存储装置