柔性类CMOS反相器及其制备方法

文献发布时间:2023-06-19 12:02:28

技术领域

本发明涉及柔性电子器件技术领域,尤其涉及一种柔性类CMOS(ComplementaryMetal-Oxide-Semiconductor,互补金属氧化物半导体)反相器及其制备方法。

背景技术

随着电子信息技术的发展,对柔性电子器件尤其是可穿戴电子器件提出了迫切的需求。而在柔性基底上得到稳定的薄膜晶体管(Thin Film Transistor,TFT)是柔性电子器件应用在集成电路领域的前提。非晶态铟镓锌氧化物(a-IGZO)作为金属氧化物半导体的代表材料,有迁移率高,稳定性好,大面积均一性好,可在柔性基底上制备(制备温度低)以及透明度高(带隙宽,对可见光的透过性好)等优点,被广泛用于显示领域以及集成电路领域。

在集成电路领域中,金属氧化物半导体一般被用来构筑互补型金属氧化物半导体(CMOS)逻辑器件。然而,由于在价带附近存在着高密度的电子阱,大多数金属氧化物半导体材料呈现出n型半导体的特性,只有少数呈现出p型或双极半导体的特性,这极大地限制了它们在CMOS逻辑电路中的应用。与金属氧化物半导体相反,大多数有机材料表现出本征的p型半导体特性,并且具有柔性,易于合成和种类众多等优点,可用来被构筑有机-无机异质结。

为了探索在逻辑电路中的潜在应用前景,n型金属氧化物材料被用来与p型有机材料结合制备双极晶体管,进而构筑类CMOS(CMOS-like)逻辑器件。

相关技术中,在柔性基底上通过碳纳米管来构筑类CMOS反相器,但是碳纳米管还需要选择性的掺杂,额外增加了工艺的复杂度及器件的不稳定性。

发明内容

本发明提供一种柔性类CMOS反相器及其制备方法,用以解决现有技术中在柔性基底上通过碳纳米管来构筑类CMOS反相器需要选择性的掺杂而造成工艺复杂且器件不稳定的缺陷。

本发明提供一种柔性类CMOS反相器的制备方法,包括:

提供柔性基底;

在所述柔性基底上形成保护层;

在所述保护层上制备栅电极;

在所述保护层和所述栅电极上沉积介电层;

在所述介电层上形成第一沟道层,所述第一沟道层的材料为无机材料;

在所述第一沟道层上制备源电极和漏电极;

在所述第一沟道层、所述源电极和所述漏电极上形成第二沟道层,所述第二沟道层的材料为有机材料;

其中,所述栅电极、所述介电层、所述第一沟道层、所述源电极和所述漏电极通过光刻进行图案化。

根据本发明提供的柔性类CMOS反相器的制备方法,提供柔性基底,包括:

提供玻璃基底;

在所述玻璃基底上依次旋涂聚二甲基硅氧烷和聚酰亚胺生成所述柔性基底。

根据本发明提供的柔性类CMOS反相器的制备方法,在所述柔性基底上形成保护层,包括:

在所述柔性基底上通过原子层沉积的方式沉积Al

根据本发明提供的柔性类CMOS反相器的制备方法,在所述保护层上制备栅电极,包括:

在所述保护层上通过电子束蒸镀制备所述栅电极。

根据本发明提供的柔性类CMOS反相器的制备方法,在所述保护层和所述栅电极上沉积介电层,包括:

在所述保护层和所述栅电极上通过等离子体增强化学气相沉积法沉积SiO

根据本发明提供的柔性类CMOS反相器的制备方法,在所述介电层上形成第一沟道层,包括:

在所述介电层上通过磁控溅射形成所述第一沟道层,所述第一沟道层为a-IGZO沟道层。

根据本发明提供的柔性类CMOS反相器的制备方法,在所述第一沟道层、所述源电极和所述漏电极上形成第二沟道层,包括:

在所述第一沟道层、所述源电极和所述漏电极上通过热蒸镀C8-BTBT(2,7-二辛基[1]苯并噻吩并[3,2-B]苯并噻吩)形成所述第二沟道层。

本发明提供的柔性类CMOS反相器及其制备方法,提供了粗糙度低的柔性基底,然后通过在柔性基底上依次形成保护层、栅电极、介电层、无机的第一沟道层、源电极和漏电极,以及有机的第二沟道层,最终通过制备有机-无机异质结双极晶体管来构筑了柔性类CMOS反相器。

附图说明

为了更清楚地说明本发明或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

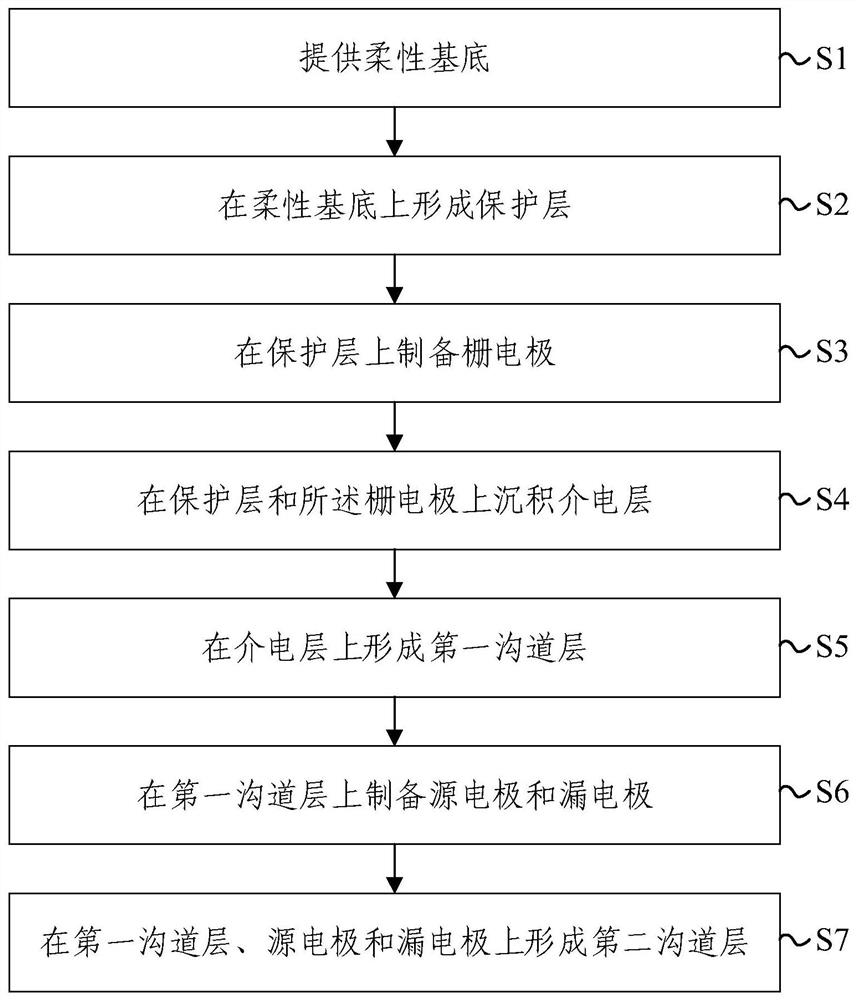

图1是本发明提供的柔性类CMOS反相器的制备方法的流程示意图;

图2-图8为本发明的柔性类CMOS反相器的制备过程示意图;

图9为本发明一个示例中柔性类CMOS反相器在电子增强模式下的电压转移曲线图;

图10为本发明一个示例中柔性类CMOS反相器在电子增强模式下的电压增益曲线图;

图11为本发明一个示例中柔性类CMOS反相器在空穴增强模式下的电压转移曲线图;

图12为本发明一个示例中柔性类CMOS反相器在空穴增强模式下的电压增益曲线图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明中的附图,对本发明中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

应理解,说明书通篇中提到的“实施例”或“一个实施例”意味着与实施例有关的特定特征、结构或特性包括在本发明的至少一个实施例中。因此,在整个说明书各处出现的“实施例中”或“在一个实施例中”未必一定指相同的实施例。此外,这些特定的特征、结构或特性可以任意适合的方式结合在一个或多个实施例中。

在本发明的描述中,需要理解的是,术语“第一”和“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性。

在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“连接”应做广义理解,例如,可以是直接相连,也可以通过中间媒介间接相连。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

下面结合附图描述本发明的柔性类CMOS反相器的制备方法。

图1是本发明提供的柔性类CMOS反相器的制备方法的流程示意图。如图1所示,本发明提供的柔性类CMOS反相器的制备方法,包括:

S1:提供柔性基底。

如图2所示,在玻璃基底之上,首先通过旋涂仪旋涂聚二甲基硅氧烷(Polydimethylsiloxane,PDMS)作为缓冲层。旋涂仪的动作过程包括滴胶,高速旋转以及干燥。滴胶步骤把PDMS滴注到玻璃基底表面上,高速旋转把PDMS铺展到玻璃基底上形成簿层,干燥步骤除去PDMS层中多余的溶剂。两种常用的滴胶方式是静态滴胶和动态滴胶。静态滴胶就是简单地把光刻胶滴注到静止的基片表面的中心。动态滴胶方式是在玻璃基底低速(通常在500转/分左右)旋转的同时进行滴胶,“动态”的作用是让光刻胶容易在玻璃基底上铺展开,减少光刻胶的浪费,采用动态滴胶不需要很多光刻胶就能润湿(铺展覆盖)整个玻璃基底表面。尤其是当光刻胶或玻璃基底本身润湿性不好的情况下,动态滴胶尤其适用,不会产生针孔。

本实施例采用动态滴胶,PDMS旋涂速度为3000r/min,旋涂时间为1min,厚度为7-8μm。在缓冲层上旋涂聚酰亚胺(Polyimide,PI)后得到柔性基底,聚酰亚胺具有耐高温的优点。在本实施例中,PI旋涂速度为4000r/min,旋涂时间为1min,厚度为1.2μm。

S2:在柔性基底上形成保护层。

如图3所示,在柔性基底上通过原子层沉积的方式沉积Al

S3:在保护层上制备栅电极。

如图4所示,在保护层上通过电子束蒸镀制备栅电极。电子束蒸镀利用电磁场的配合可以精准地实现利用高能电子轰击坩埚内靶材,使之融化进而沉积在保护层上。本发明采用电子束蒸镀可以得到能量密度极高的栅电极。

S4:在保护层和栅电极上沉积介电层。

如图5所示,在保护层和栅电极上通过等离子体增强化学气相沉积法(PlasmaEnhanced Chemical Vapor Deposition,PECVD)沉积SiO

S5:在介电层上形成第一沟道层。第一沟道层的材料为无机材料。

如图6所示,在介电层上通过磁控溅射形成第一沟道层。其中,磁控溅射具有设备简单、易于控制、镀膜面积大和附着力强、高速、低温和低损伤优点。磁控溅射的工作原理是指电子在电场E的作用下,在飞向介电层过程中与氩原子发生碰撞,使其电离产生出Ar正离子和新的电子;新电子飞向介电层,Ar离子在电场作用下加速飞向阴极靶,并以高能量轰击靶表面,使靶材发生溅射。在溅射粒子中,中性的靶原子或分子沉积在基片上形成薄膜,而产生的二次电子会受到电场和磁场作用,产生E(电场)×B(磁场)所指的方向漂移,简称E×B漂移,其运动轨迹近似于一条摆线。若为环形磁场,则电子就以近似摆线形式在靶表面做圆周运动,它们的运动路径不仅很长,而且被束缚在靠近靶表面的等离子体区域内,并且在该区域中电离出大量的Ar来轰击靶材,从而实现了高的沉积速率。随着碰撞次数的增加,二次电子的能量消耗殆尽,逐渐远离靶表面,并在电场E的作用下最终沉积在介电层上。由于该电子的能量很低,传递给介电层的能量很小,致使介电层温升较低。

在本实施例中,第一沟道层为a-IGZO沟道层。a-IGZO作为金属氧化物半导体的代表材料,有迁移率高、稳定性好、大面积均一性好和透明度高的优点。磁控溅射生长a-IGZO的过程中,溅射时间为600s,功率为80W,溅射舱内氩气与氧气流量分别为24sccm,1sccm,溅射得到的a-IGZO厚度为20nm。

S6:在第一沟道层上制备源电极和漏电极。

如图7所示,在第一沟道层上通过电子束蒸镀制备源电极和漏电极。其中,栅电极、介电层、第一沟道层、源电极和漏电极通过光刻进行图案化。在本实施例中,光刻后得到器件的长宽比为1:2,光刻后得到的a-IGZO TFT阵列。

S7:在第一沟道层、源电极和漏电极上形成第二沟道层。其中,第二沟道层的材料为有机材料。

如图8所示,在第一沟道层、源电极和漏电极上通过热蒸镀C8-BTBT形成第二沟道层。在本实施例中,蒸镀温度为109℃,蒸镀速度为0.02nm/s,厚度为100nm。

图9为本发明一个示例中柔性类CMOS反相器在电子增强模式下的电压转移曲线图;图10为本发明一个示例中柔性类CMOS反相器在电子增强模式下的电压增益曲线图;图11为本发明一个示例中柔性类CMOS反相器在空穴增强模式下的电压转移曲线图;图12为本发明一个示例中柔性类CMOS反相器在空穴增强模式下的电压增益曲线图。如图9-图12所示,从电压转移曲线可得,制备的类CMOS反相器其既可以工作在第一象限也可工作在第三象限。

此外,本发明还提供一种柔性类CMOS反相器,由上述的柔性类CMOS反相器的制备方法制备而成。

需要说明的是,本发明实施例的柔性类CMOS反相器的其它构成以及作用对于本领域的技术人员而言都是已知的,为了减少冗余,不做赘述。

最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

- 柔性类CMOS反相器及其制备方法

- CMOS反相器及应用该CMOS反相器的电子装置