封装结构及其制造方法、光子集成电路芯片

文献发布时间:2024-04-18 19:48:15

技术领域

本发明涉及半导体领域,更为具体而言,涉及一种封装结构及其制造方法、光子集成电路芯片。

背景技术

在光子集成电路中,有时需要将光耦合入光子集成电路,使得光在光子集成电路中传输、或者输入光子集成电路中的光子器件。在光子集成电路中通常设置有耦合结构或者耦合器件,以实现光的输入。制造合适的光子集成电路,以提高光的耦合效率,减少光在光耦合过程中的损失十分重要。

在对光子集成电路进行封装时,基于电连接的需要,一些场景中希望在光子集成电路中形成贯穿材料层以及贯穿衬底的导电结构。

在光子集成电路的生长衬底形成过孔时,目前仍然存在一些挑战,例如其工艺本身可能并不成熟,或者会因为工艺等原因对光子电路中的器件产生影响。

发明内容

本发明提供了一种封装结构及其制造方法、一种光子集成电路芯片。

在一个示例性的实施方式中,提出一种封装结构的制造方法,包括:提供光子集成结构,所述光子集成结构包括光栅耦合器,以及反射层,其中,所述反射层与所述光栅耦合器对应;提供第一衬底;以及将所述光子集成结构与所述第一衬底键合,在所述键合之后,所述反射层位于所述光栅耦合器与所述第一衬底之间。

示例性的,在所述提供光子集成结构的步骤中,被提供的所述光子集成结构包括第一介电层;所述提供光子集成结构的步骤包括:基于SOI衬底形成所述光子集成结构,其中,所述SOI衬底包括背衬底、绝缘层以及顶层硅,所述第一介电层来自SOI衬底中的绝缘层;去除所述背衬底;以及,在去除背衬底之后,在所述第一介电层背离所述光栅耦合器的一侧形成所述反射层。

示例性的,在所述第一介电层中设置有用于容纳反射层的开孔,在所述容纳反射层的开孔中设置所述反射层。

示例性的,其中,所述提供光子集成结构的步骤中,所述光子集成结构还包括:第一开孔,以及设置于所述第一开孔中的导电材料;所述提供第一衬底的步骤中,所述第一衬底还包括:第二开孔,以及设置于所述第二开孔中的导电材料;在将所述光子集成结构与所述第一衬底键合的步骤中,使得所述第一开孔与所述第二开孔对准,并且所述第一开孔中的所述导电材料与对应的所述第二开孔中的所述导电材料电性连接。

示例性的,所述第一开孔贯穿所述第一介电层;所述第二开孔贯穿所述第一衬底。

示例性的,在去除所述背衬底之后,在所述第一介电层中形成所述第一开孔。

示例性的,在去除所述背衬底之前,在所述第一介电层中形成所述第一开孔。

示例性的,其中,所述光子集成结构具有第一侧以及与所述第一侧相对的第二侧,所述第一介电层位于所述光子集成结构的第二侧,并且,所述光子集成结构的第二侧朝向所述第一衬底进行键合。

示例性的,还包括,在所述第一介电层的第一侧形成第二介电层,所述第二介电层覆盖所述光栅耦合器。

示例性的,其中所述光子集成结构与所述第一衬底之间通过氧化物-氧化物键合方式进行键合。

示例性的,包括在所述第一衬底的第一侧形成第五介电层;形成第三开孔,所述第三开孔贯穿所述第五介电层,并且所述第三开孔与所述第二开孔对准;以及在所述第三开孔中形成导电材料,在所述将所述光子集成结构与所述第一衬底键合时,使得所述第五介电层位于所述光子集成结构与所述第一衬底之间,并且使得所述第三开孔中的导电材料与所述第二开孔中的导电材料电性连接。

在一个示例性的实施方式中,提出一种封装结构,其包括采用本申请中所述的制造方法制造。

在一个示例性的所述方式中,提出一种光子集成电路芯片,所述光子集成电路芯片包括:光子集成结构,所述光子集成结构包括:光栅耦合器,以及反射层,其中,所述反射层与所述光栅耦合器对应;还包括第一衬底;其中,所述反射层位于所述光栅耦合器与所述第一衬底之间,所述光子集成电路芯片由所述光子集成结构与所述第一衬底键合而获得。

示例性的,所述光子集成结构包括第一介电层;所述第一介电层来自SOI衬底中的绝缘层,并且所述SOI衬底中的原有背衬底被去除;其中,所述反射层形成于所述第一介电层背离所述光栅耦合器的一侧。

示例性的,在所述第一介电层中设置有用于容纳反射层的开孔,所述反射层设置于所述容纳反射层的开孔中。

示例性的,所述光子集成电路芯片包括第五介电层,所述第五介电层位于所述光子集成结构与所述第一衬底之间。

在一个示例性的实施方式中,提出一种光子集成电路芯片,其包括采用本申请中所述的制造方法制造。

本公开中实施例中反射层的设置方式,可通过去除光子集成电路的初始衬底(例如背衬底)而制造反射层等相关结构,可以避免对光子集成结构中光子器件层产生不良影。另外,可以利用同一个掩模版形成反射层以及一些导电通孔对应区域,而节省额外工艺步骤。在一些步骤中,光子集成结构中的原有介电层(例如第一介电层)进行键合,无需在光子集成结构上设置额外的键合结构,减少了工艺流程。此外,键合获得的光子集成电路,贯穿衬底的导电开孔,能够适用更多场景的封装。

本发明实施方式的各个方面、特征、优点等将在下文结合附图进行具体描述。根据以下结合附图的具体描述,本发明的上述方面、特征、优点等将会变得更加清楚。

附图说明

图1A-图5B示出了一种示例性的封装结构的制造方法的中间步骤或相关结构的示意图;

图6示出了一种示例性的封装结构的示意图;

图7A-7C示出了一种示例性的封装结构的制造方法的中间步骤或相关结构的示意图;

图8示出了一种示例性的光子集成电路芯片的示意图。

具体实施方式

在光子集成电路中,有时需要将光耦合入光子集成电路,使得光在光子集成电路中传输、或者输入光子集成电路中的光子器件。在光子集成电路中通常设置有耦合结构或者耦合器件,以实现光的输入。制造合适的光子集成电路,以提高光的耦合效率,减少光在光耦合过程中的损失十分重要。本发明人已经认识到,在设置反射层以提高耦合结构的光耦合效率时,反射层的设置工艺方法、位置等很重要,合适的设置方法能够改善光的耦合效果并且不会影响光子集成电路中的其它器件,还可以降低成本。

另外,本发明人已经认识到,在对光子集成电路进行封装时,基于电连接的需要,有时希望在光子集成电路中形成贯穿材料层以及贯穿衬底的导电结构。

在光子集成电路的生长衬底形成过孔时,目前仍然存在一些挑战,例如其工艺本身可能并不成熟,或者会因为工艺等原因对光子电路中的器件产生影响。

为了便于理解本发明技术方案的各个方面、特征以及优点,下面结合附图对本发明进行具体描述。应当理解,下述的各种实施方式只用于举例说明,而非用于限制本发明的保护范围。

本公开中使用的术语仅出于描述特定实施例的目的并且不意图限制本公开。如本公开中使用的,单数形式“一个”、“一”和“该”意图也包括复数形式,除非上下文清楚地另有指示。将进一步理解的是,术语“包括”和/或“包含”当在本说明书中使用时指定所述及特征、整体、步骤、操作、元件和/或部件的存在,但不排除一个或多个其他特征、整体、步骤、操作、元件、部件和/或其群组的存在或添加一个或多个其他特征、整体、步骤、操作、元件、部件和/或其群组。如本公开中使用的,术语“和/或”包括相关联的列出项目中的一个或多个的任意和全部组合,并且短语“A和B中的至少一个”是指仅A、仅B、或A和B两者。在本公开中,衬底可以指未经切割的衬底,例如未经切割的晶圆,也可以表示经切割的衬底。在本公开中,芯片可以包括裸芯片(die)。在本公开中,一个实施例的特征也可被应用并适当地合并作为在本公开中描述的其他实施例的特征。

实施例一,本实施例提供一种封装结构的制造方法,以及封装结构。一种封装结构的制造方法,包括提供光子集成结构,所述光子集成结构包括:第一开孔,以及设置于所述第一开孔中的导电材料;提供第一衬底,所述第一衬底包括:第二开孔,以及设置于所述第二开孔中的导电材料;将所述光子集成结构与所述第一衬底键合,以使得所述第一开孔中的所述导电材料与对应的所述第二开孔中的所述导电材料电性连接。

示例性的,该封装结构的制造方法采用常规的半导体工艺,因而其亦为半导体结构的制造方法,相应制造获得半导体结构。图1A~图1C示出了所提供光子集成结构的形成步骤,亦即,准备光子集成结构的步骤,其中,所述光子集成结构包括:第一开孔,以及设置于所述第一开孔中的导电材料。在示例性的实施方式中,所述光子集成结构包括第一介电层,所述第一开孔在所述第一介电层中延伸。

如图1A所示,具体的,光子集成结构可基于绝缘体上的半导体层制造,例如绝缘体上硅(SOI,Silicon-On-Insulator)、绝缘体上层叠锗化硅(S-SiGeOI)等,此外,也可以提供其它衬底,用于制造光子集成结构,衬底材料可以是:硅、锗、碳化硅、砷化镓、磷化镓,可以是化合物半导体,也可以是合金半导体等,也可以是上述材料的组合。衬底可以是晶圆,例如SOI晶圆。以绝缘体上硅(SOI,Silicon-On-Insulator)衬底为例,包括提供SOI衬底,所述SOI衬底包括背衬底、绝缘层以及顶层硅。示例性的,绝缘层为埋氧层。其中,绝缘层作为第一介电层,图1A示出了背衬底101、第一介电层102以及顶层硅103。其中,背衬底可以是晶圆,例如硅晶圆。所述第一介电层具有第一侧以及与第一侧相对的第二侧,其中,顶层硅103位于所述第一介电层102的第一侧,背衬底101位于所述第一介电层的第二侧。

如图1B所示,在形成光子集成结构的步骤中,可包括基于所述SOI衬底形成光子器件层104,光子器件层104包括各种类型的光子器件,例如波导、光栅耦合器、光调制器、定向耦合器、多模干涉器(multi-mode inferometer,MMI)、光电探测器、光分束器等。可通过基于顶层硅进行光刻、刻蚀、图案化等步骤,以及沉积、掺杂步骤形成光子器件。在形成光子器件时,可包括沉积不同类型的半导体材料以及金属材料。

示例性的,光子器件位于第一介电层的上方(第一侧),其中,各种类型的光子器件可以是一个或者多个。

如图1C所示,在形成光子器件之后,形成第二介电层105,第二介电层105覆盖一个或多个光子器件。在第二介电层105中可设置有导电连接结构(图未示),以电连接至一个或多个光子器件。可选的,第二介电层105可以包括多个子层。

可根据需要进一步形成电连接结构以及其它材料层。如图1D所示,可在第二介电层上形成第一导电层M1,例如第一金属层。

如图2,在第二介电层105上形成第三介电层106以及第四介电层107,第三介电层、第四介电层可交替堆叠,各个层的厚度和材料可以不一致,第三介电层、第四介电层的材料可以是例如氧化硅、氮化硅。在光子集成结构中形成导电连接结构,其中电连接结构包括导电层(M1,M2,M3,M4),以及导电通孔(V12,V23,V34),导电通孔可用于连接导电层,可根据需要设置导电层以及导电通孔的数量。导电层周围围绕第三介电层和/或第四介电层。可根据需要设置导电连接结构的数量,有的导电连接结构可以用于与光子器件进行电连接,有的可以用于与第一衬底中的第二导电开孔进行电连接。还可根据电连接需要,形成垫108以及UBM109。

如图3A,包括在光栅耦合器1041上方形成开孔110,其中,开孔中可以具有空气,或者设置其它材料,使其具有合适折射率及介电常数,从而形成导光开孔。

如图3B,光子集成结构具有第一侧以及与第一侧相对的第二侧,图3B示出了对光子集成结构的第二侧进行减薄,去除SOI衬底中的背衬底,从而在光子集成结构的第二侧暴露第一介电层102。可选的,也可减薄一部分SOI衬底中的绝缘层。因此,第一介电层102来自SOI衬底中的绝缘层,可以是SOI衬底中的绝缘层直接作为第一介电层102,也可以包括对SOI衬底中的绝缘层进行例如减薄等处理而获得第一介电层102。

如图3C,形成第一开孔111,所述第一开孔111在第一介电层102中延伸。图中示出了与一个M1对应的两个第一开孔111。示例性的,在第一介电层中设置第一开孔111时,也包括第一开孔111在其它材料层延伸的情形,例如,形成第一开孔111时,第一开孔111可在第一介电层102延伸并在第二介电层105中延伸,第一开孔包括第一介电层中的第一部分、以及第二介电层中的第二部分。在图3C的示例中,可从光子集成结构的第二侧开始刻蚀,从而形成第一开孔111。

如图3D,在第一开孔中形成导电材料,从而形成第一导电开孔112,第一导电开孔112与导电层M1形成电连接。第一开孔可贯穿第一介电层,对应的第一导电开孔贯穿第一介电层,构成第一导电通孔。第一开孔贯穿第一介电层、第二介电层。第一导电开孔112与导电层M1形成电连接,第一导电开孔贯穿第一介电层102、第二介电层105。示例性的,本发明在形成第一导电开孔112的过程中,可以包括大马士革工艺。

如图3E,示出了形成反射层114的一种方式,反射层114的位置与光栅耦合器1041对应,其并不需要正对光栅耦合器,只需使得能够将部分光反射回光栅耦合器即可,以增加光栅耦合器的耦合效率。反射层可以包括例如金属层,在形成反射层114时,可以通过在第一介电层102中形成容纳反射层的开孔,然后形成金属材料作为反射层,在此过程中可包括采用大马士革工艺,金属材料可以是例如银、铜、镍等亦或合金材料,反射层114也可以是金属以外的材料或者材料层的堆叠,只需能够实现所需波段的反射即可。本示例为反射层的设置一种具体的方案,可通过在移除初始的衬底之后,形成反射层114,减少了光子集成结构正面的过多工艺,避免对光子集成结构中光子器件层及其它结构产生不良影。此外,相关技术还可结合兼容在键合阶段键合的工艺过程中或者导电通孔形成的工艺过程中,并不需要过多额外的步骤。

可以采用同一个掩模版设置反射层114的区域、第一导电开孔112的区域,从而降低步骤需求或者成本,在一些实施方式中,由于反射层114,第一导电开孔112设置在第一介电层之中或者至少部分被其围绕,因而有利于可以采用类似的工艺形成。反射层114可以使得更多的光进入光栅耦合器1041,从而提高光耦合效率。其中,光栅耦合器1041也可以是其它合适的光耦合结构。在形成反射层114时,也可以不需要在第一介电层112中先形成开孔,而是直接在第一介电层112背离光栅耦合器1041的一侧形成第一介电层。这种设置反射层的方式,可以避免对光子集成结构中光子器件层或其它结构产生不良影。另外,也可在第一介电层102的第二侧形成一个或多个功能性结构113。可选的,第一介电层102的第二侧亦可形成再布线层(图未示),第一导电开孔(的导电材料)与再布线层电连接。

图4A-4B示出了在第一衬底201并在其中形成第二开孔。如图4A,提供原始衬底作为第一衬底201,例如硅衬底,但不限于此。图4B中,在原始衬底中通过刻蚀形成第二开孔202,然后形成导电材料204a(如图4C),从而形成第二导电开孔204。可选的,在设置导电材料204a之前,还可先形成隔离层204b,第二导电开孔204可包括第二开孔中的隔离层204b以及导电材料204a,其中隔离层可包括绝缘材料。在此过程中,可采用常规的制造硅通孔工艺。

示例性的,第一衬底具有第一侧和第二侧,从第一侧形成第二开孔。然后,在第二开孔中设置导电材料,形成导电材料层,从而形成导电开孔。示例性的,可包括在第二开孔的侧壁和底部形成绝缘材料的步骤,以形成绝缘隔离层。在一些实施方式中,绝缘层除了覆盖侧壁和底部,还可覆盖第一衬底的第一侧。在一些实施方式中,使用铜金属化以及使用铜电镀技术来填充第二开孔,从而形成导电开孔。

可选的,在第二开孔中设置导电材料204b之前,还可包括形成阻挡层的步骤,阻挡层可用于扩散阻挡以防止导电材料层中的金属扩散至衬底,也可用作导电材料和电介质之间的粘合层。示例性的阻挡层可以是例如TaN、Ta、Ti、TiN,但不限于此。

第二开孔中的导电材料层的材料可以是铜,或者基于铜的合金。示例性的导电材料还可以包括钨、铝等材料,也可以是其它具有良好导电性能的材料。在形成导电材料层之后。可通过研磨、蚀刻等工艺去除覆盖于第一衬底表面的多余的导电材料层、阻挡层。在一些实施例中,亦可研磨、蚀刻等方式去除部分或者全部覆盖于衬底表面绝缘隔离层。

可选的,第一衬底也可以是透明衬底,例如玻璃衬底、石英衬底等,也可以是本领域中其它常见的衬底材料。

在图4C示出了在第一衬底201中形成有第二导电开孔204,第二导电开孔204形成于衬底201的第一侧。在第二导电开孔204形成之后,如图4D所示,可选的,包括进一步形成介电层(第五介电层205),覆盖该第一衬底表面以及第二导电开孔。并在第五介电层中形成第三开孔,在第三开孔中设置导电材料,形成第三导电开孔206,第三导电开孔206可贯穿第五介电层205,从而构成第三导电通孔。第三导电开孔与第二导电开孔电连接。其中,第三导电开孔可以是插塞(plug),例如铜插塞,当然也可以包括其它金属材料或导电材料。其中,第三开孔、第二开孔在对准的那一侧可以具有不同的开孔区域大小。示例性的,可以有一个或多个第三开孔与同一个第二开孔对准,例如图中示出了两个第三开孔对准至第二开孔。在没有特别说明的情况下,本公开中开孔之间“对准”包括如下情形(以第三开孔与第二开孔对准为例),第三开孔与第二开孔的对准并不需要严格使得它们的中心对准;在一些情况下,第三开孔在对准一侧的开孔区域,以及第二开孔在对准一侧的开孔区域可以仅有部分重叠,只需实现正常导电连接的功能即可。示例性的,第三导电开孔在形成过程中可以包括大马士革工艺。

在图5A中,光子集成结构与第一衬底进行键合。其中,所述反射层114位于所述光栅耦合器1041与所述第一衬底201之间。去除了光子集成结构的初始衬底后进行键合,将带有反射层114的光子结构与第一衬底201键合。示例性的,在图5A所示的实施方式中,反射层114位于第一介电层102与第五介电层205之间。

在一些实施方式,光子集成结构具有第一侧以及与第一侧相对的第二侧,第一介电层在光子集成结构的第二侧露出,第一介电层102的第二侧朝向第一衬底201进行键合。示例性的,在键合时,第一介电层的第二侧朝向第一衬底的第一侧,使得光子集成结构的第一开孔112与第一衬底201的第二开孔204进行对准,以使得第一开孔112、第二开孔204中的导电材料实现电连接,亦即,第一导电开孔与对应的第二导电开孔实现对准,以及电连接。其中,第一开孔、第二开孔在对准的那一侧可以具有不同的开孔区域大小,第一开孔与第二开孔的对准并不需要严格使得它们的中心对准。在一些情况下,第一开孔在对准一侧的开孔区域,以及第二开孔在对准一侧的开孔区域可以仅有部分重叠,只需实现正常导电连接的功能即可。示例性的,可以有一个或多个第二开孔与同一个第一开孔对准,图5A中示出了两个第一开孔与同一个第二开孔对准,进而,对应的两个第一导电开孔112与同一个第二导电开孔204对准。在一些实施方式中,光子集成结构可以具有多个第一开孔,每一个第二开孔可以对准一个或一组第一开孔,其中,一组第一开孔包括多个第一开孔。光子集成结构去除了背衬底,而未在背衬底中形成通孔,可减少在背衬底形成通孔时工艺条件可能对光子集成结构造成不利影响。

在一些实施方式中,外界的光可以从光子集成结构的第一侧输入。

示例性的,第一开孔、第二开孔可以具有不同的孔径尺寸,例如第一开孔可以具有相对第二开孔较小的孔径。在一些实施例中,第二开孔的孔径是第一开孔的孔径的2~10倍,可以根据开孔尺寸的大小,调整一个第一开孔对应的第二开孔的数量,以获得合适的电连接性能。

在图5A中,第一衬底与光子集成结构之间还具有第五介电层205,在键合时,第三导电开孔206与对应的第一导电开孔112电连接。多个第三开孔分别与多个对应的第一开孔对准,亦即第三导电开孔206与对应的第一导电开孔112对准。示例性的,光子集成结构中SOI衬底原有的氧化层/绝缘层(埋氧层)可以作为键合层。

光子集成结构与第一衬底之间的键合可采用氧化物-氧化物之间的键合,例如氧化硅(SiOx)-氧化硅(SiOx)键合。示例性的,第一介电层为氧化硅(SiOx)材料,第五介电层为氧化硅(SiOx)材料,其中SiOx表示材料体系,并不表示第一介电层、第五介电层二者氧含量相同。

在键合时采用光子集成结构中的介电层(例如第一介电层)进行键合,无需在光子集成结构上设置额外的键合结构,减少了工艺流程。

图5B示出了对第一衬底201的第二侧减薄及后续工艺的示意图。在图5B中,可在图5A的第一衬底201的第二侧对第一衬底201进行减薄,形成对应的贯穿衬底开孔(Throughsbustrate via),即使得第二开孔贯穿第一衬底,相应的,第二导电开孔204贯穿第一衬底201,形成为第二导电通孔。可选的,在该第一衬底的第二侧形成介电层207(如图5B)。其中,减薄的工艺可以是例如研磨、化学机械抛光、刻蚀等。

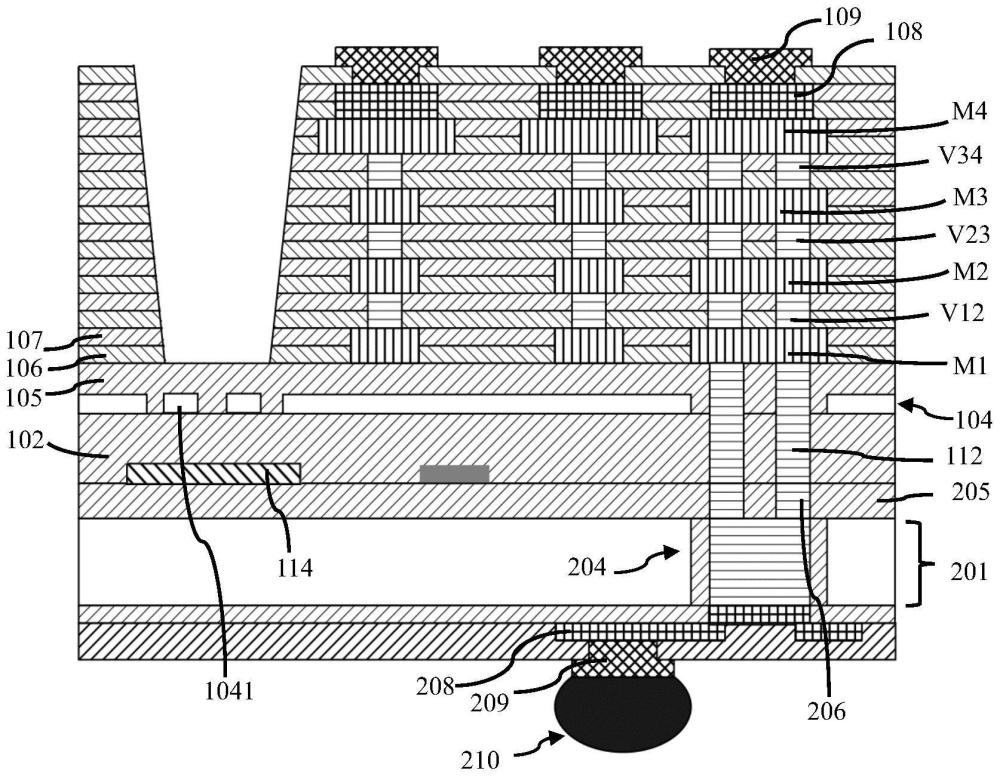

如图6示出了进一步形成其它连接结构后的一种封装结构示意图。在图5B之后,在第一衬底的第二侧形成再布线层(RDL)208,以及UBM209,UBM 209与再布线层208电连接。可根据电连接需要,形成与UBM连接的导电连接件210。导电连接件可以是可控塌陷芯片连接(C4)凸块、球栅阵列(BGA)连接件、焊球、金属柱、微凸块等。导电连接件可以包括诸如焊料、铜、铝、金、镍、银、钯、锡等或它们的组合的导电材料。在一些实施例中,可以通过首先由诸如蒸发、电镀、印刷等常用的方法形成焊料层来形成导电连接件。在一些实施例中,导电连接件是通过溅射、电镀、化学镀、CVD等形成的金属柱,诸如铜柱。

光子集成结构、第一衬底可以单独制造,从而使得第一衬底中形成开孔时并不影响光子集成结构。另外,光子集成结构中第一介电层的开孔,与第一衬底中的开孔可以通过不同的工艺制造,也可以具有不同的尺寸,例如光子集成结构中与第一衬底电连接的导电开孔的可以具有相对第一衬底通孔较小的孔径,从而工艺上更容易实现。

所制造的封装结构具有第一表面(图6中封装结构的上表面)以及与第一表面相对的第二表面,封装结构包括导电路径,该导电路径在封装结构的第一表面与第二表面之间延伸,所述导电路径依次经过第一导电开孔、第二导电开孔。示例性的,依次经过第一导电开孔、第三导电开孔、第二导电开孔。

在一些实施方式中,一些材料或者层的制造顺序可以根据需要而调整。例如,可以在光子集成结构与第一衬底键合之后,形成垫108以及UBM 109。可选的,在光子集成结构与第一衬底键合之前,就在第一衬底中形成贯穿第一衬底的第二开孔。可选的,在光子集成结构与第一衬底键合之前,在第一衬底的第二侧形成RDL结构。可选的,在光子集成结构与第一衬底键合之前,在光子集成结构的第一介电层的第二侧亦可形成再布线层,光子集成结构的第一导电开孔(的导电材料)通过再布线层与第一衬底中对应的第二导电开孔(的导电材料)进行电连接,在电连接时无需使第一导电开孔与第二导电开孔进行对准。

本发明提供一种封装结构,其可以由本发明的封装方法制造。示例性的封装结构如图6所示。包括:光子集成结构,所述光子集成结构包括:第一开孔,以及设置于所述第一开孔中的导电材料;第一衬底,所述第一衬底包括:第二开孔,以及设置于所述第二开孔中的导电材料;所述第一开孔与所述第二开孔对准,并且所述第一开孔中的所述导电材料与对应的所述第二开孔中的所述导电材料电性连接。

实施例二,在本实施例中,在去除SOI衬底中的背衬底之前,在所述第一介电层中形成所述第一开孔。在如图1C的步骤之后,可包括在第一介电层102中形成第一开孔的步骤,以及设置导电材料从而形成第一导电开孔112(如图7A),在后续步骤去除SOI衬底中的背衬底101。示例性的,在形成第二介电层105后,如图7A所示,可以自第二介电层105至第一介电层102进行刻蚀,形成穿过第二介电层、第一介电层的第一开孔,该开孔包括第一介电层中的第一部分、以及第二介电层中的第二部分,在第一开孔中设置有导电材料,从而形成第一导电开孔112,第一导电开孔112贯穿第一介电层,从而构成第一导电通孔。

然后,如图7B所示,可在第二介电层105上形成第一导电层M1。可根据需要进一步形成电连接结构以及其它材料层。可参考图2,在第二介电层上形成第三介电层以及第四介电层,第三介电层、第四介电层可交替堆叠,各个层的厚度和材料可以不一致。在光子集成结构中形成导电互连结构,其中电互连结构包括导电层(M1,M2,M3,M4),以及导电通孔(V12,V23,V34),导电通孔可用于连接导电层。导电层周围围绕第三介电层和/或第四介电层。

如图7C,然后去除衬底101,使得第一导电开孔112暴露。在后续步骤中,可参考如图4A~6中相应步骤,将光子集成结构与第一衬底进行键合。

本发明提还供一种光子集成电路芯片,其可以由本发明各实施例的封装方法制造。光子集成电路芯片包括:所述光子集成电路芯片包括:光子集成结构,所述光子集成结构包括:光栅耦合器,以及反射层,其中,所述反射层与所述光栅耦合器对应;还包括第一衬底;其中,所述反射层位于所述光栅耦合器与所述第一衬底之间,所述光子集成电路芯片由所述光子集成结构与所述第一衬底键合而获得。示例性的光子集成电路芯片如图8所示,光子集成电路芯片800包括光子集成结构100,光子集成结构100设置于第一衬底201上方。所述光子集成结构100包括第一介电层102,所述第一开孔在所述第一介电层中延伸,第一开孔中设置有导电材料,从而构成第一导电开孔112;所述第一开孔贯穿所述第一介电层102。

第二开孔中设置有导电材料,从而形成第二导电开孔204;所述第二开孔贯穿所述第一衬底201。

所述光子集成结构100基于SOI衬底形成,其中,所述SOI衬底包括背衬底、绝缘层以及顶层硅,第一介电层102可来自SOI衬底中的绝缘层。

所述背衬底被去除,以使所述第一介电层102与所述第一衬底201键合。

所述光子集成结构100具有第一侧以及与所述第一侧相对的第二侧,所述第一介电层102在所述光子集成结构的第二侧暴露,并且,所述光子集成结构的第二侧朝向所述第一衬底201的第一侧进行键合。

其中,所述第一介电层102具有第一侧以及与所述第一侧相对的第二侧,所述光子集成结构包括光子器件层104,光子器件层104包括各种类型的光子器件,例如波导、光栅耦合器、光调制器、定向耦合器、多模干涉器(multi-mode inferometer,MMI)、光电探测器、光分束器等,所述光子器件设置于所述第一介电层102上方,即所述光子器件位于所述第一介电层102的第一侧,所述第一介电层102的第二侧与所述第一衬底201进行键合。

所述光子集成结构还包括第二介电层105,所述第一开孔贯穿第一介电层以及第二介电层。

在图8中,示例性的,光子集成电路芯片800包括依次设置的第一衬底201,第五介电层205、第一介电层102,光子器件层104、第二介电层105、第三介电层106以及第四介电层107。如图8所示,光子集成电路芯片还包括反射层114,位于所述第一衬底201与所述光栅耦合器1041之间。示例性的,反射层114位于第五介电层205与第一介电层102之间。

光子集成电路芯片800具有第一表面(图8中光子集成电路芯片的上表面)以及与第一表面相对的第二表面,光子集成电路包括导电路径,该导电路径穿过光子集成电路芯片,该导电路径在光子集成电路芯片的第一表面与第二表面之间延伸,在该导电路径从第一表面至第二表面的方向上,所述导电路径依次经过第一导电开孔112、第二导电开孔204。在一些实施方式中,在该导电路径从第一表面至第二表面的方向上,所述导电路径依次经过第一导电开孔112、第三导电开孔206、第二导电开孔204。

光子集成电路芯片800包括第五介电层205,所述第五介电层位于所述第一介电层以及所述第三介电层之间;第五介电层205具有第三开孔,所述第三开孔贯穿所述第五介电层,并且所述第三开孔与所述第二开孔对准;以及在所述第三开孔中形成导电材料,使得所述第三开孔中的导电材料与所述第二开孔中的导电材料连接,从而,第五介电层205具有第三导电开孔206。

在一些实施方式中,光子集成电路芯片中可以具有多个第二开孔,每一个第二开孔都对应多个第一开孔。

本领技术人员应当理解,以上所公开的仅为本发明的实施方式而已,当然不能以此来限定本发明请求专利保护的权利范围,依本发明实施方式所作的等同变化,仍属本发明之权利要求所涵盖的范围。

- 膜上芯片封装件以及膜上芯片封装件的制造方法

- 芯片封装方法及芯片封装结构

- 一种扇出型芯片封装结构及其制造方法

- 芯片封装结构的制造方法

- 光子集成电路及其制造方法、光子计算系统、光子计算芯片

- 一种背向散射光栅耦合封装结构的光子芯片及其制造方法