可重构计算结构、计算方法及硬件架构

文献发布时间:2023-06-19 12:13:22

技术领域

本发明涉及计算机技术领域,尤其涉及一种可重构计算结构、计算方法及硬件架构。

背景技术

目前,许多应用需求包括多个复杂的运算,例如,一个多媒体应用中可能包括数据并行处理、位处理、不规则计算、高精度字操作、具有实时要求的操作等子任务,要求处理系统能够灵活地处理上述各个子任务。

然而,传统计算结构采用的是固定的硬件资源进行计算,无法根据不同计算任务灵活配置相应的硬件资源。此外,传统方案中存储器与逻辑电路分设在两块芯片上,导致存储器到逻辑电路的数据搬运路径较长,增加了功耗和延时。

发明内容

本发明提供一种可重构计算结构、计算方法及硬件架构,用以解决现有技术中无法灵活根据不同计算任务配置硬件资源,且存储器到逻辑电路的数据搬运距离较长,增加了功耗和延时的缺陷。

本发明提供一种可重构计算结构,包括:

第一半导体结构和第二半导体结构;

所述第一半导体结构与所述第二半导体结构连接,所述第一半导体结构包括存储器和逻辑电路,所述第二半导体结构包括可重构阵列,所述可重构阵列包括多个可重构算子;

所述逻辑电路用于从所述存储器中获取待运行的运算算法,并基于所述运算算法,对所述可重构阵列中的可重构算子进行配置,确定所述运算算法对应的运算阵列,以使所述第二半导体结构基于所述运算阵列执行所述运算算法。

根据本发明提供的一种可重构计算结构,所述第二半导体结构还包括基本计算阵列,所述基本计算阵列是预先配置的固定阵列。

根据本发明提供的一种可重构计算结构,所述运算算法包括第一运算子算法和第二运算子算法,所述第一运算子算法的复杂度高于所述第二运算子算法的复杂度;

所述可重构阵列用于执行所述第一运算子算法,所述基本计算阵列用于执行所述第二运算子算法。

根据本发明提供的一种可重构计算结构,所述第一半导体结构与所述第二半导体结构是通过对第一键合层和第二键合层进行键合处理后连接的;所述第一键合层设置于所述第一半导体结构,所述第二键合层设置于所述第二半导体结构。

根据本发明提供的一种可重构计算结构,所述第一半导体结构还包括接口电路,所述接口电路用于从外部数据流获取所述运算算法,以使所述存储器存储所述运算算法,以及用于输出所述运算算法的运算结果。

根据本发明提供的一种可重构计算结构,所述接口电路包括用于通信的接口。

本发明还提供一种基于如上所述可重构计算结构的计算方法,包括:

获取所述运算算法以及所述运算算法对应的运算数据;

将所述运算数据输入所述第一半导体结构,通过所述第二半导体结构执行所述运算算法。

根据本发明提供的一种基于可重构计算结构的计算方法,所述运算算法包括第一运算子算法和第二运算子算法,所述第一运算子算法的复杂度高于所述第二运算子算法的复杂度;所述第二半导体结构还包括基本计算阵列,所述基本计算阵列是预先配置的固定阵列;

所述将所述运算数据输入所述第一半导体结构,通过所述第二半导体结构执行所述运算算法,包括:

将所述运算数据输入所述第一半导体结构,通过所述可重构阵列执行所述第一运算子算法,以及通过所述基本计算阵列执行所述第二运算子算法。

根据本发明提供的一种基于可重构计算结构的计算方法,在通过所述第二半导体结构执行所述运算算法之后,还包括:

将所述运算算法的运算结果输入至所述第一半导体结构,通过所述第一半导体结构的接口电路输出所述运算结果。

本发明还提供一种基于可重构计算结构的硬件架构,包括:如上所述的可重构计算结构。

本发明提供的可重构计算结构、计算方法及硬件架构,逻辑电路对可重构阵列中的可重构算子进行配置,确定运算算法对应的运算阵列,从而可以根据不同场景下的运算算法,灵活配置相应的可重构算子,以使第二半导体结构基于对应的运算阵列执行运算算法。同时,存储器和逻辑电路均设置于第一半导体结构,从而能够有效减小存储器与逻辑电路之间的数据搬运距离,减小了功耗和延时。此外,存储器和逻辑电路,与可重构阵列分设在两个半导体结构中,突破了平面工艺限制,增加了计算逻辑资源的存储空间。

附图说明

为了更清楚地说明本发明或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

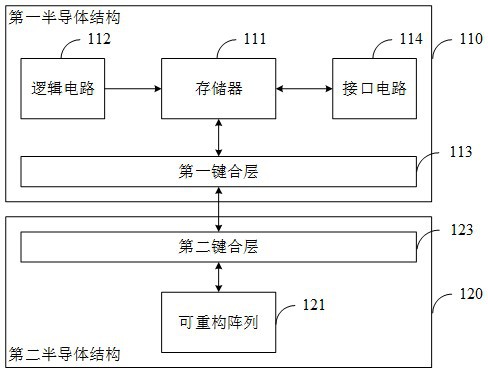

图1是本发明提供的可重构计算结构的结构示意图;

图2是本发明提供的又一可重构计算结构的结构示意图;

图3是本发明提供的基于可重构计算结构的计算方法的流程示意图;

图4是本发明提供的第二半导体结构执行运算算法的流程示意图;

附图标记:

110:第一半导体结构;120:第二半导体结构;111:存储器;112:逻辑电路;

113:第一键合层;114:接口电路;121:可重构阵列;122:基本计算阵列;

123:第二键合层。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明中的附图,对本发明中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

对此,本发明提供一种可重构计算结构。图1是本发明提供的可重构计算结构的结构示意图,如图1所示,该计算结构包括:第一半导体结构110和第二半导体结构120。

第一半导体结构110与第二半导体结构120连接,第一半导体结构110包括存储器111和逻辑电路112,第二半导体结构120包括可重构阵列121,可重构阵列包括多个可重构算子。其中,第一半导体结构110与第二半导体结构120可以通过半导体接合工艺连接,如键合连接,从而第一半导体结构110中的运算数据可以传输至第二半导体结构120,以完成相应的运算。

其中,第一半导体结构110上的存储器111,可以通过接口从外部数据流中获取待运行的运算算法,并存储运算算法。逻辑电路112用于从存储器111获取运算算法,并基于运算算法,对可重构阵列121中的可重构算子进行配置,确定运算算法对应的运算阵列,以使第二半导体结构120基于运算阵列执行运算算法。

可以理解的是,由于可重构阵列121中具有多种可重构算子,逻辑电路112对各可重构算子进行配置,可以得到不同的计算阵列,各计算阵列可以实现不同的算子功能,如在对函数式进行计算时,可以根据不同场景下的权重、系数等,灵活配置相应的可重构算子完成相应的运算算法。

相较于专用集成电路 ASIC无法处理特定计算任务之外的其它任务,本发明实施例提供的可重构计算结构不仅能够根据不同场景灵活执行相应的运算算法,而且能够保证较高的性能。例如,一个多媒体应用中可能包括数据并行处理、位处理、不规则计算、高精度字操作、具有实时要求的操作等子任务,要求处理系统能够灵活地处理上述各个子任务并达到一定的性能。许多其它应用也具有类似的需求,如数据加密、人工智能等,本发明实施例提供的计算结构能够根据不同场景下的计算任务,灵活配置相应的可重构算子,完成对应的运算算法。

此外,相较于传统方法中存储器与逻辑电路分设在两块芯片上,本发明实施例将存储器111和逻辑电路112均设置于第一半导体结构110,从而能够有效减小存储器111与逻辑电路112之间的数据搬运距离,减小了功耗和延时,提高了执行运算算法的效率。

需要说明的是,第一半导体结构110与第二半导体结构120可以上下叠加设置,从而可以大幅度缩短存储器111至可重构阵列121的数据搬运距离,减少了存储器111到可重构阵列121的数据搬运延迟,进而减少了功耗和延时。此外,第一半导体结构110与第二半导体结构120上下叠加设置,使得第一半导体结构110与第二半导体结构120所占的面积相当于一个半导体结构的面积,即减小了计算结构的占用面积,使得计算结构能够集成在一个较小的芯片中,降低了芯片制造成本。同时,存储器和逻辑电路,与可重构阵列分设在两个半导体结构中,从而增加了计算逻辑资源的存储空间。

由此可见,本发明实施例提供的可重构计算结构,逻辑电路对可重构阵列中的可重构算子进行配置,确定运算算法对应的运算阵列,从而可以根据不同场景下的运算算法,灵活配置相应的可重构算子,以使第二半导体结构基于对应的运算阵列执行运算算法。同时,存储器和逻辑电路均设置于第一半导体结构,从而能够有效减小存储器与逻辑电路之间的数据搬运距离,减小了功耗和延时。此外,存储器和逻辑电路,与可重构阵列分设在两个半导体结构中,突破了平面工艺限制,增加了计算逻辑资源的存储空间。

基于上述实施例,第二半导体结构120还包括基本计算阵列122,基本计算阵列122是预先配置的固定阵列。

具体地,基本计算阵列122是预先配置的固定阵列,可以对固定的运算算法进行运算(例如基本的加法、乘法等)。

如图2所示,在第二半导体结构120上还设置基本计算阵列122,从而当运算算法无需根据不同场景调节权重或系数时,即运算算法对应的运算公式是固定的基本算法,如加法、乘法等,则可以通过基本计算阵列122执行该运算算法,而不需要逻辑电路112对可重构算子进行配置,节约了逻辑电路112的逻辑计算量。

需要说明的是,第一半导体结构110与第二半导体结构120可以上下叠加设置,从而可以大幅度缩短存储器111至可重构阵列121和基本计算阵列122的数据搬运距离,减少了存储器111到可重构阵列121和基本计算阵列122的数据搬运延迟,进而减少了功耗和延时。

基于上述任一实施例,运算算法包括第一运算子算法和第二运算子算法,第一运算子算法的复杂度高于第二运算子算法的复杂度;

可重构阵列121用于执行第一运算子算法,基本计算阵列122用于执行第二运算子算法。

具体地,运算算法包括第一运算子算法和第二运算子算法,第一运算子算法的复杂度高于第二运算子算法的复杂度。例如,第一运算子算法可以为函数式运算,其对应计算公式中的权重或系数会根据不同场景变化,第二运算子算法可以为基本加减运算,其对应的计算公式是固定不变的。

在此基础上,作为一种优选实施例,可重构阵列121用于执行第一运算子算法,即逻辑电路112可以根据不同场景对可重构阵列121中的可重构算子进行配置,确定与第一运算子算法匹配的计算阵列,实现根据不同场景灵活执行第一运算子算法。同时,由于第二运算子算法在不同场景下对应的运算公式是固定不变的,即可以理解为第二运算子算法在不同场景下对应的硬件资源是固定不变的,因此可以采用基本计算阵列122执行第二运算子算法。

需要说明的是,可重构阵列121和基本计算阵列122可以基于第一运算子算法和第二运算子算法的顺序,执行对应的运算子算法。例如,若运算算法中运算子算法的计算顺序为“第一运算子算法→第二运算子算法”,则第二半导体结构120中执行对应运算子算法的阵列顺序为“可重构阵列→基本计算阵列”;若运算算法中运算子算法的计算顺序为“第二运算子算法→第一运算子算法”,则第二半导体结构120中执行对应运算子算法的阵列顺序为“基本计算阵列→可重构阵列”。

由此可见,本发明实施例根据运算算法中运算子算法的复杂度,由可重构阵列121和基本计算阵列122分别执行对应的运算子算法,从而对于复杂度较高的第一运算子算法,可以灵活配置对应的计算阵列,对于复杂度较低的第二运算子算法,采用基本计算阵列执行相应的运算子算法,即对于第二运算子算法不需要逻辑电路112对可重构算子进行配置,节约了逻辑电路112的逻辑计算量。

基于上述任一实施例,第一半导体结构110与第二半导体结构120是通过对第一键合层113和第二键合层123进行键合处理后连接的;第一键合层113设置于第一半导体结构110,第二键合层123设置于第二半导体结构120。

具体地,如图1所示,第一半导体结构110上设置有第一键合层113,第二半导体结构120上设置有第二键合层123,第一键合层113和第二键合层123之间通过键合连接,从而第一半导体结构110与第二半导体结构120可以实现数据交互,例如第一半导体结构110可以将运算算法对应的运算数据传输给第二半导体结构120,第二半导体结构120可以将运算算法对应的运算结果传输给第一半导体结构110。

其中,键合是将两片表面清洁、原子级平整的同质或异质半导体材料经表面清洗和活化处理,在一定条件下直接结合,通过范德华力、分子力甚至原子力使晶片键合成为一体。例如,本发明实施例可以采用半导体直接键合技术,使得第一半导体结构110与第二半导体结构120键合连接,从而不仅能够实现第一半导体结构110与第二半导体结构120之间的数据交互,而且可以将第一半导体结构110与第二半导体结构120集成在一个较小的芯片中,节约了芯片的制造成本。

基于上述任一实施例,第一半导体结构110还包括接口电路114,接口电路114用于从外部数据流获取运算算法,以使存储器111存储运算算法,以及用于输出运算算法的运算结果。

具体地,如图1所示,第一半导体结构110还包括接口电路114,接口电路114可以从外部数据流中获取运算算法,并存储至存储器111中,从而逻辑电路112可以从存储器111中获取运算算法。

此外,在第二半导体结构120执行完成运算算法之后,可以将对应的运算结果输入至接口电路114,从而接口电路114可以输出相应的运算结果。

由此可见,本发明实施例通过在第一半导体结构110上设置接口电路114,从而可以实现可重构计算结构与外部数据流之间的数据交互。

基于上述任一实施例,接口电路114包括用于通信的接口。

具体地,接口电路114包括用于通信的接口,通过该接口可以实现与外部数据流之间的数据交互。其中,该接口可以为以太网接口,也可以为其它通信协议接口,本发明实施例对此不作具体限定。

例如,接口电路114通过接口获取外部数据流中的运算算法,存储器111将该运算算法存储,从而逻辑电路112可以从存储器111中获取运算算法,并基于运算算法确定算法阵列,以使第二半导体结构120执行运算算法。此外,第二半导体结构120可以将运算算法对应的运算结果传输至接口电路114,从而接口电路114可以通过接口输出该运算结果。

基于上述任一实施例,本发明提供一种基于如上任一实施例所述的可重构计算结构的计算方法,该方法包括:

获取运算算法以及运算算法对应的运算数据;

将运算数据输入第一半导体结构,通过第二半导体结构执行运算算法。

具体地,在获取运算算法和运算数据之后,将运算数据输入至第一半导体结构,第一半导体结构中的存储器负责存储运算算法和运算数据,从而第一半导体结构中的逻辑电路可以从存储器中获取运算算法。其中,存储器可以通过接口从外部数据流中获取待运行的运算算法,并存储运算算法。

在逻辑电路获取运算算法之后,逻辑电路基于运算算法,对可重构阵列中的可重构算子进行配置,确定运算算法对应的运算阵列,以使第二半导体结构基于运算阵列执行运算算法。可以理解的是,第一半导体结构与第二半导体结构可以通过半导体接合工艺连接,如键合连接,从而第一半导体结构中的运算数据可以传输至第二半导体结构,以完成相应的运算。

由于可重构阵列中具有多种可重构算子,逻辑电路对各可重构算子进行配置,可以得到不同的计算阵列,各计算阵列可以实现不同的算子功能,如在对函数式进行计算时,可以根据不同场景下的权重、系数等,灵活配置相应的可重构算子完成相应的运算算法。

此外,相较于基于传统方法的计算结构进行计算的方法,本发明实施例中由于存储器和逻辑电路均设置于第一半导体结构,从而能够有效减小存储器与逻辑电路之间的数据搬运距离,减小了功耗和延时,提高了执行运算算法的效率。

此外,第一半导体结构与第二半导体结构可以上下叠加设置,从而可以大幅度缩短存储器至可重构阵列的数据搬运距离,减少了存储器到可重构阵列的数据搬运延迟,进而减少了功耗和延时。此外,第一半导体结构与第二半导体结构上下叠加设置,使得第一半导体结构与第二半导体结构所占的面积相当于一个半导体结构的面积,即减小了计算结构的占用面积,使得计算结构能够集成在一个较小的芯片中,降低了芯片制造成本。同时,存储器和逻辑电路,与可重构阵列分设在两个半导体结构中,从而增加了计算逻辑资源的存储空间。

如图3所示,将运算数据输入至第一半导体结构,第一半导体结构将运算数据传输到第二半导体结构,第二半导体结构基于运算数据进行数据运算,当第二半导体结构完成数据运算之后,第二半导体结构将运算结果传输到第一半导体结构,若不需进行下一步计算,则由第一半导体结构输出运算结果。若需要在此基础上进行下一步计算,则第一半导体结构将下一步计算的数据输入至第二半导体结构,以使第二半导体结构按照上述方法进行数据处理。

由此可见,本发明实施例提供的基于可重构计算结构的计算方法,通过逻辑电路对可重构阵列中的可重构算子进行配置,确定运算算法对应的运算阵列,从而可以根据不同场景下的运算算法,灵活配置相应的可重构算子,以使第二半导体结构基于对应的运算阵列执行运算算法。同时,存储器和逻辑电路均设置于第一半导体结构,从而能够有效减小存储器与逻辑电路之间的数据搬运距离,减小了功耗和延时。此外,存储器和逻辑电路,与可重构阵列分设在两个半导体结构中,突破了平面工艺限制,增加了计算逻辑资源的存储空间。

基于上述任一实施例,运算算法包括第一运算子算法和第二运算子算法,第一运算子算法的复杂度高于第二运算子算法的复杂度;第二半导体结构还包括基本计算阵列,基本计算阵列是预先配置的固定阵列;

将运算数据输入第一半导体结构,通过第二半导体结构执行运算算法,包括:

将运算数据输入第一半导体结构,通过可重构阵列执行第一运算子算法,以及通过基本计算阵列执行第二运算子算法。

具体地,运算算法包括第一运算子算法和第二运算子算法,第一运算子算法的复杂度高于第二运算子算法的复杂度。例如,第一运算子算法可以为函数式运算,其对应计算公式中的权重或系数会根据不同场景变化,第二运算子算法可以为基本加减运算,其对应的计算公式是固定不变的。

在此基础上,可重构阵列用于执行第一运算子算法,即逻辑电路可以根据不同场景对可重构阵列中的可重构算子进行配置,确定与第一运算子算法匹配的计算阵列,实现根据不同场景灵活执行第一运算子算法。同时,由于第二运算子算法在不同场景下对应的运算公式是固定不变的,即可以理解为第二运算子算法在不同场景下对应的硬件资源是固定不变的,因此可以采用基本计算阵列执行第二运算子算法。

需要说明的是,可重构阵列和基本计算阵列可以基于第一运算子算法和第二运算子算法的顺序,执行对应的运算子算法。

如图4所示,在获取运算算法之后,若运算算法中第一运算子算法计算顺序在第二运算子算法之前,则第二半导体结构中执行对应运算子算法的阵列顺序为“可重构阵列执行第一运算子算法→基本计算阵列执行第二运算子算法”;若运算算法中第一运算子算法计算顺序在第二运算子算法之后,则第二半导体结构中执行对应运算子算法的阵列顺序为“基本计算阵列执行第二运算子算法→可重构阵列执行第一运算子算法”。

由此可见,本发明实施例根据运算算法中运算子算法的复杂度,由可重构阵列和基本计算阵列分别执行对应的运算子算法,从而对于复杂度较高的第一运算子算法,可以灵活配置对应的计算阵列,对于复杂度较低的第二运算子算法,采用基本计算阵列执行相应的运算子算法,即对于第二运算子算法不需要逻辑电路对可重构算子进行配置,节约了逻辑电路的逻辑计算量。

基于上述任一实施例,在使第二半导体结构执行运算算法之后,还包括:

将运算算法的运算结果输入至第一半导体结构,以使第一半导体结构的接口电路输出运算结果。

具体地,第一半导体结构可以通过接口电路从外部数据流中获取运算算法,并存储至存储器中,从而逻辑电路可以从存储器中获取运算算法。

此外,在第二半导体结构执行完成运算算法之后,可以将对应的运算结果输入至接口电路,从而接口电路可以输出相应的运算结果。

基于上述任一实施例,一种可重构计算结构的硬件架构,包括:如上任一实施例所述的可重构计算结构。

具体地,上述实施例提供的可重构计算结构,通过逻辑电路对可重构阵列中的可重构算子进行配置,确定运算算法对应的运算阵列,从而可以根据不同场景下的运算算法,灵活配置相应的可重构算子,以使第二半导体结构基于对应的运算阵列执行运算算法。同时,存储器和逻辑电路均设置于第一半导体结构,从而能够有效减小存储器与逻辑电路之间的数据搬运距离,减小了功耗和延时。此外,存储器和逻辑电路,与可重构阵列分设在两个半导体结构中,突破了平面工艺限制,增加了计算逻辑资源的存储空间。

因此,包含上述任一实施例的可重构计算结构的硬件架构,也具有上述可重构计算结构的所有优点。其中,可以将上述可重构计算结构封装于晶圆内,得到可重构计算结构的硬件架构,由于数据传输和数据转移是在晶圆级别的,数据信号从第一半导体结构到第二半导体结构的传输速度会更快,能够有效地减少时延,降低功耗。

最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

- 可重构计算结构、计算方法及硬件架构

- 一种基于可重构计算结构的内积计算方法