一种半导体测试用多方式测试系统

文献发布时间:2023-06-19 11:00:24

技术领域

本发明属于半导体测试系统技术领域,具体涉及一种半导体测试用多方式测试系统。

背景技术

半导体器件是导电性介于良导电体与绝缘体之间,利用半导体材料特殊电特性来完成特定功能的电子器件。

在半导体器件测试时,金属电迁移失效和金属应力迁移失效是影响半导体器件可靠性性能的主要因素,其中,所述金属电迁移失效指的是在器件工作时,金属互连线内有一定电流通过并产生电场,在所述电场的作用下,金属离子会沿着导体产生质量的输运,形成金属离子的迁移,金属离子的迁移容易在金属互连线的局部区域产生空洞。当所述空洞达到一定程度时,金属互连线的电阻大大增加,容易导致半导体器件的性能退化或失效。所述金属应力迁移失效指的是:器件在一定温度下工作时,金属互连线与其它材料层的热膨胀系数不一致,所以在金属互连线与其它材料层之间形成应力,从而使金属互连线或者后段通孔中晶粒间的小空隙向应力集中的地方聚集形成空洞。所述空洞达到一定程度后容易使所述金属互连线发生断路,进而容易导致半导体器件的性能退化或失效,影响半导体器件测试的整体效率。

现有的半导体测试系统较为单一,对于一些复合型器件双向SCR、达林顿阵列、光耦、光电逻辑、继电器、三端稳压器、双向触发二极管等只能测试部分参数,并且不能做半导体器件的曲线扫描,严重影响半导体性能的分析判断,影响测试结果。

发明内容

本发明所要解决的技术问题在于针对上述现有技术的不足,提供一种半导体测试用多方式测试系统,以解决上述背景技术中提出的问题。

为解决上述技术问题,本发明采用的技术方案是:一种半导体测试用多方式测试系统,包括PC主机以及与PC主机之间信号连接的DA模块和AD模块;

所述PC主机通过DA模块信号连接有信号控制模块,所述信号控制模块信号连接有功率输出模块,所述功率输出模块信号连接有测试模块;

所述测试模块用于完成测试器件的测试作业;

所述测试模块还信号连接有采样模块,所述采样模块信号连接有信号处理模块,所述信号处理模块通过AD模块将测试信号反馈至PC主机上,完成测试器件的测试过程。

优选的,所述PC主机内预设有测试软件,测试以IGBT的测试标准为依据进行编写,对测试反馈数据进行存储、显示和判断,并根据设计完成硬件加密功能,通过软件启动检测串口,在串口开起后发送检测指令,并根据相应规则返回检测代码,实现软硬件的结合加密。

优选的,所述DA模块是选用16位并口输入的高速DAC709KH芯片,高速DAC709KH芯片将数据信号转化成模拟信号的电压量,其电压量是-10V~10V,在测试时,所述DA模块至少发出一个脉冲信号。

优选的,所述信号控制模块用于将信号分成低源信号和高源信号,并将其输出,低源信号分为低源电压源和低源电流源,高源信号分为高源电压源、高源电流源,所述功率输出模块是信号放大成所需要的功率信号输出到测试模块上。

优选的,所述测试模块与功率输出模块配合使用,完成测试器件的测试。

优选的,所述采样模块包括电压信号或电流信号的采样,用于电压或电流加载到与测试器件连接的测试模块上后,将测试模块上产生的测量的电压信号或电流信号进行采集。

优选的,所述采样模块的采样方式分为普通电压采样、差分电流采样、普通电流采样、高压采样和大电流采样。

优选的,所述信号处理模块是将采样模块的信号进行判断,分别判断出电压信号还是电流信号,并放大或缩小成标准的电压信号输送至AD模块上。

优选的,所述AD模块还连接有滤波电路,滤波电路分为低通滤波和高通滤波,低通滤波是由运放组成的低通滤波器,高通滤波是UAF42AP滤波芯片。

优选的,所以AD模块具体为16位的高速ADC700KP芯片,采样速度是2uS,且在高速ADC700KP芯片前加有采样保持器SHC5320KP,用于保证信号的稳定性,再将信号反馈至PC主机上。

本发明与现有技术相比具有以下优点:

本发明通过对测试系统中的信号控制模块和功率输出模块进行调整,使得测试过程中信号能灵活调整,与功率输出模块配合,完成信号的放大输出,同时将测试信号进行灵活采样,不同的测试信号分别能得到精准的采集,从而使得测试系统能对多个单元进行同时测试,测试种类增加到19大类27分类,便于完成半导体的测试过程。

附图说明

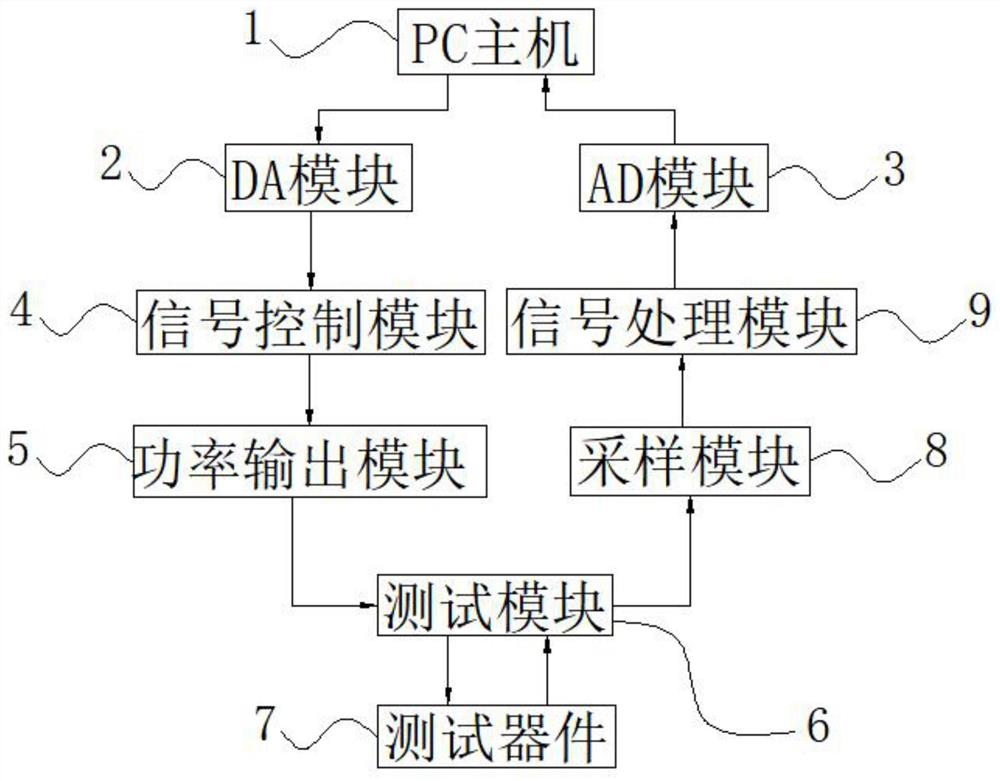

图1是本发明整体原理图图;

图2是本发明积分电路原理图;

图3是本发明信号控制模块原理框架图;

图4是本发明信号控制模块中高源电压源电路示意图;

图5是本发明信号控制模块中高源电流源电路示意图;

图6是本发明信号控制模块中低源电压源电路示意图;

图7是本发明信号控制模块中低源电流源电路示意图;

图8是本发明功率输出模块电路原理图;

图9是本发明采样模块中普通电压采样电路图;

图10是本发明采样模块中差分电流采样电路图;

图11是本发明采样模块中普通电流采样电路图;

图12是本发明采样模块中高压采样电路图;

图13是本发明采样模块中大电流采样电路图;

图14是本发明实施例中滤波电路原理图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

如图1所示,本发明提供一种技术方案:一种半导体测试用多方式测试系统,包括PC主机1以及与PC主机1之间信号连接的DA模块2和AD模块3;

所述PC主机1通过DA模块2信号连接有信号控制模块4,所述信号控制模块4信号连接有功率输出模块5,所述功率输出模块5信号连接有测试模块6;

所述测试模块6用于完成测试器件7的测试作业;

所述测试模块6还信号连接有采样模块8,所述采样模块8信号连接有信号处理模块9,所述信号处理模块9通过AD模块3将测试信号反馈至PC主机1上,完成测试器件7的测试过程。

所述PC主机1内预设有测试软件,测试以IGBT的测试标准为依据进行编写,对测试反馈数据进行存储、显示和判断,并根据设计完成硬件加密功能,通过软件启动检测串口,在串口开起后发送检测指令,并根据相应规则返回检测代码,实现软硬件的结合加密,主要是对原有二进制文件格式分析、串口发送指令分析、串口指令的发送、文档发送校验的计算、直角坐标系的设计的实现。

测试软件采用多文档界面,可以同时编辑多个测试文件,互不影响,输入界面直观,操作简便,做了最大最小值的限制,防止输入过大的电流或电压参数造成设备损坏,当测试文件编辑完成后,可以进行保存,也可以直接发送进行测试,发送时有进度条提醒,发送完成后,进行测试。

所述DA模块2是选用16位并口输入的高速DAC709KH芯片,高速DAC709KH芯片将数据信号转化成模拟信号的电压量,其电压量是-10V~10V。

为了提高测试速度,采用脉冲测试,那么就需要DA模块2发出至少一个脉冲信号,在测试时加载在与测试模块6连接的测试器件7的电压越高,要求脉冲的上升时间就越慢,如果上升时间过快就会产生电流或电压的长时间震荡,致使被测量的信号也会出现震荡,而无法得到正确的测试结果;而如果上升时间过慢,又会要求功率源的设计处更大的功率,以适应脉冲功率的要求,在DA模块2出来后的信号增加了四组积分电路,具体如图2所示,以适应不同的测试时所需脉冲的上升时间的斜率。

所述信号控制模块4用于将信号分成低源信号和高源信号,并将其输出,低源信号分为低源电压源和低源电流源,高源信号分为高源电压源、高源电流源,具体如图3所示;

在使用过程中,外接220V交流电先经过变压器T变压,再经过整流桥整流为直流电,然后再经过电容C9和电容C10滤波成恒压。

一开始晶闸管Q12没有打开,输出电压为0,通过比较器U7A进行比较,阳极端这时大于5V,于是输出电压Q10导通,晶闸管Q12也被导通,这时电压输出到电容CF1上,当电容CF1充满电后电压继续上升,通过电阻R32和电阻R33分压后,当大于5V时,比较器U7B输出负电压,Q10截止,晶闸管Q12也跟着截止。

其稳压原理具体为,当电压过低时,电阻R32和电阻R34之间的电压降低,比较器U7A的输出电压上升,进而使得Q10输出电压升高,晶闸管Q12连通,即电压升高;

当电压过高时,电阻R32和电阻R34之间的电压升高,比较器U7A输出电压降低,进而使得Q10输出电压减低,晶闸管Q12关闭,即电压减低。

以上过程就可控制输出电压,又由于电容CF1使用了10mF大电容作为储能器件,在瞬间脉冲测试时可释放出大的电流,便于完成半导体器件的测试过程。

测试过程高源电压源时,简化原理图如图4所示;其中R113=R2116,R175=R176,图3中要加载电压到被测器件CE的两端,即VCE,VCE是由输入电压Ui控制的,只要在Ui加一个-10V~10V的电压,就能在CE产生-2000V~+2000V电压,由于U121是跟随器,所以

Va=VE

又因为R176=R175,U129是反相器,所以

Vd=-VE

根据运放公式得

因为R113=R2116,带入上式得

可看出加在被测器件上的电压是有控制电压Ui所决定的,并和Ui线性变化,在实际使用当中,分了三个档位,分别是0~10V;0~100V;0~2000V。运行良好,加载电压准确。

测试过程高源电流源时,简化原理图如图5所示;

图中要加载电流流过被测器件,即ICE。ICE是由输入电压Ui控制的。只要在Ui加一个-10V~10V的电压,就能在CE产生最大-1250A~+1250A电流。因为R220和被测器件串联,所以流过R220的电流等于ICE。

因U210是跟随器,所以

Vf=VE

根据运放公式得

IE和电阻R220的电流就是

带入上式得

从上式中可看出,加在被测器件上的电流是由控制电压Ui所决定的,并和Ui线性变化,在实际使用当中,分了11个档位,分别是0~1uA;0~10uA;0~100uA;0~1mA;0~10mA;0~100mA;0~1A;0~10A;0~50A;0~500A;0~1250A,运行良好,加载电压准确。

测试过程低源电压源时,简化原理图如图6所示;

图中要加载电压到被测器件GE的两端,即VGE。VGE是由输入电压Ui控制的。只要在Ui加一个-10V~10V的电压,就能在GE产生-20V~+20V电压。

分析方法同高源电压源类似,最终公式为:

可看出加在被测器件上的电压是有控制电压Ui所决定的,并和Ui线性变化。

测试过程低源电流源时,简化原理图如图7所示;

图中要加载电流流过被测器件,即IGE,IGE是由输入电压Ui控制的,只要在Ui加一个-10V~10V的电压,就能在GE产生-10A~+10A电流;

分析方法同高源电流源类似,最终公式为

可看出加在被测器件上的电流是由控制电压Ui所决定的,并和Ui线性变化。

在实际使用当中,分了8个档位,分别是0~1uA;0~10uA;0~100uA;0~1mA;0~10mA;0~100mA;0~1A;0~10A,运行良好,加载电压准确.

所述功率输出模块5是信号放大成所需要的功率信号输出到测试模块6上,具体如图8所示,功率输出模块采用三级推挽方式,由信号控制模块发出的电流信号,先推动偏置放大的晶体管MJE340,如果电流达不到晶体管MJE340的开启电流,此时三级放大全部截止,运放将直接输出。

如果电流达到晶体管MJE340的开启电流,此时偏置放大工作,晶体管MJE340输出信号到中级放大,中级放大的晶体管MJE15030和晶体管MJE15031工作,同样如果电流达不到MJE15031的开启电流后中级放大不工作,晶体管MJE340放大输出,以此类推最终驱动四个功率输出放大的晶体管MJE4343输出电流,级级放大,用一个功放可兼容微小电流和大电流,最小电流达到100nA,最大电流可达50A,提高了测试过程中的精准度和可靠性,提高了测试的效率。

所述测试模块6与功率输出模块5配合使用,完成测试器件7的测试。

所述采样模块8包括电压信号或电流信号的采样,用于电压或电流加载到与测试器件7连接的测试模块6上后,将测试模块6上产生的测量的电压信号或电流信号进行采集。

所述采样模块8的采样方式分为普通电压采样、差分电流采样、普通电流采样、高压采样和大电流采样。

普通电压采样电路具体如图9所示,对于线路中一般不超过50V的低电压采样,采用普通电压采样,它是一个标准的差分放大电路,即将CE两端的的电压放大输出。

差分电流采样电路图具体如图10所示,对于低源线路中一般不超过20A采用普通差分电流采样,它是一个标准的差分放大电路,这里因为流过采样电阻的电流和被测器件的电流相等,所以采样的到采样电阻的电流就是流过被测器件的电流。又因为采样电阻的组织是一定的,所以只要得到采样电阻的电压再经过下式可得到电流。

式中I是流过采样电阻的电流(流过被测器件的电流),U是采样电阻的电压,R是采样电阻的阻值。

普通电流采样电路原理图具体如图11所示,对于高源线路中一般不超过50A时,采用普通电流采样计算方式同差分电流采样。

高压采样电路图如图12所示,因测试高压时因电压比较高,如果直接像普通的电压差分采样的方法采样时,就把采样的运放烧掉,所以电压在经过运放之前进行比例分压,将原电压按比例减小到运放不至于烧坏的电压,测试机中不超过10V。

大电流采样电路图如图13所示,当电流大于50A时,这时采样电阻的阻值非常小,约为0.001,如此小的阻值,电阻的精度很难达到0.1%,所以采用分流累加的方式进行设计,分了10组采样电路,每组采样电路对应一组电流源,这样既能准确采样,又不至于每组电流分配不均匀烧坏器件,经过以上的采样模块8的各个电路设计,能准确的测试出电流和电压的大小,而且采样的准确性直接关系到测试精度,所以PC主机1在发出测量脉冲后的2/3出采样,这样可避免脉冲在初始状态时的震荡。

所述信号处理模块9是将采样模块8的信号进行判断,分别判断出电压信号还是电流信号,并放大或缩小成标准的电压信号输送至AD模块3上,

所述AD模块3还连接有滤波电路,具体如图14所示,滤波电路分为低通滤波和高通滤波,低通滤波是由运放组成的低通滤波器,高通滤波是UAF42AP滤波芯片。

所以AD模块3具体为16位的高速ADC700KP芯片,采样速度是2uS,且在高速ADC700KP芯片前加有采样保持器SHC5320KP,用于保证信号的稳定性,再将信号反馈至PC主机1上。

为了提高测试速度,还设置有扫描测试和适配器,利用PC主机1进行控制,每次测试前现将相应的继电器吸合到需要测试的单元上,编程容易方便,一次可测量多个器件,对于多封装器件测试速度尤为突出。

需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。

尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

- 一种半导体测试用多方式测试系统

- 一种基于半导体芯片自动测试系统的万能手测器