数模转换器

文献发布时间:2023-06-19 18:32:25

技术领域

本公开涉及一种数模转换器DAC。具体地,本公开涉及具有电阻器梯形布置和用作缓冲器的放大器的DAC,其中电阻器梯形布置包括:包括最低有效位节段的第一节段、包括最高有效位节段的第二节段和第三节段。

背景技术

缓冲电压型DAC是DAC系列的重要组成。例如就线性而言的准确性和速度是关键特征。

发明内容

根据本公开的第一方面,提供一种数模转换器DAC,包括:

放大器,所述放大器用于形成所述DAC的缓冲器,所述放大器包括反相输入端和非反相输入端以及用于提供所述DAC的输出的输出端,其中所述反相输入端经由第一电阻器耦合到第一基准电压端,所述第一基准电压端被配置成接收第一基准电压,并且其中所述输出端经由第二电阻器耦合到所述反相输入端;以及

电阻器梯形布置,所述电阻器梯形布置耦合到所述放大器的所述非反相输入端且被配置成基于数字控制字在所述非反相输入端处生成电压,其中所述电阻器梯形布置包括:

i)第一节段,所述第一节段包括多个第一节段电阻器和一个或多个第一开关,所述第一节段耦合到所述放大器的所述非反相输入端,并且所述一个或多个第一开关中的每一个被配置成单独地且选择性地将所述多个第一节段电阻器中的相应第一节段电阻器耦合到所述第一基准电压端或第二基准电压端,所述第二基准电压端被配置成接收不同于所述第一基准电压的第二基准电压,并且其中所述多个第一节段电阻器和所述一个或多个第一开关被布置成R-2R配置和单元-R配置之一;

ii)第二节段,所述第二节段包括一个或多个单元,每个单元包括具有第一电阻器端和第二电阻器端的第二节段电阻器,其中所述第二电阻器端耦合到相应第二开关,其中所述一个或多个单元通过所述一个或多个单元中的每一个的所述第二节段电阻器的所述第一电阻器端并联耦合到所述非反相输入端,其中每个相应第二开关被配置成单独地且选择性地将相应第二电阻器端耦合到所述第一基准电压端或所述第二基准电压端,其中所述第二节段的所述一个或多个单元的每个第二节段电阻器具有第二电阻值R

iii)第三节段,所述第三节段包括一个或多个第三节段电阻器,所述第三节段的所述一个或多个第三节段电阻器中的每一个具有第一电阻器端和第二电阻器端,其中所述第三节段的所述一个或多个第三节段电阻器中的每一个通过其第一电阻器端并联耦合到所述非反相输入端且通过其第二电阻器端连接到所述第一基准电压端,其中所述第三节段的所述一个或多个第三节段电阻器具有总第三电阻值,所述总第三电阻值基于所述第二电阻值和用于控制所述第二节段的所述一个或多个单元的所述第二开关的所述数字控制字中的位数;并且

其中所述第一节段的所述第一开关被配置成由所述数字控制字的第一部分控制,所述第一部分包括所述数字控制字的一个或多个最低有效位,并且所述第二节段的所述第二开关被配置成由所述数字控制字的第二部分控制,所述第二部分包括所述数字控制字的一个或多个最高有效位,且由此对所述第一开关和所述第二开关的控制控制所述DAC在所述输出端处的所述输出。

在一个或多个例子中,所述第三节段包括两个或更多个第三节段电阻器。

在一个或多个例子中,所述第三节段用于提供对可变IR压降的抗扰性。在一个或多个例子中,所述第三节段用于改善所述DAC的总不可调整误差。在一个或多个例子中,所述第一节段形成最低有效位节段。在一个或多个例子中,所述第二节段形成最高有效位节段。

在一个或多个实施例中,Rsp=R

在一个或多个例子中,所述多个第一节段电阻器之一包括终端电阻器,并且所述多个第一节段电阻器中的其余电阻器与所述一个或多个第一开关形成所述R-2R配置和所述单元-R配置之一,其中所述终端电阻器包括耦合到所述R-2R配置和所述单元-R配置之一的第一电阻器端且包括耦合到所述第一基准电压端的第二电阻器端。

在一个或多个实施例中,所述第一节段的R-2R布置包括布置成链的一个或多个第一节段单元,其中

所述一个或多个第一节段单元中的第一个第一节段单元包括所述多个第一节段电阻器中的具有电阻R

其中所述一个或多个第一节段单元中的每个后一第一节段单元包括所述多个第一节段电阻器中的具有电阻R

其中所述第一节段包括所述多个第一节段电阻器中的终端电阻器,所述终端电阻器具有耦合到布置在所述链中的最末第一节段单元的所述中间节点的第一电阻器端和耦合到所述第一基准电压端的第二电阻器端。

在一个或多个实施例中,所述电阻2R

在一个或多个实施例中,所述第一节段的单元-R布置包括布置成链的一个或多个第一节段单元,其中

所述一个或多个第一节段单元中的第一个第一节段单元包括所述多个第一节段电阻器中的具有电阻R

其中所述一个或多个第一节段单元中的每个后一第一节段单元包括所述多个第一节段电阻器中的第一单元电阻器,所述第一单元电阻器具有电阻2.R

其中所述第一节段另外包括所述多个第一节段电阻器中的终端电阻器,所述终端电阻器具有耦合到所述第一节段单元中的所述第一个第一节段单元的所述中间节点的第一电阻器端和耦合到所述第一基准电压端的第二电阻器端。

在一个或多个实施例中,所述电阻R

其中L包括第一节段单元的数量。

在一个或多个实施例中,所述第一节段的总输出阻抗等于R

在一个或多个实施例中,所述第三节段中的第三节段电阻器的数量等于2

在一个或多个实施例中,所述第三节段中的第三节段电阻器的数量等于2

在一个或多个实施例中,所述放大器被配置成借助于耦合到第三基准电压端和第四基准电压端而获得电力,其中所述第三基准电压端被配置成接收等于或大于所述第二基准电压的电源电压,并且所述第四基准电压端被配置成接收接地基准电压,并且所述第一基准电压等于或大于所述接地基准电压。

在一个或多个实施例中,所述第四基准电压端被配置成耦合到接地基准电压,并且所述缓冲器的所述第一电阻器的电阻等于所述缓冲器的所述第二电阻器的电阻。

在一个或多个例子中,所述放大器被配置成使得在所述输出端处提供的电压VO_DAC如下:

在一个或多个实施例中,所述DAC包括被配置成接收所述数字控制字的所述第二部分的二进制到温度计解码器,来自所述二进制到温度计解码器的输出被配置成控制所述第二节段的所述第二开关。

在一个或多个实施例中,所述第一节段包括单元-R配置,并且所述DAC包括被配置成接收所述数字控制字的所述第一部分的第二二进制到温度计解码器,来自所述第二二进制到温度计解码器的输出被配置成控制所述第一节段的所述第一开关。

在一个或多个实施例中,所述第一节段包括R-2R配置,并且所述DAC包括延迟均衡器,所述延迟均衡器被配置成从控制器接收所述数字控制字的所述第一部分,来自所述延迟均衡器的输出被配置成控制所述第一节段的所述第一开关。

在一个或多个实施例中,所述一个或多个第三节段电阻器中的至少一个使其第二电阻器端经由第三开关耦合到所述第一基准电压端,所述第三开关被配置成使至少一个或多个第三电阻器与所述第一基准电压端选择性地连接或断开连接。

虽然本公开容许各种修改和替代形式,但其细节已经借助于例子在图式中示出且将进行详细描述。然而,应理解,除所描述的具体实施例以外的其它实施例也是可能的。也涵盖落在所附权利要求书的精神和范围内的所有修改、等效物和替代实施例。

以上论述并非旨在表示当前或未来权利要求集的范围内的每一示例实施例或每一实施方案。以下附图和具体实施方式还举例说明了各种示例实施例。结合附图考虑以下详细描述可以更全面地理解各种示例实施例。

附图说明

现将仅借助于例子参考附图来描述一个或多个实施例,在附图中:

图1示出了本公开的DAC的第一示例实施例;

图2示出了本公开的DAC的示例放大器或缓冲器;

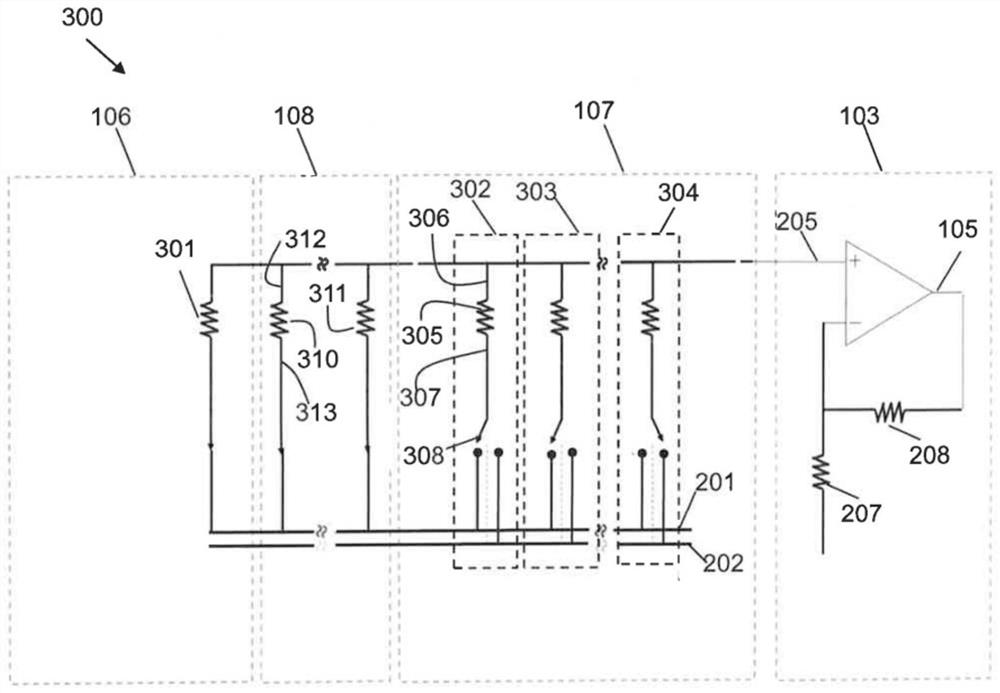

图3示出了本公开的DAC的第二示例实施例;

图4示出了本公开的DAC的第三示例实施例,其中第一节段包括R-2R配置;并且

图5示出了本公开的DAC的第四示例实施例,其中第一节段包括单元-R配置或“节段单元-R”配置。

具体实施方式

本公开涉及一种数模转换器DAC,且具体地涉及一种缓冲电压型DAC。此DAC可能需要平衡准确性、速度和电流消耗。

DAC可以使用电阻器和开关的电阻器梯形布置以根据数字控制字选择性地将电阻器耦合到不同基准电压。因此,数字控制字中的每一位,其中数字控制字可以控制开关中的相应一个(或多个)开关的动作,如下文将描述。电阻器梯形布置有效地包括互连的分压器集合,每个分压器在电阻梯形布置的输出处产生输出电压。因此,通过开关将电阻器梯形布置的电阻器选择性地耦合到至少两个不同基准电压提供了将要基于数字控制字产生的电压。电阻梯形布置的输出可以被提供到缓冲器,所述缓冲器可以体现为运算放大器。

图1示出了包括电阻器梯形布置101的DAC 100,所述电阻器梯形布置101被配置成基于在包括数字控制字的数字输入104处接收到的数字控制字在缓冲器103的输入102处提供输出电压。缓冲器103可以包括运算放大器。缓冲器103的输出105形成DAC的模拟输出。电阻器梯形布置101包括多个电阻器和多个开关。开关由数字控制字的位控制,并且确定其耦合到的电阻器是否连接到第一基准电压或第二基准电压。第一基准电压可以是低于第二基准电压的电压。第一基准电压和第二基准电压均可以是正电压(或第一基准电压可以是接地)。

在本例子中,电阻梯形布置101被分成第一节段106和第二节段107。在其它例子中,可以提供一个或多个另外的节段以接收数字控制字的在较低有效位与最高有效位之间的位。第一节段106包括最低有效位节段或LSB节段,且因而被配置成接收数字控制字的包括数字控制字的最低有效位的较低有效位中的一个或多个。第二节段107包括最高有效位节段或MSB节段,且因而被配置成接收比数字控制字的较低有效位更高的包括数字控制字的最高有效位的有效位中的一个或多个。因此,对于位为B

图2示出了缓冲器103的更多细节,并且示出了简化的电阻梯形布置101。电阻梯形布置101耦合到第一基准电压端201,或具体地电阻梯形布置101的多个开关中的每一个的端耦合到第一基准电压端201。第一基准电压端201被配置成接收第一基准电压。电阻梯形布置101耦合到第二基准电压端202,或具体地开关中的每一个的另外的端耦合到第二基准电压端202。第二基准电压端202被配置成接收第二基准电压。

缓冲器103可以体现为运算放大器203。放大器203包括反相输入端204和非反相输入端205以及用于提供DAC的输出105的输出端206。反相输入端204经由第一电阻器Rfb1207耦合到第一基准电压端201。第一基准电压端201被配置成接收第一基准电压VL。输出端206经由第二电阻器Rfb2 208耦合到反相输入端204。因此,第二电阻器208在输出206与反相输入端204之间形成反馈环路。第一电阻器207的第一端耦合在第二电阻器208与反相输入端204之间的节点209处。第一电阻器207的第二端耦合到所述第一基准电压端201。

放大器203借助于包括第三基准电压端210和第四基准电压端211的两个端获得电力。第三基准电压端210被配置成接收等于或大于第二基准电压VH的电源电压VDDA。第四基准电压端211被配置成接收接地基准电压。第一基准电压VL等于或大于接地基准电压。

在一个或多个例子中,第四基准电压端211被配置成耦合到接地基准电压,并且第一电阻器208的电阻等于第二电阻器207的电阻。

放大器203的第一电阻器207和第二电阻器208的布置使得在输出端206处提供的被称为VO_DAC的电压如下:

其中Rfb1为第一电阻器207的电阻,Rfb2为第二电阻器208的电阻,并且VO_LADDER为通过电阻器梯形布置101提供到非反相输入205的电压。

图3示出了DAC 300的示例实施例的更详细视图。放大器103示出为在非反相输入端102处耦合到电阻器梯形布置的节段106、107、108。

电阻器梯形布置101的第一节段106包括多个第一节段电阻器301(仅示出了一个,但在图4中示出为401-407且在图5中示出为501-505)和一个或多个第一开关(在图3中未示出,但在图4中示出为408-410且在图5中示出为506-508)。一个或多个第一开关408-410、506-508中的每一个被配置成单独地且选择性地将多个第一节段电阻器中的相应第一节段电阻器301、402、404、406、502-504耦合到第一基准电压端201或耦合到第二基准电压端202。多个第一节段电阻器301、401-407、501-505以及一个或多个第一开关408-410和506-508被布置成R-2R配置(在示例图4中示出)和单元-R配置(在示例图5中示出)之一。此类电阻器梯形配置对于基于电阻器梯的DAC领域的技术人员来说是已知的。

综上所述,R-2R配置包括布置成链的一个或多个单元421-423,每个单元包括两个第一节段电阻器,一个第一节段电阻器具有电阻R 401、403、405,并且另一个第一节段电阻器具有电阻2R 402、404、406。两个第一节段电阻器串联布置,其中2R第一节段电阻器耦合到第一开关408、409、410,并且其中一个或多个单元中的第一个单元通过R电阻器耦合到非反相输入205,并且每个后一单元耦合到链中的前一单元的节点424-426,所述节点定位在所述前一单元的R电阻器与2R电阻器之间。综上所述,本领域的技术人员还已知为节段-单元-R配置的单元-R配置包括通过一个电阻器端耦合到非反相输入端205的第一单元电阻器501以及并联耦合到节段电阻器的其它电阻器端的一个或多个另外的电阻器502-505,另外的电阻器中的每一个还耦合到相应第一开关506-508。

第一节段106中的被配置成接收数字控制字的较低位的开关的数量可以包括至少一个、至少两个、至少三个、至少四个,或至少五个或更多个。然而,在此例子中,变量M1表示用于控制第一节段106的数字控制字的位数(第一部分中的位数)对应于一个或多个第一开关的数量。

在示例图3中,R-2R配置和单元-R配置由电阻器301图解表示。然而,应了解,本公开的DAC 100、300、400、500包括作为第一节段106的一部分的至少一个第一节段电阻器,所述第一节段电阻器通过第一电阻器端耦合到非反相输入端205,并且其第二电阻器端通过一个或多个第一开关之一在耦合到第一基准电压端201与耦合到第二基准电压端202之间选择性地切换。下文将提供R-2R配置和单元-R配置的更全面描述。

图3所示的第二节段107包括一个或多个单元302、303、304。在一个或多个例子中,第二节段107可以被视为包括单元-R配置。每个单元302、303、304在结构上基本相同,并且为简单起见,仅更详细地标记了单元302。具体地,每个单元包括具有第一电阻器端306和第二电阻器端307的第二节段电阻器305,其中第二电阻器端307耦合到相应第二开关308。一个或多个单元302、303、304通过一个或多个单元302、303、304中的每一个的第二节段电阻器305的第一电阻器端306并联耦合到非反相输入端205。一个或多个单元302、303、304的每个相应第二开关308被配置成单独地且选择性地将相应第二电阻器端307耦合到第一基准电压端201或第二基准电压端202。第二节段107的一个或多个单元302、303、304的第二节段电阻器305中的每一个具有第二电阻R

在一个或多个例子中,一个或多个单元的数量等于2

已发现,在一个或多个例子中,提供第三节段108可以提供对可变IR压降的抗扰性。IR压降可以被视为电流流过电阻器时所经历的电阻电压降,随着电阻值变化,电压降也随之变化,从而引起可变IR压降。已知IR压降会降低DAC的总不可调整误差(TUE),其中TUE给出简单表示DAC的线性的准确性的一个数字,包括积分非线性(INL)/偏移误差(EO)/增益误差(EG)。第三节段108包括一个或多个第三节段电阻器310、311。在一个或多个例子中,第三节段108包括两个或更多个第三节段电阻器310、311。第三节段108的一个或多个第三节段电阻器310、311中的每一个具有第一电阻器端312和第二电阻器端313(为简洁起见,仅第三节段电阻器310被标记为电阻器端)。第三节段108的一个或多个第三节段电阻器310、311中的每一个通过其相应第一电阻器端312并联耦合到非反相输入端205。第三节段电阻器310、311还通过其相应第二电阻器端307连接到第一基准电压端201。第三节段108的一个或多个第三节段电阻器具有总第三电阻Rsp,其中Rsp=R

在一个或多个其它例子中,Rsp=R

如上文所提及,第一节段106的所述一个或多个第一开关408-410、506-508和第二节段107的一个或多个第二开关308(图3中示出三个)被配置成由数字控制字(经由440、441和540、541)控制,并且由此控制DAC 100在输出端105处的输出。

示例图4更详细地示出了第一节段106,并且表示了所述第一节段106的任选R-2R配置。在图4的例子中,第一节段106包括三个第一开关408-410。第一节段接收经由缓冲器103提供DAC的输出的数字控制字的三个较低有效位,

一般来说,第一节段106的R-2R布置包括布置成链的一个或多个第一节段单元421、422、423,且因此链中的第二个第一节段单元耦合到链中的第一个第一节段单元,并且链中的第三个第一节段单元耦合到链中的第二个第一节段单元,等等。因此,第一节段单元可以被视为彼此串联耦合。在此例子中,示出了三个第一节段单元421、422、423,但应了解,本公开不限于三个第一节段单元421、422、423。

一个或多个第一节段单元中的第一单元421包括上述多个第一节段电阻器中的具有电阻R

第一单元421还包括第一单元开关408,所述第一单元开关408包括先前提及的一个或多个第一开关之一。第一单元电阻器401耦合在非反相输入端205与第一节段单元的第一单元421的中间节点424之间,并且第二单元电阻器402耦合在中间节点424与所述第一单元开关408之间。

一个或多个第一节段单元的每个后一第一节段单元422、423与对应开关409、410的包括“R”和“2R”电阻器的类似布置。因此,每个后一第一节段单元422、423包括具有电阻R

因此,考虑到第一节段单元的第二单元422,所述第二个第一节段单元422的第一单元电阻器403耦合在第一个第一节段单元421的中间节点424与其自身的中间节点425之间,并且所述第二个第一节段单元422的第二单元电阻器404耦合在中间节点425与第二单元开关409之间。

现在,考虑到第一节段单元的第三单元423,所述第三个第一节段单元423的第一单元电阻器405耦合在第二个第一节段单元422的中间节点425与其自身的中间节点426之间,并且所述第三个第一节段单元423的第二单元电阻器406耦合在中间节点426与第三单元开关410之间。

如先前所提及,第一单元开关408、第二单元开关409和第三单元开关410被配置成将相应的第二单元电阻器402、404、406耦合到第一基准电压端201或第二基准电压端202。

在此和其它例子中,第一节段106还包括多个第一节段电阻器中的终端电阻器407,所述终端电阻器407具有耦合到布置在链中的最末第一节段单元(即,在此例子中为第三个第一节段单元423)的中间节点426的第一电阻器端以及耦合到第一基准电压端201的第二电阻器端。

在一个或多个例子中,一个或多个第一节段单元的第一单元421的第一单元电阻器401是任选的。因此,在一个或多个例子中,一个或多个第一节段单元的第一单元421可以具有2R电阻器402而不具有“R”电阻器401,而第一节段单元的第二单元422和第三单元423等确实具有上文所描述的R-2R布置。

在一个或多个例子中,当第一节段106具有R-2R布置时,电阻2R

转而参看图5,示出了单元-R布置。在一个或多个例子中,第一节段106的单元-R布置包括布置成链的一个或多个第一节段单元。在此例子中,包括三个第一节段单元521、522和523的第一单元521。第一节段单元521、522和523的第二单元向前均并联耦合到第一节段单元的第一单元521。

因此,在一个或多个例子中,一个或多个第一节段单元的第一单元521包括具有电阻R

第一单元电阻器501耦合在非反相输入端205与第一节段单元的第一单元521的中间节点524之间,并且第二单元电阻器502耦合在中间节点524与所述第一单元开关506之间。如先前所提及,一个或多个第一节段单元的第一单元521的第一单元开关506被配置成将相应的第二单元电阻器502耦合到第一基准电压端201或第二基准电压端202。

我们现在考虑包括一个或多个第一节段单元的后一第一节段单元的第二个第一节段单元522和第三个第一节段单元523。第二个第一节段单元522和第三个第一节段单元523分别各自包括第一单元电阻器503、504(即,其包括多个第一节段电阻器的电阻器),并且所述第一单元电阻器503、504各自具有电阻2.R

另外,第一节段106另外包括终端电阻器505(其包括多个第一节段电阻器之一),所述终端电阻器505具有耦合到第一节段单元的第一单元521的中间节点524的第一电阻器端和耦合到第一基准电压端201的第二电阻器端。

电阻R

在一个或多个例子中,第一节段106的总输出阻抗等于R

因此,图4和5示出了第一节段106的两个替代配置,但第二节段107和第三节段108具有相同布局。

在例如示例图3所示的一个或多个例子中,第三节段108包括直接耦合到第一基准电压端201的一个或多个第三节段电阻器310、311(图3中的两个)。在例如示例图4和5所示的一个或多个例子中,第三节段108包括通过开关430、530选择性地耦合到第一基准电压端201的一个或多个第三节段电阻器(一个在图4中示出在431处,一个在图5中示出在531处)。可以提供控制器442、542以控制开关430、530,且由此使第三节段电阻器431、531与第一基准电压端201连接和断开连接。当断开连接时,第三节段电阻器431、531不连接到任何其它组件。开关430和530可以被配置成选择性地将一个或多个第三节段电阻器431耦合到第一基准电压端201,使得第三节段108的一个或多个第三节段电阻器具有总、集合第三电阻Rsp,其中Rsp=R

在一个或多个例子中,第三节段中的第三节段电阻器310、311、431、531的数量等于2

在一个或多个例子中,第三节段可以通过分裂电阻器布置提供,如下文所描述。在一个或多个例子中,第三节段中的第三节段电阻器310、311、431、531的数量等于2

在一个或多个例子中,并且如图4和图5所示,DAC 100包括被配置成从控制器(未示出)接收数字控制字的二进制到温度计解码器440、540。来自二进制到温度计解码器440、540的输出被配置成控制第二节段107的第二开关411、412、413、511、512、513。二进制到温度计解码器440、540接收数字控制字的最高有效位和数字控制字中与所述最高有效位相邻的位,所述位包括数字控制字中的最有效的位。二进制到温度计解码器440、540输出用于控制第二节段107的第二开关411、412、413、511、512、513的数量的多个单独的控制信号。

在其中第一节段106包括单元-R配置的例子中,DAC 100包括被配置成从控制器(未示出)接收数字控制字的第二二进制到温度计解码器541。来自第二二进制到温度计解码器541的输出被配置成控制第一节段的第一开关506、507、508。二进制到温度计解码器541接收数字控制字的最低有效位和数字控制字中与所述最低有效位相邻的位,所述位包括数字控制字中的较低有效位。二进制到温度计解码器541输出用于控制第一节段106的第一开关506、507、508的多个单独的控制信号。

在其中第一节段106包括R-2R配置的例子中,DAC 100包括延迟均衡器441,所述延迟均衡器被配置成从控制器(未示出)接收控制信号。来自延迟均衡器441的输出被配置成控制第一节段106的第一开关408、409、410。延迟均衡器441接收到的数字控制字包括数字控制字的最低有效位和数字控制字中与所述最低有效位相邻的位,所述位包括数字控制字中的较低有效位。二进制到温度计解码器541输出用于控制第一节段106的第一开关506、507、508的多个单独的控制信号。在一个或多个例子中,延迟均衡器接收M1个位,并且可以提供2

除非明确陈述特定次序,否则可以任何次序执行以上附图中的指令和/或流程图步骤。同样,本领域的技术人员将认识到,虽然已经论述了一个示例指令集/方法,但本说明书中的材料可以多种方式组合以还产生其它例子,并且应在此详细描述提供的上下文内来进行理解。

在一些示例实施例中,上文描述的指令集/方法步骤实施为体现为可执行指令集的功能和软件指令,所述可执行指令集在计算机或以所述可执行指令编程且受所述可执行指令控制的机器上实现。此类指令被加载以在处理器(例如,一个或多个CPU)上执行。术语处理器包括微处理器、微控制器、处理器模块或子系统(包括一个或多个微处理器或微控制器),或其它控制或计算装置。处理器可以指单个组件或多个组件。

在其它例子中,本文中示出的指令集/方法以及与其相关联的数据和指令存储在相应存储装置中,所述存储装置被实施为一个或多个非暂时性机器或计算机可读或计算机可用存储介质。此类计算机可读或计算机可用存储介质被视为物品(或制品)的部分。物品或制品可以指任何制造的单个组件或多个组件。如本文所定义的非暂时性机器或计算机可用介质不包括信号,但此类介质能够接收并处理来自信号和/或其它暂时性介质的信息。

本说明书中论述的材料的示例实施例可以整体或部分地通过网络、计算机或基于数据的装置和/或服务实施。这些可以包括云、因特网、内联网、移动装置、台式计算机、处理器、查找表、微控制器、消费者设备、基础架构,或其它启用装置和服务。如本文和权利要求书中可以使用的,提供以下非排他性定义。

在一个例子中,使本文所论述的一个或多个指令或步骤自动化。术语自动化或自动(和其类似变型)意指使用计算机和/或机械/电气装置控制设备、系统和/或过程的操作,而不需要人为干预、观测、努力和/或决策。

应了解,据称将耦合的任何组件可以直接或间接地耦合或连接。在间接耦合的状况下,可以在据称将耦合的两个组件之间定位额外的组件。

在本说明书中,已经依据选择的细节集呈现了示例实施例。然而,本领域的普通技术人员将理解,可以实践包括这些细节的不同选择集合的许多其它示例实施例。希望所附权利要求书涵盖所有可能的示例实施例。

- 用于校准多比特数模转换器的方法,应用这种方法的多比特数模转换器以及具有这样的多比特数模转换器的转换器

- 一种数模转换器、数模转换器的失配校准方法及芯片