一种芯片测试筛选方法

文献发布时间:2023-06-19 11:00:24

技术领域

本发明涉及集成电路芯片测试领域,具体涉及一种芯片测试筛选方法。

背景技术

芯片的工艺制程的不断缩小,为了缩减制造成本,在芯片制造中,相邻位线(英文为bitline)的间距变得越来越小,部分芯片在工艺发生偏差时,相邻位线间的介质在持续高压下可靠性变差,在使用过程中介质因高压被击穿。现有的对位线短路(应为为bitlineshort,请参阅图1所示,图1中虚线处即为bitline short)的测试方案,针对的是已发生的,即在未测试前已经发生的情况。本发明不仅可以筛选出测试前已发生,还可以筛选出未发生且在应用中有风险的芯片。

发明内容

本发明的目的在于提供一种芯片测试筛选方法,可在测试阶段将背景技术中提到的芯片筛除,采用高压及时间两个维度加速的方式将存在可靠性风险的芯片在测试阶段筛选出。

为了达到上述目的,本发明采用的技术方案如下:

一种芯片测试筛选方法,包括:

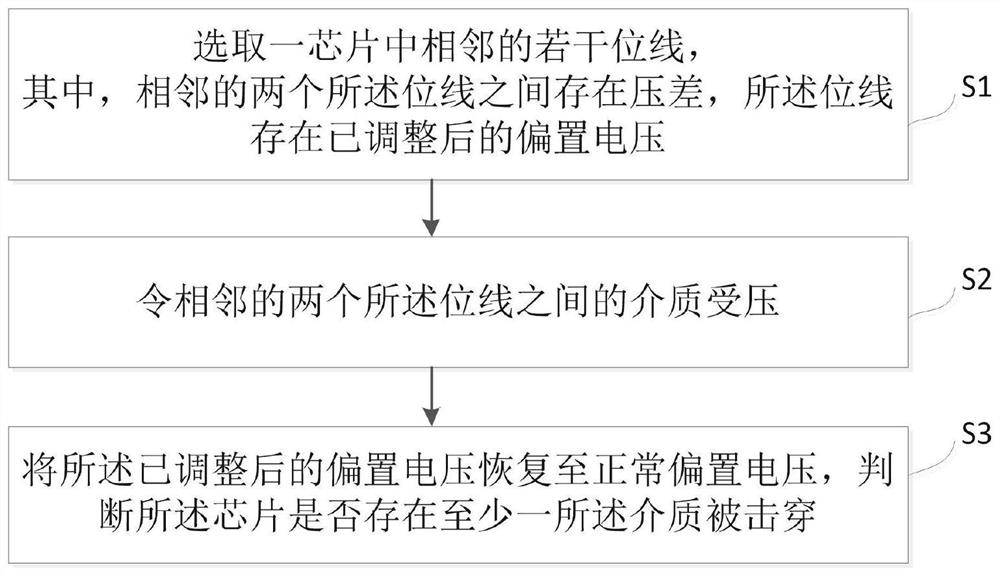

S1、选取一芯片中相邻的若干位线,其中,相邻的两个所述位线之间存在压差,所述位线存在已调整后的偏置电压;

S2、令相邻的两个所述位线之间的介质受压;

S3、将所述已调整后的偏置电压恢复至正常偏置电压,判断所述芯片是否存在至少一所述介质被击穿。

进一步地,所述步骤S1之前还包括:

通过写棋盘格数据的方式使所述芯片中所有的相邻的两个位线之间产生压差,其中,所述棋盘格由若干“1”和若干“0”,“1”的上下左右为“0”,“0”的上下左右为“1”。

进一步地,在写棋盘格数据时,所述位线处于正常的偏置电压。

进一步地,所述步骤S1之前还包括:

调整所述位线的偏置电压,以使相邻的两个所述位线的偏置电压分别调整至所述正常的偏置电压的正、负百分之一百三十。

进一步地,所述介质受压的时间为100ms~900ms。

进一步地,通过反复写棋盘格数据若干次,使相邻位线之间的介质受压。

进一步地,所述步骤S3具体包括:

将所述芯片的已调整后的偏置电压恢复至正常偏置电压;

对所述芯片所有的存储阵列进行擦写;

判断所述芯片是否能正确写入目标的棋盘格数据,若是,判定所述芯片为安全芯片,若否,判定所述芯片为失效芯片。

进一步地,所述芯片为存储芯片和/或控制芯片。

与现有技术相比,本发明至少具有以下优点之一:

(1)此类芯片的失效属于早期失效,可通过加大电压和加长时间来加速失效,筛选出以往在应用阶段才出现的可靠性风险芯片,不同批次中存在风险的芯片都能够筛选出。

(2)发生击穿后,恢复正常的偏置电压,此时位线上的电压产生压降,偏置电压不正确不能正确写入目标的棋盘格数据。

附图说明

图1为本发明一实施例中芯片测试筛选方法的结构示意图。

具体实施方式

以下结合附图1和具体实施方式对本发明作进一步详细说明。根据下面说明,本发明的优点和特征将更清楚。需要说明的是,附图采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施方式的目的。为了使本发明的目的、特征和优点能够更加明显易懂,请参阅附图。须知,本说明书所附图式所绘示的结构、比例、大小等,均仅用以配合说明书所揭示的内容,以供熟悉此技术的人士了解与阅读,并非用以限定本发明实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本发明所能产生的功效及所能达成的目的下,均应仍落在本发明所揭示的技术内容能涵盖的范围内。

需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、芯片测试筛选方法、物品或者现场设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、芯片测试筛选方法、物品或者现场设备所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括所述要素的过程、芯片测试筛选方法、物品或者现场设备中还存在另外的相同要素。

请参阅图1所示,本实施例提供的一种芯片测试筛选方法,芯片的位线上的任何位置均可能发生短路,本方法可以有效地将此类芯片筛选出,该方法包括:

S1、选取一芯片中相邻的若干位线,其中,相邻的两个所述位线之间存在压差,所述位线存在已调整后的偏置电压;

S2、令相邻的两个所述位线之间的介质受压,其中,介质受压范围是4V~5.5V;

S3、将所述已调整后的偏置电压恢复至正常偏置电压,判断所述芯片是否存在至少一所述介质被击穿,若是,判定所述芯片为失效芯片,若若,判定所述芯片为安全芯片。

本实施例中,所述步骤S1之前还包括:

通过写棋盘格数据的方式使所述芯片中所有的相邻的两个位线之间产生压差,其中,所述棋盘格由若干“1”和若干“0”间隔组成,即“1”的上下左右为“0”,“0”的上下左右为“1”,“1”表示+5V,“0”表示0V,相邻的“1”与“0”之间的压差为5V。

本实施例中,在写棋盘格数据时,所述位线处于正常的偏置电压。

本实施例中,所述步骤S1之前还包括:调整所述位线的偏置电压,以使相邻的两个所述位线的偏置电压分别调整至所述正常的偏置电压的120%~140%,一个调整至原偏置电压的+130%,另一个调整至原偏置电压的-130%,该处需补充一个包含130%的范围(例120%~140%)。

本实施例中,所述介质受压的时间为100ms~900ms。

本实施例中,通过反复写棋盘格数据若干次,使相邻位线之间的介质受压,相对较弱的便会被高压击穿,产生电阻特性。

本实施例中,所述步骤S3具体包括:

将所述芯片的已调整后的偏置电压恢复至正常偏置电压;

对所述芯片所有的存储阵列进行擦写;

判断所述芯片是否能正确写入目标的棋盘格数据(该处的目标的棋盘格数据可与之前输入的棋盘格数据相同,通过判断能否输出与之前相同的棋盘格数据来判断该芯片是否为安全芯片),若是,判定所述芯片为安全芯片,若否,判定所述芯片为失效芯片。

本实施例中,所述芯片为存储芯片和/或控制芯片。

尽管本发明的内容已经通过上述优选实施例作了详细介绍,但应当认识到上述的描述不应被认为是对本发明的限制。在本领域技术人员阅读了上述内容后,对于本发明的多种修改和替代都将是显而易见的。因此,本发明的保护范围应由所附的权利要求来限定。

- 一种芯片测试筛选方法

- 一种APS芯片测试及筛选方法