一种箭载三模冗余计算机系统

文献发布时间:2023-06-19 18:30:43

技术领域

本发明涉及电气系统技术领域,尤其涉及一种箭载三模冗余计算机系统。

背景技术

运载火箭控制系统的性能直接影响火箭飞行的成败,箭载计算机作为控制系统的大脑,实现运载火箭的导航、制导、稳定计算以及飞行时序的控制,是运载火箭的核心关键设备。目前提高箭载计算机可靠性的方法多采用冗余体系架构,包括双模冗余、三模冗余以及更多模冗余架构,然而采用多模冗余架构必然带来成本及设计复杂度的翻倍增加,尤其是小型运载火箭以及商业运载火箭,对研制成本较为敏感。因此,设计一种高可靠、低成本的箭载冗余计算机,对运载火箭控制系统的可靠性及性价比的提升意义重大。

发明内容

鉴于上述问题,本发明提出了一种电路设计简易、控制策略简单的箭载三模冗余计算机系统,可实现冗余计算、故障屏蔽处理,具有可靠性高、成本低的优点。

本申请通过一实施例提供如下技术方案:

一种箭载三模冗余计算机系统,包括:第一处理器、第二处理器、第三处理器、三模输出权仲裁电路和三模故障屏蔽电路,所述第一处理器、所述第二处理器和所述第三处理器均与所述三模故障屏蔽电路和所述三模输出权仲裁电路连接,所述第一处理器、所述第二处理器和所述第三处理器之间两两互连;所述第一处理器,被配置为校验所述第二处理器和所述第三处理器的数据,输出第一判决信号;所述第二处理器,被配置为校验所述第一处理器和所述第三处理器的数据,输出第二判决信号;所述第三处理器,被配置为校验所述第一处理器和所述第二处理器的数据,输出第三判决信号;所述三模输出权仲裁电路,被配置为基于所述第一判决信号、所述第二判决号、第三判决信号以及输出权控制信号,向所述第一处理器或所述第二处理器输出输出权控制信号;所述输出权控制信号用于在所述第一处理器和所述第二处理器之间确定输出权;所述三模故障屏蔽电路,被配置为基于所述第一判决信号、所述第二判决信号和所述第三判决信号,向所述第一处理器、所述第二处理器或所述第三处理器输出故障复位信号;所述故障复位信号用于对故障处理器的复位。

可选的,所述三模输出权仲裁电路被配置为:

基于所述第二判决信号和所述第三判决信号均表征所述第一处理器故障时,则向所述第二处理器输出输出权控制信号,以将输出权从所述第一处理器转移至所述第二处理器;基于所述第一判决信号和所述第三判决信号均表征所述第二处理器故障时,则向所述第一处理器输出输出权控制信号,以将输出权从所述第二处理器转移至所述第一处理器。

可选的,所述三模故障屏蔽电路被配置为:

基于接收到所述第二判决信号和所述第三判决信号均表征所述第一处理器故障的次数,向所述第一处理器输出所述故障复位信号;基于接收到所述第一判决信号和所述第三判决信号均表征所述第二处理器故障的次数,向所述第二处理器输出所述故障复位信号;基于接收到所述第一判决信号和所述第二判决信号均表征所述第三处理器故障的次数,向所述第三处理器输出所述故障复位信号。

可选的,所述第一判决信号、所述第二判决信号和所述第三判决信号均为两路信号;

所述第一处理器被配置为:校验所述第一处理器的数据与所述第二处理器的数据不匹配时,生成第一路表征故障的第一判决信号;校验所述第一处理器的数据与所述第三处理器的数据不匹配时,生成第二路表征故障的第一判决信号;所述第二处理器被配置为:校验所述第二处理器的数据与所述第一处理器的数据不匹配时,生成第一路表征故障的第二判决信号;校验所述第二处理器的数据与所述第三处理器的数据不匹配时,生成第二路表征故障的第二判决信号;所述第三处理器被配置为:校验所述第三处理器的数据与所述第一处理器的数据不匹配时,生成第一路表征故障的第三判决信号;校验所述第三处理器的数据与所述第二处理器的数据不匹配时,生成第二路表征故障的第三判决信号。

可选的,所述三模输出权仲裁电路,包括:第一判决逻辑子电路、第二判决逻辑子电路和第三判决逻辑子电路、第一输出权三取二输出子电路和第二输出权三取二输出子电路;所述第一处理器、所述第二处理器和所述第三处理器均分别连接至所述第一判决逻辑子电路、第二判决逻辑子电路和第三判决逻辑子电路;所述第一判决逻辑子电路、所述第二判决逻辑子电路和所述第三判决逻辑子电路均分别连接至第一输出权三取二输出子电路和第二输出权三取二输出子电路;所述第一输出权三取二输出子电路连接至所述第一处理器的输出权控制端、第一判决逻辑子电路、所述第二判决逻辑子电路和所述第三判决逻辑子电路,所述第二输出权三取二输出子电路连接至第二处理器的输出权控制端、第一判决逻辑子电路、第二判决逻辑子电路和第三判决逻辑子电路;所述输出权控制信号包括第一赋权信号和第二赋权信号,所述第一赋权信号为第一输出权三取二输出子电路输出的信号,所述第二赋权信号为第二输出权三取二输出子电路输出的信号;所述第一判决逻辑子电路、所述第二判决逻辑子电路和所述第三判决逻辑子电路均被配置为:若所述第一赋权信号、所述第二赋权信号、所述第一判决信号、所述第二判决信号和所述第三判决信号表征所述第二处理器具备输出权且所述第二处理器故障时,则向所述第一输出权三取二输出子电路和第二输出权三取二输出子电路均输出第一仲裁信号;若所述第一赋权信号、所述第二赋权信号、所述第一判决信号、所述第二判决信号和所述第三判决信号表征所述第一处理器具备输出权且所述第一处理器故障时,则向所述第一输出权三取二输出子电路和第二输出权三取二输出子电路均输出第二仲裁信号;所述第一输出权三取二输出子电路被配置为,对所述第一仲裁信号进行三取二输出所述第一赋权信号;所述第二输出权三取二输出子电路被配置为,对所述第二仲裁信号进行三取二输出所述第二赋权信号。

可选的,所述三模故障屏蔽电路包括第一计数子电路、第二计数子电路和第三计数子电路;所述第一处理器与所述第二计数子电路及所述第三计数子电路连接,所述第二处理器与所述第一计数子电路及第三计数子电路连接,所述第三处理器与所述第一计数子电路及第二计数子电路连接;所述第一计数子电路与所述第一处理器的复位端连接,所述第二计数子电路与所述第二处理器的复位端连接,所述第三计数子电路与所述第三处理器的复位端连接;所述第一计数子电路被配置为:在确定所述第二判决信号和所述第三判决信号均表征所述第一处理器故障时,计数一次;计数次数大于预设次数时,向所述第一处理器输出所述故障复位信号;所述第二计数子电路被配置为:在确定所述第一判决信号和所述第三判决信号均表征所述第二处理器故障时,计数一次;计数次数大于预设次数时,向所述第二处理器输出所述故障复位信号;所述第三计数子电路被配置为:在确定所述第一判决信号和所述第二判决信号均表征所述第三处理器故障时,计数一次;计数次数大于预设次数时,向所述第三处理器输出所述故障复位信号。

可选的,所述第一计数子电路包括第一与门子电路、第一计数器和第一锁存器;所述第一与门子电路与所述第一计数器连接,所述第一计数器与所述第一锁存器连接;所述第一与门子电路被配置为基于所述第二判决信号和所述第三判决信号,确定所述第一处理器是否故障;所述第一计数器被配置为在确定所述第一处理器故障时计数一次;所述第一锁存器被配置为在所述第一计数器计数次数大于预设的第一计数次数时,向所述第一处理器输出所述故障复位信号;所述第二计数子电路包括第二与门子电路、第二计数器和第二锁存器;所述第二与门子电路与所述第二计数器连接,所述第二计数器与所述第二锁存器连接;所述第二与门子电路被配置为基于所述第一判决信号和所述第三判决信号,确定所述第二处理器是否故障;所述第二计数器被配置为在确定所述第二处理器故障时计数一次;所述第二锁存器被配置为在所述第二计数器计数次数大于预设的第二计数次数时,向所述第二处理器输出所述故障复位信号;所述第三计数子电路包括第三与门子电路、第三计数器和第三锁存器;所述第三与门子电路与所述第三计数器连接,所述第三计数器与所述第三锁存器连接;所述第三与门子电路被配置为基于所述第一判决信号和所述第二判决信号,确定所述第三处理器是否故障;所述第三计数器被配置为在确定所述第三处理器故障时计数一次;所述第三锁存器被配置为在所述第三计数器计数次数大于预设的第三计数次数时,向所述第三处理器输出所述故障复位信号。

可选的,箭载三模冗余计算机系统还包括机内高速总线;所述第一处理器、所述第二处理器和所述第三处理器各自校验的数据均包括输入的数字量信号和模拟量信号,输出的数字量信号和模拟量信号,处理器计算的过程结果,处理器接收的通信数据,以及处理器发送的通信数据;所述机内高速总线被配置为:将所述第二处理器和所述第三处理器的所述校验的数据传输给所述第一处理器;将所述第一处理器和所述第三处理器的所述校验的数据传输给所述第二处理器;将所述第一处理器和所述第二处理器的所述校验的数据传输给所述第三处理器。

可选的,箭载三模冗余计算机系统还包括机外总线,所述第一处理器、所述第二处理器和所述第三处理器均与所述机外总线连接;所述第一处理器、所述第二处理器和所述第三处理器中不具备输出权的处理器被配置为:通过所述机外总线监听并校验具备输出权的处理器发送的数据。

可选的,箭载三模冗余计算机系统还包括时钟同步电路;所述第一处理器、所述第二处理器和所述第三处理器的时钟同步端口均连接至所述时钟同步电路;所述时钟同步电路被配置为:同步所述第一处理器、所述第二处理器和所述第三处理器的时钟信号。

在本发明实施例中提供的一种箭载三模冗余计算机系统,其中第一处理器、第二处理器和第三处理器中每个处理器分别对另外两个处理器的数据进行校验,从而得到对应的第一判决信号、第二判决信号和第三判决信号;接着三模输出权仲裁电路基于第一判决信号、第二判决信号和第三判决信号以及输出权控制信号,向第一处理器或第二处理器输出输出权控制信号;从而在第一处理器和第二处理器之间确定输出权,输出权就可在第一处理器和第二处理器之间进行变换,能够保证在任意一个处理器出现故障时,整个电路的输出可靠性;此时,第三处理器仅仅作为校验判断的处理器,而不用于输出,可在降低设计复杂度及研制成本的同时保证具备高可靠冗余输出的能力;进一步的,三模故障屏蔽电路基于第一判决信号、第二判决信号和第三判决信号,向第一处理器、第二处理器或第三处理器输出强制故障复位信号,以停止故障处理器的工作,从而避免故障处理器影响整个系统的正常运行,保证系统运行的可靠。

上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

附图说明

通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本发明的限制。而且在整个附图中,用相同的参考符号表示相同的部件。在附图中:

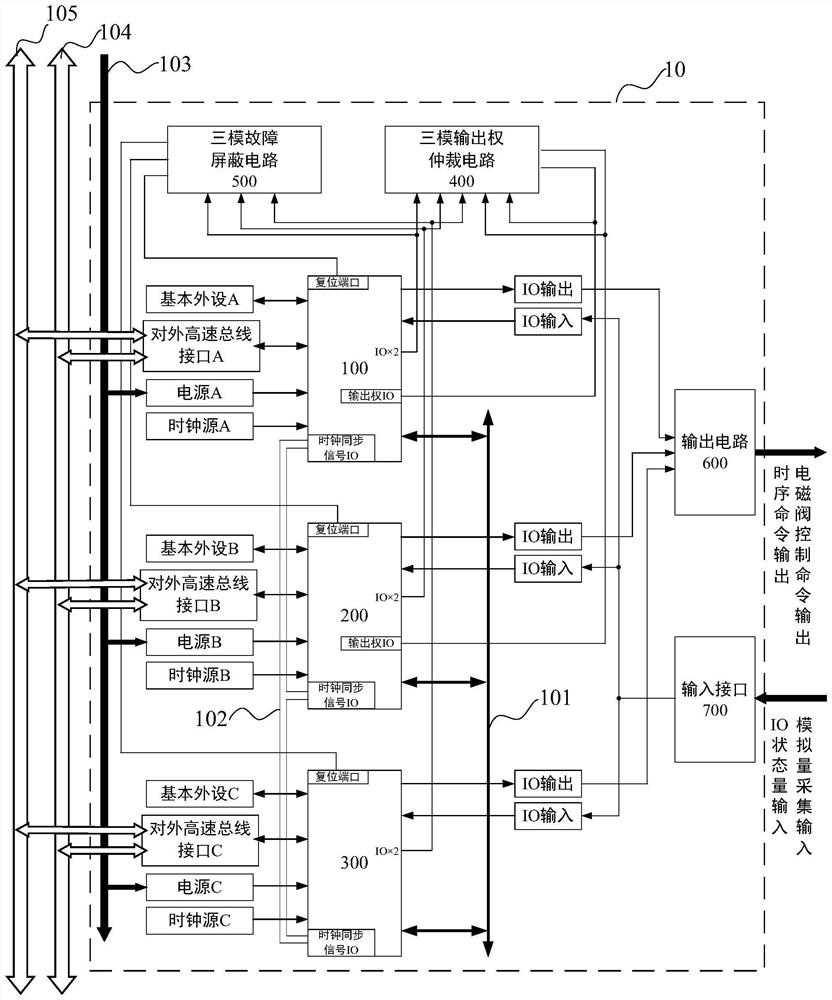

图1为本发明实施例中箭载三模冗余计算机系统的结构示意图;

图2为本发明实施例中机内高速总线的连接结构示意图;

图3为本发明实施例中三模输出权仲裁电路的结构示意图;

图4为本发明实施例中三模故障屏蔽电路的结构示意图;

图5为本发明实施例中时钟同步电路的结构示意图。

具体实施方式

下面将参照附图更详细地描述本公开的示例性实施例。虽然附图中显示了本公开的示例性实施例,然而应当理解,可以以各种形式实现本公开而不应被这里阐述的实施例所限制。相反,提供这些实施例是为了能够更透彻地理解本公开,并且能够将本公开的范围完整的传达给本领域的技术人员。

请参见图1,示出了本发明第一实施例提供的一种箭载三模冗余计算机系统10,包括:第一处理器100、第二处理器200、第三处理器300、三模输出权仲裁电路400和三模故障屏蔽电路500。

第一处理器100、第二处理器200和第三处理器300(为了便于表述,后文中一处理器可对应为一模)均与三模故障屏蔽电路500和三模输出权仲裁电路400连接。第一处理器100、第二处理器200和第三处理器300之间两两互连,具体的,可通过模间的机内高速总线101连接。第一处理器100、第二处理器200和第三处理器300均连接有各自独立的电源、时钟源、基本外设、对外高速总线。具体的,第一处理器100连接有电源A、时钟源A、基本外设A、对外高速总线接口A;第二处理器200连接有电源B、时钟源B、基本外设B、对外高速总线接口B;第三处理器300连接有电源C、时钟源C、基本外设C、对外高速总线接口C。

电源A、电源B和电源C通过机外(箭载三模冗余计算机系统10外)输入电源103进行供电,三模电源各自独立。

对外高速总线接口A、对外高速总线接口B和对外高速总线接口C同时连接机外总线,机外总线被配置为两路双冗余线路,用于数据冗余备份,三个处理器通过各自接口电路挂接在机外总线进行对外数据通信:三处理器通过机外总线监听并校验具备输出权的处理器发送的数据。机外总线包括第一机外冗余高速总线104和第二机外冗余高速总线105。通过上述的连接方式可实现机内(箭载三模冗余计算机系统10内)数据源冗余和机外的数据链路冗余,提高系统可靠性。

三个处理器周围基本外设均相同,可包括DDR(Double Data Rate,双倍速率同步动态随机存储器)、FLASH(FLASH在电子以及半导体领域内往往表示Flash Memory的意思,即平时所说的“闪存”,全名叫Flash EEPROM Memory。)、EMMC(Embedded Multi MediaCard,嵌入式多媒体卡)等等;结合电源、时钟源、基本外设、对外高速总线接口构成的电路后,每个处理器均能够独立实现箭载计算机的供电、飞控(包括导航、制导以及稳定)计算、对外通信及输入输出控制功能,在硬件功能上任何一模故障不会影响其他两模的正常工作。

在一些实现方式中,可通过配置在第一处理器100、第二处理器200和第三处理器300之间进行输出权的转移。但在本实施例中,可仅为第一处理器100和第二处理器200配置输出权,即输出权可在第一处理器100和第二处理器200之间转移。第一处理器100、第二处理器200和第三处理器300还可连接共同的输出电路600,该输出电路600可以是三取二硬件表决网络,以保证输出正确结果、屏蔽错误结果。当然,第一处理器100、第二处理器200和第三处理器300还可连接共同输入接口700,保证三个处理器能够同时接收到相同的输入量,通过三个处理器相互校验接收的输入量,可以剔除数据采集误差和故障错误,保证接收数据的正确性。

可以理解的,三个处理器输出的IO信号均通过三取二硬件表决网络输出,每模输出相同的两路IO输出量,分别控制两个开关,只有当两个及以上处理器的IO输出结果一致,正确的IO信号才能输出计算机外。输入信号包括IO输入量以及模量输入量,当机外的输入信号进入计算机内,通过输入接口700将同一信号分三路送给三模的每一模,保证三模都能收到该输入信号。

在一些实现方式中,第一处理器100被配置为校验第二处理器200和第三处理器300的数据,输出第一判决信号;第二处理器200被配置为校验第一处理器100和第三处理器300的数据,输出第二判决信号;第三处理器300被配置为校验第一处理器100和第二处理器200的数据,输出第三判决信号;三模输出权仲裁电路400,被配置为基于第一判决信号、第二校判决号、第三判决信号以及输出权控制信号,向第一处理器100或第二处理器200输出输出权控制信号;输出权控制信号用于在第一处理器100和所述第二处理器200之间确定输出权;三模故障屏蔽电路500被配置为基于第一判决信号、第二判决信号和第三判决信号,向第一处理器100、第二处理器200或第三处理器300输出故障复位信号;故障复位信号用于故障的处理器的强制复位。

在一些实现方式中,由于三模故障屏蔽电路500和三模输出权仲裁电路400均是独立工作的,并且还需要实现判断逻辑。因此,第一判决信号、第二判决信号和第三判决信号可均为两路信号。具体而言,第一处理器100被配置为:校验第一处理器100的数据与第二处理器200的数据不匹配时,生成第一路表征故障的第一判决信号;校验第一处理器100的数据与第三处理器300的数据不匹配时,生成第二路表征故障的第一判决信号;第二处理器200被配置为:校验第二处理器200的数据与第一处理器100的数据不匹配时,生成第一路表征故障的第二判决信号;第二处理器200的数据与第三处理器300的数据不匹配时,生成第二路表征故障的第二判决信号;第三处理器300被配置为:校验第三处理器300的数据与第一处理器100的数据不匹配时,生成第一路表征故障的第三判决信号;校验第三处理器300的数据与第二处理器200的数据不匹配时,生成第二路表征故障的第三判决信号。可以理解的,三个处理器通过机内高速总线101共享校验的数据,请参阅图2,输入的数字量信号和模拟量信号,输出的数字量信号和模拟量信号,处理器计算的过程结果,处理器接收的通信数据,以及处理器发送的通信数据。具体而言,机内高速总线101被配置为:将第二处理器200和第三处理器300的校验的数据传输给第一处理器100;将第一处理器100和第三处理器300的校验的数据传输给第二处理器200;将第一处理器100和第二处理器200的校验的数据传输给第三处理器300。这样就可实现任一处理器均可周期性的接收另外两个处理器的数据,并校验另外两个处理器的工作的正确性。校验时,可进行三取二比较,校验后可输出对应的判决信号。

应当理解的,每个处理器可通过对外高速总线接口与箭上两路机外总线相连,三个处理器均能接收机外总线发出的数据,但只有具有输出权的一处理器才允许对外发送数据。当具有输出权的一处理器对外发送数据时,另两个处理器可通过箭上两路机外总线同步监听该处理器发送的数据是否有误。若有误则生成对应的判决信号;若监听数据无误,则无动作继续保持监听状态。

在一些实现方式中,三模输出权仲裁电路400可被配置为:在第一处理器100具有输出权时,基于第二判决信号和第三判决信号均表征第一处理器100故障时,则向第二处理器200输出输出权控制信号,以将输出权从第一处理器100转移至第二处理器200;在第二处理器具有输出权时,基于第一判决信号和第三判决信号均表征第二处理器200故障时,则向第一处理器100输出输出权控制信号,以将输出权从第二处理器200转移至第一处理器100。因此,通过上述对第一处理器100和第二处理器200的故障判断,来输出对应的输出权控制信号,从而可实现输出权在第一处理器100和第二处理器200之间进行轮换,有效屏蔽故障器件、提高系统的稳定性。

请参阅图3,在一些实现方式中,三模输出权仲裁电路400接可包括:第一判决逻辑子电路410、第二判决逻辑子电路420和第三判决逻辑子电路430、第一输出权三取二输出子电路440和第二输出权三取二输出子电路450;第一处理器100、第二处理器200和第三处理器300均分别连接至第一判决逻辑子电路410、第二判决逻辑子电路420和第三判决逻辑子电路430。第一判决逻辑子电路410、第二判决逻辑子电路420和第三判决逻辑子电路430均分别连接至第一输出权三取二输出子电路440和第二输出权三取二输出子电路450;第一输出权三取二输出子电路440连接至第一处理器100的输出权控制端、第一判决逻辑子电路410、第二判决逻辑子电路420和第三判决逻辑子电路430,第二输出权三取二输出子电路450连接至第二处理器200的输出权控制端、第一判决逻辑子电路410、第二判决逻辑子电路420和第三判决逻辑子电路430;输出权控制信号包括第一赋权信号和第二赋权信号,第一赋权信号为第一输出权三取二输出子电路输出的信号,第二赋权信号为第二输出权三取二输出子电路输出的信号。

其中,第一判决逻辑子电路410、第二判决逻辑子电路420和第三判决逻辑子电路430功能相同、互为冗余,第一判决逻辑子电路410、第二判决逻辑子电路420和第三判决逻辑子电路430均被配置为:

若第一赋权信号、第二赋权信号、第一判决信号、第二判决信号和第三判决信号表征第二处理器200具备输出权且第二处理器200故障时,则向第一输出权三取二输出子电路440和第二输出权三取二输出子电路450均输出第一仲裁信号;第一输出权三取二输出子电路440被配置为,对第一仲裁信号进行三取二输出第一赋权信号,以使第一处理器100获得输出权;若第一赋权信号、第二赋权信号、第一判决信号、第二判决信号和第三判决信号表征第一处理器100具备输出权且第一处理器100故障时,则向第一输出权三取二输出子电路440和第二输出权三取二输出子电路450均输出第一仲裁信号;第二输出权三取二输出子电路450被配置为,对第二仲裁信号进行三取二输出第二赋权信号,以使第二处理器200获得输出权。也就是说,在同一时刻,第一处理器100和第二处理器200只能有一个接收到赋权信号。

换句话说,默认情况下向第一处理器100输出有效的第一赋权信号,第二赋权信号无效,当第二处理器200和第三处理器300同时判定第一处理器100的数据错误,并向三个判决子电路输出表征第一处理器100故障的判决信号时,第一处理器100的第一赋权信号失效,向第二处理输出有效的第二赋权信号,输出权由第一处理器100转向第二处理器200。同理,在第二处理器200具有输出权时,另第一处理器100和第三处理器300均判定第二处理器200的数据错误时,可向三个判决子电路输出表征第二处理器200故障的判决信号,输出权可由第二处理器200重新转为第一处理器100。在该种实现方式中,任一个处理器的故障不会影响系统的正常运行,正常处理器将获得输出权接替故障处理器的位置,主导系统继续正常、可靠的工作。

举个例子:以输出权由第一处理器100转换为第二处理器200为例进行说明。

三模输出权仲裁电路400的主要部分为第一判决逻辑子电路410、第二判决逻辑子电路420和第三判决逻辑子电路430三个八输入两输出的输出权判决逻辑电路,三个判决逻辑子电路功能相同、互为冗余,可选用分立与非门逻辑电路搭建。

判决逻辑子电路(410/420/430)八路输入信号分别为:

定义第一处理器100对第二处理200数据判决的结果记为第一判决信号的第一路信号“AB”,当第一处理器100接收第二处理器200发来的数据进行校验,当判断第二处理器200数据与自身不匹配,第一处理器100发出数据有误的置高信号,即“AB=1”,如数据无误,则发出置低信号,即“AB=0”。

定义第一处理器100对第三处理300数据判决的结果记为第一判决信号的第二路信号“AC”,当第一处理器100接收第三处理器300发来的数据进行校验,当判断第三处理器300数据与自身不匹配,第一处理器100发出数据有误的置高信号,即“AC=1”,如数据无误,则发出置低信号,即“AC=0”;“AB”与“AC”不能同时出现两个高信号。

定义第二处理器200对第一处理100数据判决的结果记为第二判决信号的第一路信号“BA”,当第二处理器200接收第一处理器100发来的数据进行校验,当判断第一处理器100数据与自身不匹配,第二处理器200发出数据有误的置高信号,即“BA=1”,如数据无误,则发出置低信号,即“BA=0”。

定义第二处理器200对第三处理300数据判决的结果记为第二判决信号的第二路信号“BC”,当第二处理器200接收第三处理器300发来的数据进行校验,当判断第三处理器300数据与自身不匹配,第二处理器200发出数据有误的置高信号,即“BC=1”,如数据无误,则发出置低信号,即“BC=0”;“BA”与“BC”不能同时出现两个高信号。

定义第三处理器300对第一处理100数据判决的结果记为第三判决信号的第一路信号“CA”,当第三处理器300接收第一处理器100发来的数据进行校验,当判断第一处理器100数据与自身不匹配,第三处理器300发出数据有误的置高信号,即“CA=1”,如数据无误,则发出置低信号,即“CA=0”。

定义第三处理器300对第二处理200数据判决的结果记为第三判决信号的第二路信号“CB”,当第三处理器300接收第二处理器200发来的数据进行校验,当判断第二处理器200数据与自身不匹配,第三处理器300发出数据有误的置高信号,即“CB=1”,如数据无误,则发出置低信号,即“CB=0”;“CA”与“CB”不能同时出现两个高信号。

判决逻辑子电路(410/420/430)两路输出信号分别为第一仲裁信号和第二仲裁信号:

向第一输出权三取二输出子电路440输出的第一仲裁信号记为信号“A”,当表示应给第一处理器100赋权时,第一仲裁信号的电路信号置高,即“A=1”,否则“A=0”;向第二输出权三取二输出子电路450输出的第二仲裁信号记为信号“B”,当表示应给第二处理器200赋权时,第二仲裁信号的电路信号置高,即“B=1”,否则“B=0”;“A”与“B”两个信号只能有一个为高信号且不能同时为低信号。

根据以上约束,三模输出权仲裁电路400八输入两输出信号可满足如下表1的真值表,表1中X表示任意值,1表示故障,0表示无故障。

表1三个判决逻辑子电路(410/420/430)的输入输出逻辑真值表

最终,通过第一输出权三取二输出子电路440和第二输出权三取二输出子电路450对第一判决逻辑子电路410、第二判决逻辑子电路420和第三判决逻辑子电路430输出的两路仲裁信号“A”与“B”进行三取二输出,就可向第一处理器100、第二处理器200输出有效的赋权信号,保证电路的可靠性。

第一输出权三取二输出子电路440输出的信号为第一赋权信号,记为信号“Q1”,“Q1=1”信号置高表示第一处理器被赋权,否则,“Q1=0”信号置低;第二输出权三取二输出子电路450输出的信号为第二赋权信号,记为信号“Q2”,“Q2=1”信号置高表示第二处理器被赋权,否则,“Q1=0”信号置低。

在一些实现方式中,三模故障屏蔽电路500可被配置为:基于接收到第二判决信号和第三判决信号均表征第一处理器100故障的次数,向第一处理器100输出故障复位信号;基于接收到第一判决信号和第三判决信号均表征第二处理器200故障的次数,向第二处理器200输出所述故障复位信号;基于接收到第一判决信号和第二判决信号均表征第三处理器300故障的次数,向第三处理器300输出所述故障复位信号。故障复位信号可为持续输出给处理器的复位端口,使得接收到复位信号的处理器一直复位,不再工作,从而达到屏蔽该故障处理器的目的。可以理解的,通过该种计数的方式可在处理器发生反复故障时,对反复故障的处理器进行屏蔽,避免输出权无意义的切换,提高了系统整体稳定性。该种屏蔽方式相对于传统的屏蔽方式而言,具备电路简易、策略简单的特点,保证了系统的可靠性。

进一步的,请参阅图4,三模故障屏蔽电路500可包括第一计数子电路510、第二计数子电路520和第三计数子电路530;第一处理器100与第二计数子电路520及第三计数子电路530连接,第二处理器200与第一计数子电路510及第三计数子电路530连接,第三处理器300与第一计数子电路510及第二计数子电路520连接;第一计数子电路510与第一处理器100的复位端连接,第二计数子电路520与第二处理器200的复位端连接,第三计数子电路530与第三处理器300的复位端连接。

其中,第一计数子电路510被配置为:在确定第二判决信号和第三判决信号均表征第一处理器100故障时,计数一次;计数次数大于预设的第一计数次数时,向第一处理器100输出故障复位信号;第二计数子电路520被配置为:在确定第一判决信号和第三判决信号均表征第二处理器200故障时,计数一次;计数次数大于预设第二计数次数时,向第二处理器200输出故障复位信号;第三计数子电路530被配置为:在确定第一判决信号和第二判决信号均表征第三处理器300故障时,计数一次;计数次数大于预设第三计数次数时,向第三处理器300输出故障复位信号。通过计数的方式可基于能够承受风险的程度灵活调整计数次数阈值,另外,还可将第一计数子电路、第二计数子电路和第三计数子电路的计数值均设置为相同的次数,也即第一计数次数、第二计数次数和第三计数次数相同;也可为不同的计数次数。

在一些实现方式中,第一计数子电路510包括第一与门子电路511、第一计数器512和第一锁存器513;第一与门子电路511与第一计数器512连接,第一计数器512与第一锁存器513连接。第一与门子电路511被配置为基于第二判决信号和第三判决信号,确定第一处理器100是否故障;第一计数器512被配置为在确定第一处理器100故障时计数一次;第一锁存器513被配置为在第一计数器512计数次数大于预设第一计数次数时,向第一处理器100输出故障复位信号。第二计数子电路520包括第二与门子电路521、第二计数器522和第二锁存器523;第二与门子电路521与第二计数器522连接,第二计数器522与第二锁存器523连接。第二与门子电路521被配置为基于第一判决信号和第三判决信号,确定第二处理器200是否故障;第二计数器522被配置为在确定第二处理器200故障时计数一次;第二锁存器523被配置为在第二计数器522计数次数大于预设第二计数次数时,向第二处理器200输出故障复位信号。第三计数子电路530包括第三与门子电路531、第三计数器532和第三锁存器533;第三与门子电路531与第三计数器532连接,第三计数器532与第三锁存器533连接。第三与门子电路531被配置为基于第一判决信号和第二判决信号,确定第三处理器300是否故障;第三计数器532被配置为在确定第三处理器300故障时计数一次;第三锁存器533被配置为在第三计数器532计数次数大于预设第三计数次数时,向第三处理器300输出故障复位信号。

通过上述实现方式可准确的对每个处理器的故障次数进行计算及故障屏蔽,保证系统运行的可靠性。

请参阅图5,在一些实现方式中,该箭载三模冗余计算机系统10还包括时钟同步电路102。第一处理器100、第二处理器200和第三处理器300的时钟同步端口均连接至时钟同步电路102。该时钟同步电路102被配置为:同步第一处理器100、第二处理器200和第三处理器300的时钟信号。也就是说,三个处理器之间通过每个处理器通过两路时钟信号线与其他处理器相连,从而形成两两相连,互相接收时钟同步信号。在初始情况下,可以首个具备输出权的处理器为主,例如以第一处理器100为主,以自身晶振为基准向第二处理器200和第三处理器300输出的同步时钟信号;第二处理器200和第三处理器300为从接收第一处理器100的同步时钟信号,并与之保持时钟对齐,输出时钟对齐反馈信号。当输出权转换时,以具有输出权的一模时钟为主,另两模转为从模式接收主模时钟同步信号。从而保证在三模的整个工作过程中时钟同步。

在本实施例中还提供一具体应用例,通过现有的硬件选择和设计可实现本实施例中的箭载三模冗余计算机系统10。具体如下:

处理器可选择采用ZYNQ-7045芯片平台,单芯片集成双核ARM Cortex-A9内核,800MHz主频(主频最高1.0GHz),并在芯片上集成了Xilinx的Kintex-7系列高性能FPGA(Field Programmable Gate Array,现场可编程逻辑门阵列)。既具备通用双核ARM处理器的编程方便性和较高的运算性能及一定的多核能力,同时具备FPGA在并行性、接口管理、高密度计算及数据处理等方面的优势,两者有机的结合起来。

每一模主控计算模块都配备大容量高速DDR3存储器缓存,容量可为1GB,保证复杂程序和操作系统对于内存的需求。同时配备大容量FLASH存储器,每个模的EMMC存储容量8GB,不但能满足箭机控制的数据存储需求,也可以用来实现箭上“黑匣子”或数据记录仪的功能。

DDR3存储器可采用Zynq PS端的主RAM存储器,容量和运行的稳定性对系统运行、数据处理及流程处理有重要影响。其中DDR3存储器选用Micron公司的MT41K256M16动态DDR3 DRAM芯片,2片并联,总位宽32bit,容量1GB。系统的大容量数据存储可采用1片Micron公司的MTFC8GAAAADV大容量EMMC闪存存储器实现。

输入电源进入计算机分为3路独立供电,对应给3个处理器及外围电路提供不同的电源,其中系统一次降压电源模块选用28V降到5V的方案,电源模块选择型号为HMTF28S5型电源模块,该电源模块具备抗浪涌能力,标称输入宽压14-40V,具有良好的输入输出保护能力。

每模需要1.0V、1.2V、1.5V、1.8V、3.3V、5V等多个电源轨道。可采用凌特的LTM4627、LTM4644电源uModule模块生成系统的1.0V、1.5V、1.8V、3.3V等主要电源轨道。再通过TPS51200生成DDR专用的电源轨道。通过LDO芯片TPS74901生成GTX收发器使用的1.0V和1.2V模拟电源。系统的主电源按照芯片手册要求的上电顺序进行上电。通过电源模块的PowerGood引脚和Run引脚进行控制。

Zynq的PS端需要33.333333MHz频率的晶振,用于系统倍频出系统主频、千兆以太网、DDR3接口等需要的时钟频率,同时系统定时器的时钟源也是由这个晶振生成的。晶振选用SiTime公司的SIT5156型温补晶振,稳定度优于5ppm。

通过ZYNQ PL端的高速GTX接口可实现多种高速串行接口,通过高速串行接口实现三模之间的机内高速总线数据通讯。晶振采用100MHz差分晶振。电路设计时需要控制传输线阻抗、控制过孔数量、连线保持等长。

三模故障屏蔽电路500可选用TI(Texas Instruments,德州仪器)公司的四路2输入正与门SN74ALVC08DR,集成了2个4位异步二进制计数器,计数器和锁存器均选用74HC/HCT393芯片,输出信号分别连接三个处理器的复位端口。

通过上述硬件实现即可完成本实施例中的箭载三模冗余计算机系统10的具体实现。

综上所述,本发明实施例中提供的一种箭载三模冗余计算机系统10,其中第一处理器100、第二处理器200和第三处理器300中每个处理器分别对另外两个处理器的数据进行校验,从而得到对应的第一判决信号、第二判决信号和第三判决信号;接着三模输出权仲裁电路400基于第一判决信号、第二判决信号和第三判决信号以及输出权控制信号,向第一处理器100或第二处理器200输出输出权控制信号;从而在第一处理器100和第二处理器200之间确定输出权,输出权就可在第一处理器100和第二处理器200之间进行变换,能够保证在任意一个处理器出现故障时,整个电路的输出可靠性;此时,第三处理器300仅仅作为校验判断的处理器,而不用于输出,可在降低设计复杂度及研制成本的同时保证具备高可靠冗余输出的能力;进一步的,三模故障屏蔽电路500基于第一判决信号、第二判决信号和第三判决信号,向第一处理器100、第二处理器200或第三处理器300输出强制故障复位信号,以停止故障处理器的工作,从而避免故障处理器影响整个系统的正常运行,保证系统运行的可靠。在此处所提供的说明书中,说明了大量具体细节。然而,能够理解,本发明的实施例可以在没有这些具体细节的情况下实践。在一些实例中,并未详细示出公知的方法、结构和技术,以便不模糊对本说明书的理解。

类似地,应当理解,为了精简本公开并帮助理解各个发明方面中的一个或多个,在上面对本发明的示例性实施例的描述中,本发明的各个特征有时被一起分组到单个实施例、图、或者对其的描述中。然而,并不应将该公开的方法解释成反映如下意图:即所要求保护的本发明要求比在每个权利要求中所明确记载的特征更多的特征。更确切地说,如下面的权利要求书所反映的那样,发明方面在于少于前面公开的单个实施例的所有特征。因此,遵循具体实施方式的权利要求书由此明确地并入该具体实施方式,其中每个权利要求本身都作为本发明的单独实施例。

本领域那些技术人员可以理解,可以对实施例中的装置中的模块进行自适应性地改变并且把它们设置在与该实施例不同的一个或多个装置中。可以把实施例中的模块或单元或组件组合成一个模块或单元或组件,以及此外可以把它们分成多个子模块或子单元或子组件。除了这样的特征和/或过程或者单元中的至少一些是相互排斥之外,可以采用任何组合对本说明书(包括伴随的权利要求、摘要和附图)中公开的所有特征以及如此公开的任何方法或者设备的所有过程或单元进行组合。除非另外明确陈述,本说明书(包括伴随的权利要求、摘要和附图)中公开的每个特征可以由提供相同、等同或相似目的的替代特征来代替。

此外,本领域的技术人员能够理解,尽管在此的一些实施例包括其它实施例中所包括的某些特征而不是其它特征,但是不同实施例的特征的组合意味着处于本发明的范围之内并且形成不同的实施例。例如,在下面的权利要求书中,所要求保护的实施例的任意之一都可以以任意的组合方式来使用。

应该注意的是上述实施例对本发明进行说明而不是对本发明进行限制,并且本领域技术人员在不脱离所附权利要求的范围的情况下可设计出替换实施例。在权利要求中,不应将位于括号之间的任何参考符号构造成对权利要求的限制。单词“包含”不排除存在未列在权利要求中的部件或步骤。位于部件之前的单词“一”或“一个”不排除存在多个这样的部件。本发明可以借助于包括有若干不同部件的硬件以及借助于适当编程的计算机来实现。在列举了若干装置的单元权利要求中,这些装置中的若干个可以是通过同一个硬件项来具体体现。单词第一、第二、以及第三等的使用不表示任何顺序。可将这些单词解释为名称。

- 一种箭载全三模冗余计算机体系架构

- 一种箭载全三模冗余计算机体系架构