可增层嵌埋内置元件的电路板结构及其制造方法

文献发布时间:2024-01-17 01:17:49

技术领域

本发明属于电路板结构及制造方法技术领域,尤其涉及可增层嵌埋内置元件的电路板结构及其制造方法。

背景技术

目前嵌埋元器件的PCB板,内埋元件类型包括存储芯片、功率芯片、逻辑芯片这样的主动元器件,也包括贴片式的电容、电阻和电感等被动元件。不同属性的内埋元器件厚度往往不一致,即便是相同属性的元器件,也会因为元件型号的差异导致厚度不一致。上述情况导致了完成图形转移后,内层芯板的厚度仍比最大的元件厚度大15-20um,因此也形成了以下缺点:

1.多数电路板都只有最厚的那款内埋元器件可以双面都通过盲孔连接电路板网络并扇出信号,其余的都只能单面导通和扇出,这对于产品的整体布线和网络设计是一种极大的浪费;

2.由于芯板厚度远大于较薄元件的厚度,在压合时,薄元件上方存在巨大空腔需要用流胶填满,若该空腔填胶不足则容易产生压合空洞的风险,同时由于太多的流胶用于填空腔,容易造成靠近空腔位置的介电层厚度严重偏薄以致无法达到客户的要求。

发明内容

本发明的目的在于至少解决现有技术中存在的技术问题之一,提供一种能够解决现有可增层嵌埋内置元件的电路板结构中只有单面可进行导通和扇出,造成产品生产设计的浪费,同时薄元件上方存在巨大空腔需要用流胶填满,容易产生压合空洞的风险,无法满足客户的生产要求等问题,具有能够通过盲孔双面连接PCB网络并扇出信号,使产品复杂的布线和网络设计得以利用,同时不同元器件所处空腔所需的填胶量差别不大,避免产生压合空洞的风险,满足客户的生产需要的可增层嵌埋内置元件的电路板结构。

本发明的目的在于至少解决现有技术中存在的技术问题之二,提供一种能够解决现有可增层嵌埋内置元件的电路板结构中只有单面可进行导通和扇出,造成产品生产设计的浪费,同时薄元件上方存在巨大空腔需要用流胶填满,容易产生压合空洞的风险,无法满足客户的生产要求等问题,具有能够通过盲孔双面连接PCB网络并扇出信号,使产品复杂的布线和网络设计得以利用,同时不同元器件所处空腔所需的填胶量差别不大,避免产生压合空洞的风险,满足客户的生产需要的可增层嵌埋内置元件的电路板结构的制作方法。

本发明的目的之一采用如下技术方案实现:

可增层嵌埋内置元件的电路板结构,包括:芯板层以及多个分别堆叠设置于所述芯板层上下表面上的增层结构,相邻所述增层结构之间的网络导通连接;

所述增层结构包括:

多个元器件,均通过导电胶分别粘附固定在所述芯板层的表面上并均与所述芯板层上的网络导通连接,各所述元器件的厚度偏差小于25um;

增层芯板,设置于所述芯板层的表面上,所述增层芯板对应各所述元器件开设有通孔且所述增层芯板的厚度与各所述元器件的厚度适配;

铜箔,堆叠设置于所述增层芯板上;

填胶层,填充设置于所述芯板层和增层芯板之间以及填充设置于所述增层芯板和铜箔之间。

进一步地,多个所述增层结构对称设置在所述芯板层上下表面上,距离所述芯板层相同距离上的所述元器件厚度偏差小于25um。

进一步地,距离所述芯板层不同距离上的所述元器件类型不同。

进一步地,所述导电胶为导电银浆或锡膏。

进一步地,所述元器件包括芯片、贴片式的电容、电阻和电感元件。

本发明的目的之二采用如下技术方案实现:

用于制造如权利要求1-5任一所述可增层嵌埋内置元件的电路板结构的制造方法,步骤如下:包括,

S1、准备好芯板层,对芯板层依次进行钻通孔、电镀填平通孔、贴膜、曝光、显影、蚀刻、褪膜等流程,完成芯板层的图形转移;

S2、选用多个厚度小于25um的元器件,将多个元器件贴装到芯板层上下表面上,并通过导电胶的连接导通各个元器件和芯板层之间的网络;

S3、对填胶层和增层芯板对对应各元器件进行开口设置,并朝着远离芯板层上下表面的方向分别按照填胶层、增层芯板、填胶层、铜箔依次堆叠设置,并进行高温压合,由此在芯板层的上下表面形成增层结构;

S4、对压合完成后的半成品依次进行钻盲孔、电镀填平盲孔、贴膜、曝光、显影、蚀刻、褪膜等流程,完成上述结构的图形转移。

进一步地,还包括S5:在完成步骤S4的产品上,可重复执行S2-S4的步骤,分别再在芯板层的上下表面堆叠增加多个增层结构。

进一步地,还包括S6:对完成S5的产品进行钻贯穿的埋孔,并在埋孔孔壁上镀铜,最后按照真空树脂塞孔、陶瓷磨板、电镀的流程顺序,完成埋孔塞孔。

进一步地,还包括S7:对完成S6的产品进行阻焊以及表面处理,最后铣切成形,完成产品制作。

相比现有技术,本发明的有益效果在于:

本发明的可增层嵌埋内置元件的电路板结构在使用时,可先将芯板层进行图形转移处理,之后再在芯板层的上下表面粘合固定上厚度偏差小于25um的多个元器件,之后在通过填胶层、增层芯板和铜箔依次堆叠压合固定,最后再次进行图形转移处理。本方案通过上述设置,所有元器件都可以通过盲孔双面连接PCB网络并扇出信号,使产品复杂的布线和网络设计得以利用;同时同一增层内埋入的元器件厚度差小于25um,使得不同元器件所处空腔所需的填胶量差别不大,消除了元器件上方填胶不足产生空洞以及元器件周边区域介电层厚度不足的风险,提高电路板结构的出品质量以及减少生产成本损失。本发明还提供用于制造上述电路板结构的制作方法,通过上述设置,使产品复杂的布线和网络设计得以利用,同时消除了元器件上方填胶不足产生空洞以及元器件周边区域介电层厚度不足的风险,提高电路板结构的出品质量以及减少生产成本损失。

附图说明

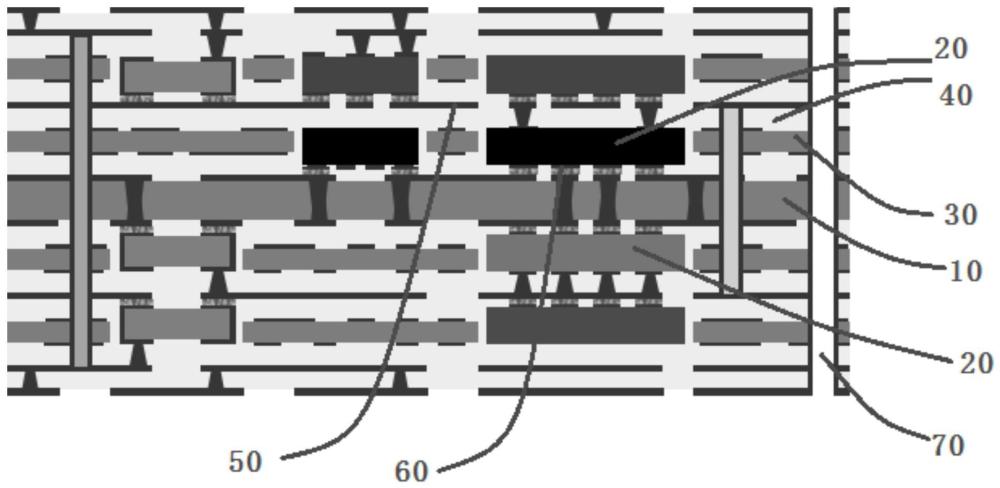

图1是本发明可增层嵌埋内置元件的电路板结构优选实施方式的结构示意图。

其中,图中各附图标记:

10、芯板层;20、元器件;30、增层芯板;40、填胶层;50、铜箔;60、导电胶;70、埋孔。

具体实施方式

下面,结合附图以及具体实施方式,对本发明做进一步描述,需要说明的是,在不相冲突的前提下,以下描述的各实施例之间或各技术特征之间可以任意组合形成新的实施例。

本发明参照图1所示,包括芯板层10以及多个分别堆叠设置于所述芯板层10上下表面上的增层结构,相邻所述增层结构之间的网络导通连接;所述增层结构包括:均通过导电胶60分别粘附固定在所述芯板层10的表面上并均与所述芯板层10上的网络导通连接的多个元器件20、设置于所述芯板层10的表面上的增层芯板30、堆叠设置于所述增层芯板30上的铜箔50以及填充设置于所述芯板层10和增层芯板30之间以及填充设置于所述增层芯板30和铜箔50之间的填胶层40,各所述元器件20的厚度偏差小于25um,所述增层芯板30对应各所述元器件20开设有通孔且所述增层芯板30的厚度与各所述元器件20的厚度适配。本方案在使用时,可先将芯板层10进行图形转移处理,之后再在芯板层10的上下表面粘合固定上厚度偏差小于25um的多个元器件20,之后在通过填胶层40、增层芯板30和铜箔50依次堆叠压合固定,最后再次进行图形转移处理。通过上述设置,所有元器件20都可以通过盲孔双面连接PCB网络并扇出信号,使产品复杂的布线和网络设计得以利用;同时同一增层内埋入的元器件20厚度差小于25um,使得不同元器件20所处空腔所需的填胶量差别不大,消除了元器件20上方填胶不足产生空洞以及元器件20周边区域介电层厚度不足的风险,提高电路板结构的出品质量以及减少生产成本损失。具体的,小于25um该数值的选取是为了适配激光钻盲孔、机械钻通孔进行计算考虑的。

作为本发明的优选实施例,其还可具有以下附加技术特征:

本实施例中,参照图1所示,多个所述增层结构对称设置在所述芯板层10上下表面上,距离所述芯板层10相同距离上的所述元器件20厚度偏差小于25um。具体的与芯板层10上下表面同样距离的增层结构上的多个元器件20均为同一类元件,由此确保其厚度偏差均在25um以内。通过上述设置,能够确保成型后的电路板结构上下基本对称,避免元件受结构不对称产生的应力影响而造成元件弯折甚至开裂的风险。提高了电路板结构的稳定性和使用寿命。

本实施例中,参照图1所示,距离所述芯板层10不同距离上的所述元器件20类型不同。通过上述设置,在保持成型后的电路板结构上下基本对称,结构稳定的同时,还能在芯板层10不同的增层结构内嵌埋不同类型的元器件20,增加埋入的元器件20种类和数量,也使得成型后的电路板结构具备更加复杂的电子电路性能和具有更多样的功能。

本实施例中,参照图1所示,所述导电胶60为导电银浆或锡膏。通过上述设置,该两种材料均能够实现将元器件20粘合固定在芯板层10上,同时该两种材料也具备电性导通的能力,由此使得通过该两者粘合固定的元器件20能与芯板层10上电路导通,实现元件Bottom面扇出信号。值得说明的,在导电胶60固化的流程中,两者采用不同的固化方式,如果导电胶60是导电银浆就用可编程烘箱烘烤固化,如果胶水是锡膏就过无铅回流焊线固化。

本实施例中,所述元器件20包括芯片、贴片式的电容、电阻和电感元件。通过上述设置,上述多种元器件20均能够安装在本芯板层10和增层结构中,由此使得成型后的电路板结构具备更加复杂的电子电路性能和具有更多样的功能。

本发明还提供一种用于制造如上所述可增层嵌埋内置元件的电路板结构的方法,步骤如下:包括,

S1、准备好芯板层10,对芯板层10打X形激光钻通孔,之后再电镀填平X形激光钻通孔,最后芯板层10依次进行贴膜、曝光、显影、蚀刻、褪膜等流程,完成芯板层10的图形转移;

S2、选用多个厚度小于25um的元器件20,将多个元器件20贴装到芯板层10上下表面上,并通过导电胶60的连接导通各个元器件20和芯板层10之间的网络;

S3、对填胶层40和增层芯板30对对应各元器件20进行开口设置,并朝着远离芯板层10上下表面的方向分别按照填胶层40、增层芯板30、填胶层40、铜箔50的次序依次从下到上排板,并进压机进行高温压合,由此在芯板层10的上下表面形成增层结构;其中填胶层40通常采用半固化片,其在高温压合的过程中会发生融化并填充到不同元器件20和增层芯板30之间的空腔中;

S4、在上述的半成品上做激光钻预处理并加工激光钻盲孔,然后加工第一机械钻埋孔70,之后再进行电镀,将激光钻盲孔填平,并在埋孔70孔壁上镀铜,通过该种方式将各个增层结构中的增层芯板30、多个元器件20以及芯板层10中电路和电信号进行连接导通;

S5、再将进行S4后的半成品,按照真空树脂塞孔→陶瓷磨板→电镀的流程顺序,完成埋孔70塞孔;

S6、对S5完成后的半成品依次进行贴膜、曝光、显影、蚀刻、褪膜等流程,完成增层结构的图形转移。

S7、工作人员还可根据用户需要,再在S6完成后的产品,再重复执行S2-S6的步骤,在产品的上下表面堆叠增加多个增层结构;

S8、对完成上述步骤的产品进行阻焊以及表面处理,最后铣切成形,完成产品制作。

通过上述设置,相比于传统的产品结构和加工方法,新的产品结构和加工方法拥有以下优势:

一、所有元器件20都可以通过盲孔双面连接PCB网络并扇出信号,使产品复杂的布线和网络设计得以利用。

二、同一增层结构内埋入的元器件20厚度差仅25um,由此使得不同元器件20所处空腔所需的填胶量差别不大,消除元器件20上方填胶不足,产生空洞或者元器件20周边区域介电层厚度不足的风险。

三、通过该种方法成型的电路板结构,其整体机构和各元器件20的厚度尺寸和上下布局基本对称,不存在元件受结构不对称产生的应力影响,也消除了电路板结构弯折甚至开裂的风险。

四、任意增层均可嵌埋元器件20,可埋入的元器件20数量翻倍增加,使得电路板结构具有更加复杂的电子电路性能。

五、实现了芯片在PCB板中的堆叠封装(Package on Package),封装密度高,传输路径短。

在不出现冲突的前提下,本领域技术人员可以将上述附加技术特征自由组合以及叠加使用。

上述实施方式仅为本发明的优选实施方式,不能以此来限定本发明保护的范围,本领域的技术人员在本发明的基础上所做的任何非实质性的变化及替换均属于本发明所要求保护的范围。

- 聚酰亚胺树脂、聚酰亚胺树脂组合物、使用其的触摸面板及其制造方法、滤色片及其制造方法、液晶元件及其制造方法、有机EL元件及其制造方法

- 一种用于增材制造中悬垂特征结构的分层方法及其增材制造方法

- 用于印刷电路板中的增层材及其制法、可内埋元件的印刷电路板

- 内置元件电路板、内置元件电路板的制造方法