用于通过PECVD进行Si间隙填充的方法

文献发布时间:2023-06-19 09:47:53

背景技术

领域

本公开的实施例涉及在基板上形成间隙填充材料的方法。

相关技术说明

在半导体处理中,正在制造具有持续地减小的特征尺寸的器件。通常,用于在这些先进技术节点处制造器件的特征包括高深宽比结构,并且通常需要用间隙填充材料(诸如绝缘材料)填充在高深宽比结构之间的间隙。将绝缘材料用于间隙填充应用的示例包括浅槽隔离(STI)、金属间电介质层(ILD)、金属前电介质(PMD)、钝化层、图案化应用等。随着器件几何形状缩小和热预算减少,由于现有沉积工艺的限制,高深宽比空间的无空隙填充变得越来越困难。

间隙填充材料可通过各种沉积工艺(例如,可流动式化学气相沉积(FCVD))来沉积。通过FCVD沉积的间隙填充材料通常质量差,其特征为高湿法蚀刻速率比(WERR)和高应力,并且需要后续工艺(诸如固化和/或退火),以提高间隙填充材料的质量。

因此,需要用于形成间隙填充材料的改进的工艺。

发明内容

本公开的实施例涉及在基板上形成间隙填充材料的方法。在一个实施例中,方法包括:将设置在工艺腔室中的基板加热到在约150摄氏度至约650摄氏度的范围内的温度;使含硅烷的前驱物流动到所述工艺腔室中;以及在所述基板中形成的特征的底部上沉积第一非晶硅层,并在所述基板的表面上沉积第二非晶硅层。所述特征的每个侧壁的第一部分与所述第一非晶硅层接触,并且每个侧壁的第二部分是暴露的。所述方法进一步包括去除所述第二非晶硅层。

在另一个实施例中,方法包括:将设置在工艺腔室中的基板加热到在约200摄氏度至约550摄氏度的范围内的温度;使硅烷或乙硅烷流动到所述工艺腔室中;在所述工艺腔室中形成等离子体;以及在所述基板中形成的特征的底部上沉积第一非晶硅层,并在所述基板的表面上沉积第二非晶硅层。所述特征的每个侧壁的第一部分与所述第一非晶硅层接触,并且每个侧壁的第二部分是暴露的。

在另一个实施例中,方法包括在基板中形成的特征的底部上沉积第一非晶硅层,并在所述基板的表面上沉积第二非晶硅层。所述特征的每个侧壁的第一部分与所述第一非晶硅层接触,并且每个侧壁的第二部分是暴露的。所述沉积所述第一非晶硅层和所述第二非晶硅层包括将设置在工艺腔室中的所述基板加热到在约150摄氏度至约650摄氏度的范围内的温度;以及使含硅烷的前驱物流动到所述工艺腔室中。所述方法进一步包括去除所述第二非晶硅层;以及重复所述沉积所述第一非晶硅层与所述第二非晶硅层和去除所述第二非晶硅层,直到所述特征被非晶硅填充为止。

附图说明

为了能够详细地理解本公开的上述特征的方式,可通过参考实施例来对上文简要地概述的本公开进行更具体的描述,其中一些在附图中被示出。然而,应注意,附图仅示出了本公开的典型的实施例,并且因此不应视为限定其范围,因为本公开可允许其他等效的实施例。

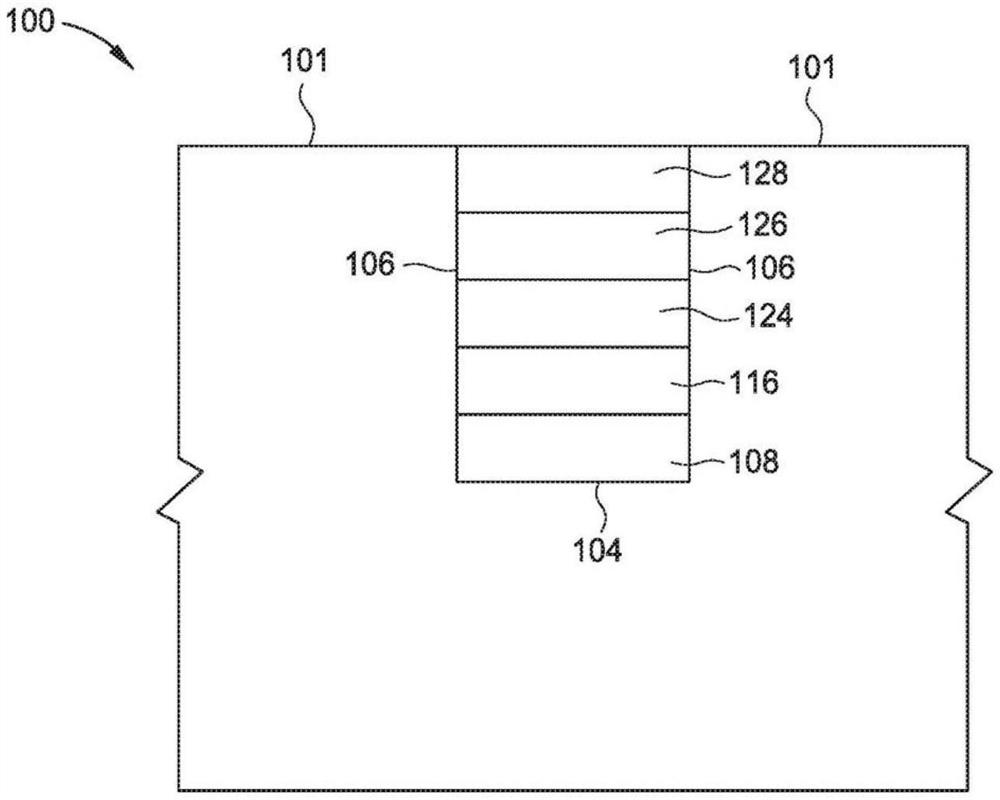

图1A至图1F示意性地示出了根据本文中所述的一个实施例的用于在基板上形成间隙填充材料的工艺。

为了便于理解,在可能的情况下,已经使用相同的附图标记来指示附图共有的相同元件。设想的是,一个实施例中公开的元素可有益地用于其他实施例,而无需关于其的具体叙述。

具体实施方式

本公开的实施例涉及用于填充沟槽的工艺。所述工艺包括在层的表面上沉积第一非晶硅层,并在所述层中形成的沟槽的一部分中沉积第二非晶硅层,并且所述沟槽的侧壁的部分是暴露的。去除所述第一非晶硅层。所述工艺进一步包括在所述层的所述表面上沉积第三非晶硅层,并在所述第二非晶硅层上沉积第四非晶硅层。去除所述第三非晶硅层。可重复沉积/去除循环工艺,直到所述沟槽被非晶硅层填充为止。由于所述非晶硅层是自下而上形成的,因此所述非晶硅层在所述沟槽中形成无缝非晶硅间隙填充。

如本文所使用的“基板”是指任何基板或在制造工艺期间在其上执行膜处理的基板上形成的材料表面。例如,取决于应用,其上可执行处理的基板表面包括诸如硅、氧化硅、应变硅、绝缘体上硅(SOI)、碳掺杂的氧化硅、非晶硅、掺杂的硅、锗、砷化镓、玻璃、蓝宝石和任何其他材料(诸如金属、金属氮化物、金属合金和其他导电材料)的材料。基板包括但不限于半导体晶片。基板可被暴露于预处理工艺以对基板表面进行抛光、蚀刻、还原、氧化、羟化、退火和/或烘烤。除了直接地在基板的表面上进行的膜处理之外,所公开的膜处理步骤中的任一个还可如下文更详细地公开的在基板上形成的在下面的层(under-layer)上执行,并且术语“基板表面”旨在包括如上下文所指示的此类在下面的层。因此,例如,在膜/层或部分膜/层已经被沉积到基板表面上时,新沉积的膜/层的暴露表面变成基板表面。

图1A至图1F示意性地示出了根据本文中所述的一个实施例的用于在基板上形成间隙填充材料的工艺。如图1A所示,基板100包括特征102。出于说明目的,附图示出了具有单个特征的基板;然而,本领域的技术人员将理解,可存在多于一个特征。特征102的形状可为任何合适的形状,包括但不限于沟槽和圆柱形过孔。如就这一点所使用的,术语“特征”意指任何有意的表面不规则性。特征的合适示例包括但不限于具有底部和两个侧壁的沟槽和过孔。特征可具有任何合适的深宽比(特征的深度与特征的宽度的比值)。在一些实施例中,所述深宽比大于或等于约5:1、10:1、15:1、20:1、25:1、30:1、35:1或40:1。

基板100包括表面101,并且特征102是表面101中形成的开口。在一个实施例中,基板100包括由诸如氧化硅或氮化硅之类的介电材料制成的STI区域,并且特征102形成在STI区域中。特征102包括底部104和侧壁106。接下来,如图1B所示,在特征102的底部104上沉积第一非晶硅层108,并且在基板100的表面101上沉积第二非晶硅层110。通过等离子体增强化学气相沉积(PECVD)工艺沉积第一非晶硅层108和第二非晶硅层110。

在一个实施例中,用于沉积第一非晶硅层108和第二非晶硅层110的PECVD工艺包括使含硅的前驱物流动到工艺腔室中,并且在工艺腔室中形成等离子体。在一个实施例中,工艺腔室是可从加利福尼亚州圣克拉拉市的应用材料公司(Applied Materials Inc.)获得的

与通过原子层沉积(ALD)工艺形成的共形层不同,所述共形层在沉积期间大部分或完全地覆盖侧壁106,第一非晶硅层108形成在特征102的底部104上并与每个侧壁106的第一部分112接触。每个侧壁106的第二部分114是暴露的,并且未被第一非晶硅层108覆盖。类似地,与第一非晶硅层108同时地形成的第二非晶硅层110形成在表面101上,而不形成在特征102的每个侧壁106的第二部分114上。第一非晶硅层108和第二非晶硅层110分别形成在底部104和表面101上,并且底部104基本上平行于表面101。因此,第一非晶硅层108和第二非晶硅层110形成在基本上平行的表面上,并且具有大致相同的厚度或近似相同的厚度。换句话说,第一非晶硅层108和第二非晶硅层110形成在水平表面上,而不形成在竖直表面上。侧壁106(竖直表面)唯一被覆盖的部分是与设置在底部104上的第一非晶硅层108的厚度相对应的部分。

接下来,如图1C所示,将第二非晶硅层110从表面101去除。去除工艺可为在与其中形成第一非晶硅层108和第二非晶硅层110的工艺腔室相同的工艺腔室中执行的等离子体蚀刻工艺。等离子体蚀刻工艺的腔室压力可与在PECVD工艺期间的腔室压力相同或与在PECVD工艺期间的腔室压力不同。处理温度可为与沉积第一非晶硅层108和第二非晶硅层110的PECVD工艺相同的处理温度。在沉积和蚀刻工艺中利用相同的处理温度有助于在沉积工艺与蚀刻工艺之间快速地转变,这增加了基板产量。等离子体功率密度在约0.14W/cm

在去除第二非晶硅层110之后,执行第二PECVD工艺以在第一非晶硅层108上形成第三非晶硅层116并在表面101上形成第四非晶硅层118,如图1D所示。可在与用于形成第一非晶硅层108和第二非晶硅层110的PECVD工艺相同的工艺条件下执行第二PECVD工艺。第三非晶硅层116与每个侧壁106的部分120接触,并且每个侧壁106的部分122是暴露的。第三非晶硅层116和第四非晶硅层118分别具有与第一非晶硅层108和第二非晶硅层110相同的性质。

如图1E所示,将第四非晶硅层118从表面101去除。去除工艺可与用于去除第二非晶硅层110的去除工艺相同。在一个实施例中,特征102被第一非晶硅层108和第三非晶硅层116填充。换句话说,整个底部104与第一非晶硅层108接触,并且整个侧壁106与第一非晶硅层108和第三非晶硅层116接触。在其他实施例中,可执行附加的沉积/去除循环工艺以填充特征102。在一个实施例中,如图1F所示,附加的非晶硅层124、126、128被沉积在第三非晶硅层116上,并且由于在每个沉积工艺后跟去除工艺,没有非晶硅层残留在表面101上。因为用于去除工艺的等离子体的功率低,所以使到特征102中的离子轰击最小化。此外,在沉积/去除循环的最后一个沉积工艺处,特征102被过度填充,并且最后一个去除工艺去除在表面101上和在特征102上方的非晶硅层。对于每个沉积/去除循环(一个循环包括一个沉积工艺和一个去除工艺),沉积时间与蚀刻时间的比值可在约1比3至约1比15的范围内。在此类示例中,蚀刻时间实质上长于沉积时间。循环数取决于特征102的深度和/或沉积在特征102中的每个非晶硅层的厚度。在一个实施例中,沉积/去除循环数在约50至约200的范围内,并且在相应沉积循环期间形成的每个非晶硅层的厚度在约250埃至约1000埃之间。特征102中形成的多个非晶硅层108、116、124、126、128是自下而上形成的。因此,在非晶硅层108、116、124、126、128中没有形成接缝或空隙。

通过使用沉积/去除循环工艺,可自下而上无缝地填充特征(诸如沟槽)。此外,由于特征中形成的非晶硅层是不可流动的,因此与常规可流动式非晶硅间隙填充相比,提高了非晶硅层的质量。此外,在形成可流动式非晶硅间隙填充之后通常执行的后续固化和/或退火工艺并非必需。

尽管前述内容针对的是本公开的实施例,但在不脱离本公开的基本范围的情况下,可设想其他和进一步实施例,并且实施例的范围由所附权利要求书确定。

- 用于通过PECVD进行Si间隙填充的方法

- 用于通过毛细管流动在电子封装体中或之间进行间隙涂覆和/或填充的组合物及其使用方法