一种1T相CrTe

文献发布时间:2024-01-17 01:26:37

技术领域

本发明涉及二维材料制备技术领域,尤其涉及一种1T相CrTe

背景技术

2004年Andre Geim等人利用胶带对厚块石墨进行机械剥离,成功得到单层石墨烯,自此二维材料迎来高速发展。2017年,二维CrI

目前对于二维CrTe

二维材料的大面积、低温制备是实现二维材料产业化应用的基础。然而机械剥离技术难以获得晶圆级规模的二维材料,该方法仅适合于实验室层面的基础科学研究。使用一般的化学气相沉积法制备1T-CrTe

发明内容

1.要解决的技术问题

本发明的目的是为了解决现有技术中使用一般的化学气相沉积法制备1T-CrTe

2.技术方案

为了实现上述目的,本发明采用了如下技术方案:

一种1T相CrTe

步骤1:采用含Cr的均匀连续薄膜作为固态的第一前驱体,其中采用Cr、Cr

步骤2:处理碲源使其形成气态的第二前驱体,其中采用碲粉作为碲源;

步骤3:在还原性气氛下,将气态的第二前驱体传质到带有第一前驱体的基底上进行化学反应,形成二维1T相CrTe

步骤4:所述化学反应在等离子体辅助下进行,等离子体功率为50-500W。

优选地,所述步骤1中含Cr的薄膜通过蒸发镀膜或磁控溅射镀膜制备。

优选地,所述步骤1中含Cr薄膜的厚度不超过15nm,Cr薄膜的厚度决定合成CrTe2薄膜的厚度。

优选地,所述步骤2中形成气态第二前驱体的方法采用加热或能量粒子束处理。

优选地,所述步骤4中化学反应进行时,基底采用两段升温及两段恒温处理,第一段恒温的温度为80-120℃,第二段恒温的温度为330-450℃。

优选地,所述步骤4中基底选自绝缘材料、半导体材料或二维层状材料。

优选地,所述绝缘材料和半导体材料为SiO

3.有益效果

相比于现有技术,本发明的优点在于:

本发明中,使用含Cr的大面积薄膜作为铬源,使用等离子体增强化学气相沉积技术,实现了低温制备晶圆级1T相CrTe

本发明的技术方法也适用于低温制备1T相的CrS

附图说明

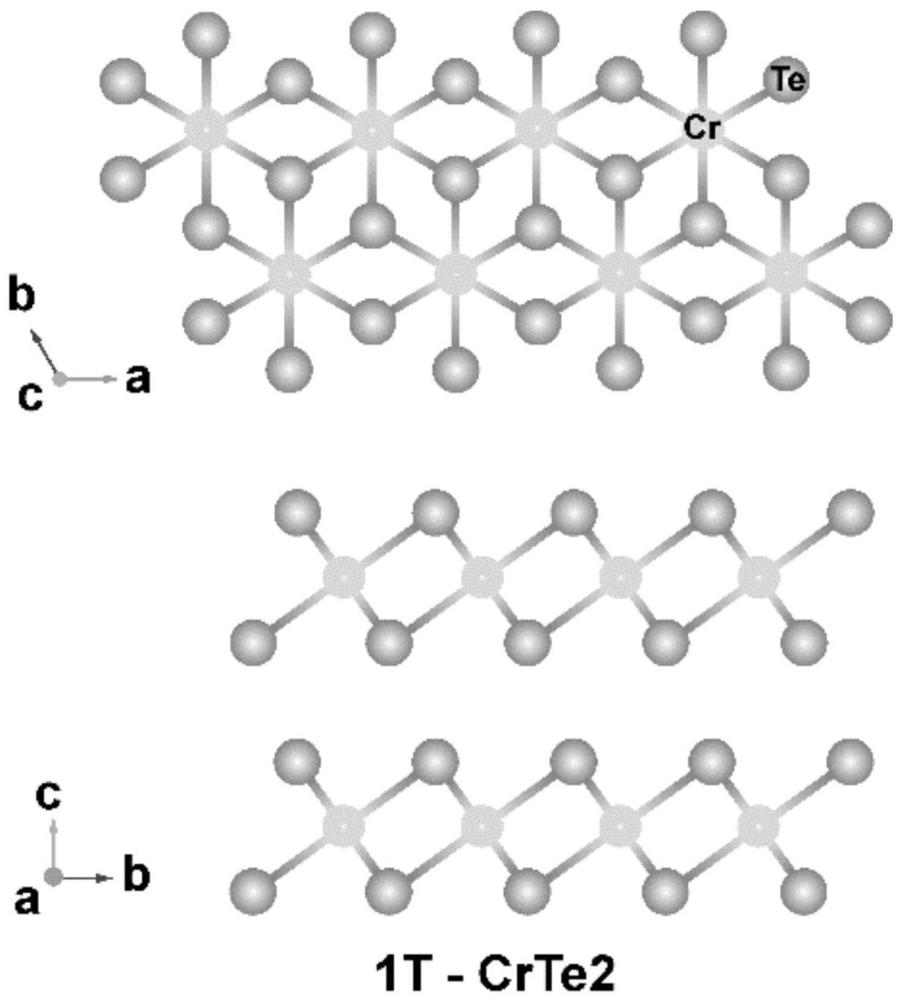

图1为本发明中提出的二维层状1T-CrTe

图2为本发明中提出的二维层状1T-CrTe

图3为实施例2制备的2英寸二维1T-CrTe

图4为实施例2制备的2英寸二维1T-CrTe

图5为实施例2制备的2英寸二维1T-CrTe

图6为实施例2制备的2英寸二维1T-CrTe

图7为实施例2制备的2英寸二维1T-CrTe

图8为实施例3制备的二维1T-CrTe

图9为实施例4制备的二维1T-CrTe

图10为实施例5制备的二维1T-CrTe

图11为实施例6制备的WSe

图12为实施例6制备的WSe

图13为实施例7制备的二维1T-CrTe

图14为对比例1制备的二维1T-CrTe

图15为对比例2制备的产物的拉曼图谱。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

实施例1:

一种1T相CrTe

步骤1:采用含Cr的均匀连续薄膜作为固态的第一前驱体,其中采用Cr或Cr

步骤2:处理碲源使其形成气态的第二前驱体,其中采用碲粉作为碲源;

步骤3:在还原性气氛下,将气态的第二前驱体传质到带有第一前驱体的基底上进行化学反应,形成二维CrTe

化学反应进行时,基底采用两段升温及两段恒温处理,第一段恒温的温度为80-120℃,第二段恒温的温度为300-450℃,基底选自绝缘材料、半导体材料或二维层状材料;绝缘材料和半导体材料为SiO

步骤4:化学反应在等离子体辅助下进行,等离子体功率为50-500W。

本发明中,使用含Cr的大面积薄膜作为铬源,使用等离子体增强化学气相沉积技术,实现了低温制备晶圆级1T相CrTe

实施例2:

其具有上述实施例的实施内容,其中,对于上述实施例的具体实施方式可参阅上述描述,此处的实施例不作重复详述;而在本申请实施例中,其与上述实施例的区别在于:

本实施例中,首先将2英寸SiO

通入H

待反应结束,让PECVD系统快速降至室温而得到二维CrTe

实施例3:

其具有上述实施例的实施内容,其中,对于上述实施例的具体实施方式可参阅上述描述,此处的实施例不作重复详述;而在本申请实施例中,其与上述实施例的区别在于:

本实施例中,首先将SiO

通入H

待反应结束,让PECVD系统快速降至室温而得到二维CrTe

实施例4:

其具有上述实施例的实施内容,其中,对于上述实施例的具体实施方式可参阅上述描述,此处的实施例不作重复详述;而在本申请实施例中,其与上述实施例的区别在于:

本实施例中,首先将2英寸SiO

本实施例中,通入H

本实施例中,待反应结束,让PECVD系统快速降至室温而得到二维CrTe

实施例5:

其具有上述实施例的实施内容,其中,对于上述实施例的具体实施方式可参阅上述描述,此处的实施例不作重复详述;而在本申请实施例中,其与上述实施例的区别在于:

本实施例中,首先将2英寸SiO

本实施例中,通入H

本实施例中,待反应结束,让PECVD系统快速降至室温而得到二维CrTe

实施例6:

其具有上述实施例的实施内容,其中,对于上述实施例的具体实施方式可参阅上述描述,此处的实施例不作重复详述;而在本申请实施例中,其与上述实施例的区别在于:

本实施例中,使用尺寸为15mm×15mm且覆盖有单层的二维WSe

本实施例中,通入H

待反应结束,让PECVD系统快速降至室温而得到二维1T-CrTe

实施例7:

其具有上述实施例的实施内容,其中,对于上述实施例的具体实施方式可参阅上述描述,此处的实施例不作重复详述;而在本申请实施例中,其与上述实施例的区别在于:

本实施例中,使用尺寸为15mm×15mm的单晶硅片作为半导体基底。使用磁控溅射系统以0.2nm/s的速率在上述基底上沉积4nm厚的Cr薄膜作为铬源,送入PECVD系统并置于载气下游端(图2)。称取碲粉800mg装入石英舟,送入PECVD系统并置于载气上游端。使用机械泵抽真空,使系统的本底真空低于1.0×10

本实施例中,通入H

待反应结束,让PECVD系统快速降至室温而得到二维1T-CrTe

以上实施例说明:改变相应的实验参数比如Cr膜的原材料前驱体及其厚度、基底的种类、等离子体的功率、合成温度等均能获得1T相CrTe

对比例1:

本实施例中,对比例1相较于实施例1,在反应时未引入等离子体辅助。首先将2英寸SiO

本实施例中,通入H

本实施例中,待反应结束,让PECVD系统快速降至室温而得到产物。对得到的产物进行拉曼光谱表征,如图14所示,结果表明对比例1所使用的方法无法在低温下制备CrTe

对比例2:

本实施例中,对比2相较于实施例1,反应温度高且在反应时未引入等离子体辅助。首先将2英寸SiO

本实施例中,通入H

本实施例中,待反应结束,让PECVD系统快速降至室温而得到产物。对得到的产物进行拉曼光谱表征,如图15所示,结果表明对比例2尽管提高了反应温度,但在无等离子体辅助的条件下,无法制备CrTe

以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,根据本发明的技术方案及其发明构思加以等同替换或改变,都应涵盖在本发明的保护范围之内。