正交相位检测器及相关电路

文献发布时间:2023-06-19 19:18:24

技术领域

本发明涉及检测同相时钟信号和正交时钟信号之间的相位差,更具体地涉及正交相位检测器及其相关电路。

背景技术

通常使用正交相位检测器(quadrature phase detector)来检测同相时钟信号和正交时钟信号之间的相位差,正交相位检测器的检测结果可以被时钟信号发生器或延迟元件用于调整同相时钟信号或正交时钟信号的相位。传统的正交相位检测器通常使用有源器件(如异或门XOR)来实现,然而,使用异或门可能会增加功耗。另外,如果正交相位检测器被设计为用于检测相位为0度、90度、180度和270度的四个时钟信号,则需要设计四组电路来检测0度和90度时钟信号之间的相位差、90度和180度时钟信号之间的相位差、180度和270度时钟信号之间的相位差、270度和0度时钟信号之间的相位差。但是,由于半导体工艺的原因,四组电路之间可能存在不匹配,导致相位检测不匹配或相位检测错误。

发明内容

因此,本发明的目的在于提供一种正交相位检测器及相关电路,其中大部分部件采用无源器件实现,以降低功耗并改善相位检测失配。

根据本发明的一个实施例,公开了一种包括第一检测电路的正交相位检测器。第一检测电路包括第一开关、第二开关和第一滤波器,其中第一开关受第二时钟信号控制以选择性地将第一时钟信号耦接到第一节点,第二开关受第二时钟信号控制以选择性地将第一节点耦接到参考电压,并且第一滤波器对第一节点处的电压进行滤波以产生第一检测结果。

根据本发明的一个实施例,公开了一种包括时钟信号发生器、第一检测电路和控制电路的正交相位检测电路。时钟信号发生器被配置为产生第一时钟信号和第二时钟信号。第一检测电路包括第一开关、第二开关和第一滤波器,其中第一开关受第二时钟信号控制以选择性地将第一时钟信号耦接到第一节点,第二开关受第二时钟信号控制以选择性地将第一节点耦接到参考电压,并且第一滤波器被配置为对第一节点处的电压进行滤波以产生第一检测结果。控制电路用以根据第一检测结果产生控制信号以调整第一时钟信号或第二时钟信号的相位。

在阅读了在各种附图和附图中示出的优选实施例的以下详细描述之后,本发明的这些和其他目的对于本领域普通技术人员无疑将变得显而易见。

附图说明

本发明通过结合附图,阅读随后的详细描述和实施例可以更全面地理解,其中:

图1是例示根据本发明一个实施例的电路的示意图。

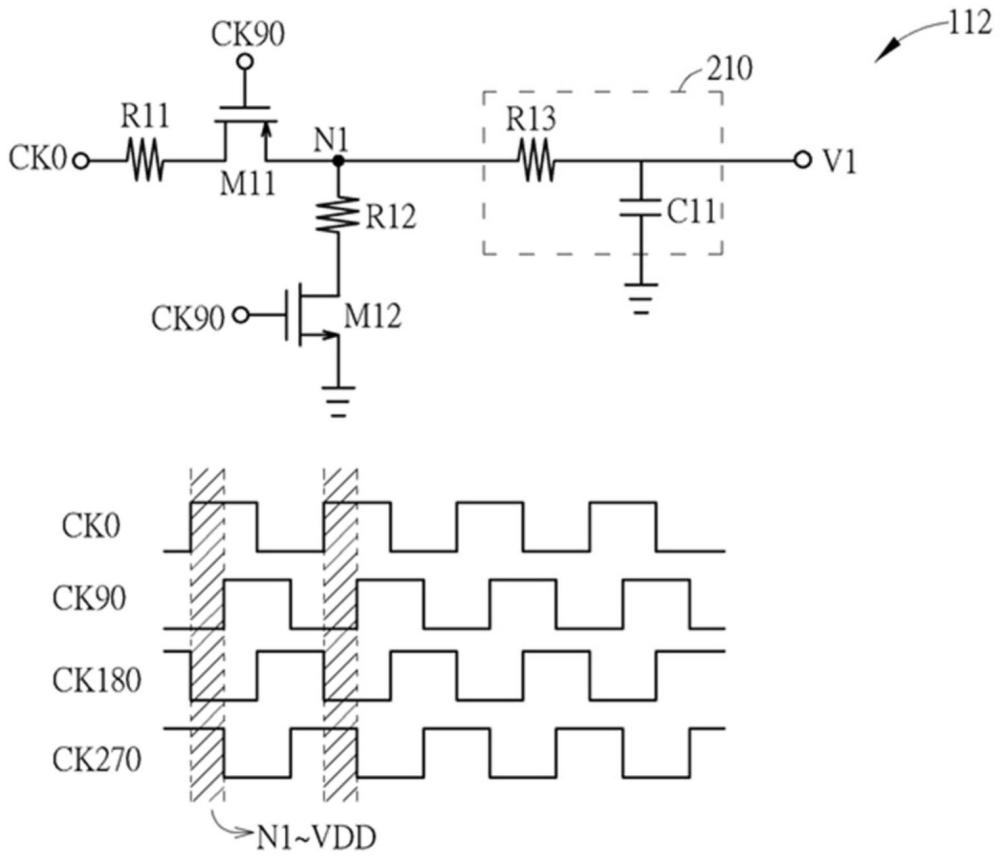

图2为例示根据本发明一个实施例的第一检测电路的示意图。

图3是例示根据本发明一个实施例的第二检测电路的示意图。

图4为例示根据本发明一个实施例的第三检测电路的示意图。

图5为例示根据本发明一个实施例的第四检测电路的示意图。

图6为例示根据本发明一个实施例的第一检测电路的示意图。

图7是例示根据本发明一个实施例的第二检测电路的示意图。

图8为例示根据本发明一个实施例的第三检测电路的示意图。

图9为例示根据本发明一个实施例的第四检测电路的示意图。

具体实施方式

在说明书及权利要求当中使用了某些词汇来指称特定的组件。本领域一般技术人员应可理解,电子设备制造商可以会用不同的名词来称呼同一组件。本说明书及权利要求并不以名称的差异来作为区别组件的方式,而是以组件在功能上的差异来作为区别的基准。在通篇说明书及后续的权利要求当中所提及的“包括”是开放式的用语,故应解释成“包括但不限定于”。此外,“耦接”一词在此是包含任何直接及间接的电气连接手段。因此,若文中描述第一装置电性连接于第二装置,则代表该第一装置可直接连接于该第二装置,或通过其他装置或连接手段间接地连接至该第二装置。

图1是例示根据本发明一个实施例的正交相位检测电路100的示意图。如图1所示,正交相位检测电路100包括正交相位检测器110、控制电路120和时钟信号发生器130,其中正交相位检测器110包括第一检测电路112、第二检测电路114、第三检测电路116和第四检测电路118。在本实施例中,正交相位检测电路100被配置为产生理想相位分别为0度、90度、180度和270度的四个时钟信号CK0、CK90、CK180和CK270。

在正交相位检测电路100的操作中,正交相位检测器110被配置为检测任意两个相邻时钟信号之间的相位差以产生检测结果。具体地,第一检测电路112用于检测时钟信号CK0和CK90之间的相位差以产生第一检测结果V1,第二检测电路114用于检测时钟信号CK90和CK180之间的相位差以产生第二检测结果V2,第三检测电路116用于检测时钟信号CK180和CK270之间的相位差以产生第三检测结果V3,第四检测电路118用于检测时钟信号CK270与CK0之间的相位差以产生第四检测结果V4。然后,控制电路120参考第一检测结果V1、第二检测结果V2、第三检测结果V3和第四检测结果V4,判断时钟信号CK0、CK90、CK180和CK270中的任何一个是否需要调整相位,并据此产生至少一个控制信号Vc。具体而言,控制电路120可以参考第一检测结果V1来判断时钟信号CK0与CK90之间的相位差是否不等于90度,并产生控制信号Vc至时钟信号发生器130以调整时钟信号CK90的相位。控制电路120可参考第二检测结果V2来判断时钟信号CK90与CK180之间的相位差是否不等于90度,并产生控制信号Vc至时钟信号发生器130以调整时钟信号CK180的相位。控制电路120可参考第三检测结果V3以判断时钟信号CK180与CK270之间的相位差是否不等于90度,并产生控制信号Vc至时钟信号发生器130以调整时钟信号CK270的相位。控制电路120可参考第四检测结果V4并判断时钟信号CK270与CK0之间的相位差是否不等于90度,并产生控制信号Vc至时钟信号发生器130以调整时钟信号CK0的相位。

在本实施例中,第一检测电路112、第二检测电路114以及第三检测电路116和第四检测电路118的至少一部分被设计为使得大部分组件采用无源元件来实现,以降低功耗并改善相位检测失配。

图2为例示本发明一个实施例的第一检测电路112的示意图。如图2所示,第一检测电路112包括晶体管M11和M12、电阻器R11和R12以及低通滤波器210,其中低通滤波器210包括电阻器R13和电容器C11。在本实施例中,晶体管M11为P型晶体管而晶体管M12为N型晶体管,晶体管M11的栅电极耦接时钟信号CK90,晶体管M11的第一电极通过节点N1和电阻器R12耦接至晶体管M12的第一电极,晶体管M11的第二电极通过电阻器R11耦接到时钟信号CK0,晶体管M12的第二电极耦接到地电压。

在另一实施例中,晶体管M11可以由任何不同类型的开关代替,并且该开关由时钟信号CK90控制以选择性地将时钟信号CK0连接到节点N1。此外,晶体管M12可以用任何不同类型的开关代替,该开关由时钟信号CK90控制,以选择性地将节点N1连接到地电压。

在第一检测电路112的操作中,当时钟信号CK90具有低电压(例如地电压或0V)并且时钟信号CK0具有高电压(例如时钟信号发生器130的电源电压VDD)时,节点N1将具有高电压(例如VDD);当时钟信号CK90和CK0均为低电压时,节点N1为低电压。而当时钟信号CK90为高电压时,则节点N1将一直为低电压,因为具有较大驱动能力的晶体管M12对节点N1进行放电。因此,由于节点N1仅在时钟信号CK0/CK90的四分之一周期期间具有高电压,因此如果时钟信号CK0和CK90之间的相位差正好等于90度,则对节点N1的电压进行滤波产生的第一检测结果V1应等于(1/4)*VDD。

在一个实施例中,如果第一检测结果Vl低于(1/4)*VDD,则表示时钟信号CK0和CK90之间的相位差小于90度,控制电路120可以产生控制信号Vc,以控制时钟信号发生器130延迟时钟信号CK90的相位。同样地,若第一检测结果V1大于(1/4)*VDD,则表示时钟信号CK0与CK90之间的相位差大于90度,控制电路120可产生控制信号Vc以控制时钟信号发生器130使时钟信号CK90的相位提前。

在图2所示的实施例中,第一检测电路112被配置为基于时钟信号CK0和CK90的上升沿检测相位差。在另一实施例中,晶体管M11可以由N型晶体管实现,而晶体管M12可以由P型晶体管实现,用于根据时钟信号CK0和CK90的下降沿检测相位差。

图3是例示根据本发明一个实施例的第二检测电路114的示意图。如图3所示,第二检测电路114包括晶体管M21和M22、电阻器R21和R22以及低通滤波器310,其中低通滤波器310包括电阻器R23和电容器C21。在本实施例中,晶体管M21为P型晶体管而晶体管M22为N型晶体管,晶体管M21的栅电极耦接时钟信号CK180,M21的第一电极通过节点N2和电阻器R22耦接至晶体管M22的第一电极,晶体管M21的第二电极通过电阻器R21耦接到时钟信号CK90,晶体管M22的第二电极耦接到地电压。

在另一实施例中,晶体管M21可以由任何不同类型的开关代替,并且该开关由时钟信号CK180控制以选择性地将时钟信号CK90连接到节点N2。此外,晶体管M22可以用任何不同类型的开关代替,该开关由时钟信号CK180控制,以选择性地将节点N2连接到地电压。

在第二检测电路114的操作中,当时钟信号CK180具有低电压(例如地电压或0V)并且时钟信号CK90具有高电压(例如时钟信号发生器130的电源电压VDD)时,节点N2将具有高电压(例如VDD);当时钟信号CK180和CK90均具有低电压时,节点N2将具有低电压。而当时钟信号CK180具有高电压时,节点N2将一直为低电压,因为具有较大驱动能力的晶体管M22对节点N2进行放电。因此,由于节点N2仅在时钟信号CK90/CK180的四分之一周期期间内具有高电压,因此如果时钟信号CK90和CK180之间的相位差正好等于90度,则对节点N2的电压进行滤波产生的第二检测结果V2应当等于(1/4)*VDD。

在一个实施例中,若第二检测结果V2低于(1/4)*VDD,则表示时钟信号CK90与CK180之间的相位差小于90度,控制电路120可产生控制信号Vc以控制时钟信号发生器130延迟时钟信号CK180的相位。类似地,若第二检测结果V2大于(1/4)*VDD,则表示时钟信号CK90与CK180之间的相位差大于90度,则控制电路120可产生控制信号Vc以控制时钟信号发生器130使时钟信号CK180的相位提前。

在图3所示的实施例中,第二检测电路114被配置为基于时钟信号CK90和CK180的上升沿检测相位差。在另一个实施例中,晶体管M21可以由N型晶体管实现,而晶体管M22则由P型晶体管实现,用于根据时钟信号CK90和CK180的下降沿检测相位差。

图4为例示根据本发明一个实施例的第三检测电路116的示意图。如图4所示,第三检测电路116包括晶体管M31和M32、电阻器R31和R32以及低通滤波器410,其中低通滤波器410包括电阻器R33和电容器C31。在本实施例中,晶体管M31为P型晶体管而晶体管M32为N型晶体管,晶体管M31的栅电极耦接时钟信号CK270,晶体管M31的第一电极通过节点N3和电阻器R32耦接至晶体管M32的第一电极,晶体管M31的第二电极通过电阻器R31耦接到时钟信号CK180,晶体管M32的第二电极耦接到地电压。

在另一实施例中,晶体管M31可以由任何不同类型的开关代替,并且该开关由时钟信号CK270控制以选择性地将时钟信号CK180连接到节点N3。此外,晶体管M32可以用任何不同类型的开关代替,该开关由时钟信号CK270控制,以选择性地将节点N3连接到地电压。

在第三检测电路116的操作中,当时钟信号CK270具有低电压(例如地电压或0V)并且时钟信号CK180具有高电压(例如时钟信号发生器130的电源电压VDD)时,节点N3将具有高电压(例如VDD);当时钟信号CK270和CK180均具有低电压时,节点N3为低电压。而当时钟信号CK270为高电压时,节点N3将一直为低电压,因为具有较大驱动能力的晶体管M32对节点N3进行放电。因此,由于节点N3仅在时钟信号CK180/CK270的四分之一周期期间内具有高电压,因此如果时钟信号CK180和CK270之间的相位差正好等于90度,则对节点N3的电压进行滤波产生的第三检测结果V3应当等于(1/4)*VDD。

在一个实施例中,若第三检测结果V3低于(1/4)*VDD,则表示时钟信号CK180与CK270之间的相位差小于90度,控制电路120可产生控制信号Vc以控制时钟信号发生器130延迟时钟信号CK270的相位。类似地,若第三检测结果V3大于(1/4)*VDD,则表示时钟信号CK180与CK270之间的相位差大于90度,控制电路120可产生控制信号Vc,以控制时钟信号发生器130使时钟信号CK270的相位提前。

在图4所示的实施例中,第三检测电路116被配置为基于时钟信号CK180和CK270的上升沿检测相位差。在另一实施例中,晶体管M31可由N型晶体管实现,而晶体管M32则由P型晶体管实现,以根据时钟信号CK180和CK270的下降沿检测相位差。

图5为根据本发明一个实施例的第四检测电路118的示意图。如图5所示,第四检测电路118包括晶体管M41和M42、电阻器R41和R42以及低通滤波器510,其中低通滤波器510包括电阻器R43和电容器C41。在本实施例中,晶体管M41为P型晶体管而晶体管M42为N型晶体管,晶体管M41的栅电极耦接时钟信号CK0,晶体管M41的第一电极通过节点N4和电阻器R42耦接晶体管M42的第一电极,晶体管M41的第二电极通过电阻器R41耦接到时钟信号CK270,晶体管M42的第二电极耦接到地电压。

在另一实施例中,晶体管M41可以由任何不同类型的开关代替,并且该开关由时钟信号CK0控制以选择性地将时钟信号CK270连接到节点N4。此外,晶体管M42可以用任何不同类型的开关代替,该开关由时钟信号CK0控制,以选择性地将节点N4连接到地电压。

在第四检测电路118的操作中,当时钟信号CK0具有低电压(例如地电压或0V)并且时钟信号CK270具有高电压(例如时钟信号发生器130的电源电压VDD)时,节点N4将具有高电压(例如VDD);当时钟信号CK0和CK270均为低电压时,节点N4为低电压。而当时钟信号CK0为高电压时,节点N4将一直为低电压,因为具有较大驱动能力的晶体管M42对节点N4进行放电。因此,由于节点N4仅在时钟信号CK270/CK0的四分之一周期内具有高电压,因此如果时钟信号CK270和CK0之间的相位差正好等于90度,则对节点N4的电压进行滤波产生的第四检测结果V4应当等于(1/4)*VDD。

在一个实施例中,若第四检测结果V4低于(1/4)*VDD,则表示时钟信号CK270与CK0之间的相位差小于90度,控制电路120可产生控制信号Vc以控制时钟信号发生器130延迟时钟信号CK0的相位。同样地,若第四检测结果V4大于(1/4)*VDD,则表示时钟信号CK270与CK0之间的相位差大于90度,控制电路120可产生控制信号Vc以控制时钟信号发生器130使时钟信号CK0的相位提前。

在图5所示的实施例中,第四检测电路118被配置为基于时钟信号CK270和CK0的上升沿检测相位差。在另一实施例中,晶体管M41可由N型晶体管实现,而晶体管M42则由P型晶体管实现,用于根据时钟信号CK270和CK180的下降沿检测相位差。

在图2至图5所示的实施例中,由于第一检测电路112、第二检测电路114、第三检测电路116和第四检测电路118内的组件不需要由电源电压VDD供电,因此电路100的功耗可以大大减少。另外,由于电阻器R11、R21、R31、R41等无源器件的工艺误差较小,因此可以改善第一检测电路112、第二检测电路114、第三检测电路116和第四检测电路118的相位检测失配。

在图2所示的第一检测电路112中,当时钟信号CK0和CK90都为低电压时,由于晶体管M11的较大导通电阻,节点N1可能不完全具有地电压或0V,导致第一检测结果V1具有错误。为解决此问题,可将第一检测电路112修改为具有补偿电路,以在时钟信号CK0和CK90都为低电压时控制节点N1具有接地电压或0V。如图6所示,第一检测电路112'还包括补偿电路,补偿电路包括晶体管M13、电阻器R14和或非(NOR)门610,其中或非门610接收时钟信号CK0和CK90。在图6所示的补偿电路的操作中,当时钟信号CK0和CK90都为低电压时,或非门610的输出信号将使晶体管M13对节点N1进行放电,从而使节点N1具有地电压。因此,第一检测结果V1可以更准确地反映时钟信号CK0和CK90的相位差。

需要说明的是,图6中所示的补偿电路是例示性的,并非对本发明的限制。只要补偿电路能够在晶体管M11被使能且时钟信号CK0为低电压(即时钟信号CK0和CK90均为低电压)时对节点N1进行放电,补偿电路可以具有任何其他合适的设计。在一个实施例中,补偿电路仅在晶体管M11被使能并且时钟信号CK0具有低电压时才对节点N1进行放电。

另外,对于晶体管M11由N型晶体管实现的情况,补偿电路被设计成当时钟信号CK0为低电压且时钟信号CK90为高电压时节点N1被放电。

在图3所示的第二检测电路114中,当时钟信号CK90和CK180都为低电压时,由于晶体管M21的导通电阻较大,节点N2可能不完全为地电压或0V,导致第二检测结果V2有误差。为解决此问题,可将第二检测电路114修改为具有补偿电路,以在时钟信号CK90和CK180都为低电压时控制节点N2具有接地电压或0V。参考图7,第二检测电路114'还包括补偿电路,补偿电路包括晶体管M23、电阻器R24和或非(NOR)门710,其中或非门710接收时钟信号CK90和CK180。在图7所示的补偿电路的操作中,当时钟信号CK90和CK180都为低电压时,或非门710的输出信号将使晶体管M23对节点N2进行放电,从而使节点N2具有地电压。因此,第二检测结果V2可以更准确地反映时钟信号CK90与CK180的相位差。

在图4所示的第三检测电路116中,当时钟信号CK180和CK270都为低电压时,由于晶体管M31的导通电阻较大,节点N3可能不完全为地电压或0V,导致第三检测结果V3有误差。为解决此问题,可将第三检测电路116修改为具有补偿电路,以在时钟信号CK180和CK270均为低电压时控制节点N3具有接地电压或0V。参考图8,第三检测电路116'还包括补偿电路,补偿电路包括晶体管M33、电阻器R34和或非(NOR)门810,其中或非门810接收时钟信号CK180和CK270。在图8所示的补偿电路的操作中,当时钟信号CK180和CK270都为低电压时,或非门810的输出信号将使晶体管M33使节点N3放电,从而使节点N3具有地电压。因此,第三检测结果V3可以更准确地反映时钟信号CK180与CK270的相位差。

在图5所示的第四检测电路118中,由于晶体管M41的导通电阻较大,当时钟信号CK270和CK0都为低电压时,节点N4可能不完全为地电压或0V,导致第四检测结果V4有误差。为解决此问题,可将第四检测电路118修改为具有补偿电路,以在时钟信号CK270和CK0都为低电压时控制节点N4具有接地电压或0V。参考图9,第四检测电路118'还包括补偿电路,补偿电路包括晶体管M43、电阻器R44和或非(NOR)门910,其中或非门910接收时钟信号CK270和CK0。在图9所示的补偿电路的操作中,当时钟信号CK270和CK0都为低电压时,或非门910的输出信号将使晶体管M43对节点N4进行放电,从而使节点N4具有地电压。因此,第四检测结果V4可以更准确地反映时钟信号CK270与CK0的相位差。

在图6至图9所示的实施例中,由于第一检测电路112'、第二检测电路114'、第三检测电路116'和第四检测电路118'内的大部分元件不需要由电源电压VDD供电,因而可以大大降低电路100的功耗。另外,由于电阻器R11、R21、R31、R41等无源器件的工艺误差小,可以改进第一检测电路112'、第二检测电路114'、第三检测电路116'、第四检测电路118'的相位检测失配。

值得注意的是,正交相位检测器110内的检测电路的数量是为了说明,而不是限制本发明。在其他实施例中,正交相位检测器110可以仅具有第一检测电路112,或者正交相位检测器110可以仅具有第一检测电路112和第二检测电路114,或者正交相位检测器110可以仅具有第一检测电路112、第二检测电路114和第三检测电路116。这些替代设计应落入本发明的范围内。

本领域技术人员将容易地理解,在保留本发明的教导的同时,可以对装置和方法进行许多修改和改变。因此,上述公开应被解释为仅受所附权利要求的范围和界限的限制。

- 正交相位检测器电路、正交相位校正器、多天线无线电电路、无线电站和方法

- 正交相位检测器电路、正交相位校正器、多天线无线电电路、无线电站和方法