摄像元件和摄像装置

文献发布时间:2023-06-19 12:07:15

本申请是中国专利申请号为201780032301.4、进入国家阶段日期为2018年11月23日,国际申请日为2017年2月27日、PCT国际申请号为PCT/JP2017/007549、发明名称为“摄像元件和摄像装置”的发明专利申请的分案申请。

技术领域

本发明涉及摄像元件和摄像装置。

背景技术

公知有对相邻的像素的信号进行运算的摄像元件(专利文献1)。该摄像元件在像素的信号间的运算前不进行相关双采样(CDS;Correlated Double Sampling),因此,无法去除各像素的噪声信号成分。

现有技术文献

专利文献

专利文献1:日本特开2001-94888号公报

发明内容

根据本发明的第1方案,摄像元件具有像素基板、和层叠于所述像素基板的运算基板,所述像素基板包括多个像素,该多个像素具有对入射光进行光电转换而生成电荷的光电转换部、和生成并输出基于所述电荷的信号的输出部,所述运算基板包括运算部,该运算部利用将所述输出部的所述电荷重置后的重置信号和基于由所述光电转换部生成的电荷的光电转换信号生成校正信号,进行针对每个所述像素生成的校正信号间的运算。

根据本发明的第2方案,摄像元件具有:像素基板,其配置有具有光电转换部和输出部的多个像素;和运算基板,其针对每个所述像素设置有运算部,该运算部利用重置信号和光电转换信号生成校正信号,进行使用了针对每个所述像素生成的所述校正信号的运算,其中,所述重置信号是对将所述输出部重置后的信号进行数字转换而得到的信号,所述光电转换信号是基于由所述光电转换部光电转换得到的信号进行数字转换而得到的信号,所述像素基板和所述运算基板层叠地配置。

根据本发明的第3方案,摄像装置具备:第1或第2方案的摄像元件;和图像生成部,其基于来自所述像素的信号生成图像数据。

附图说明

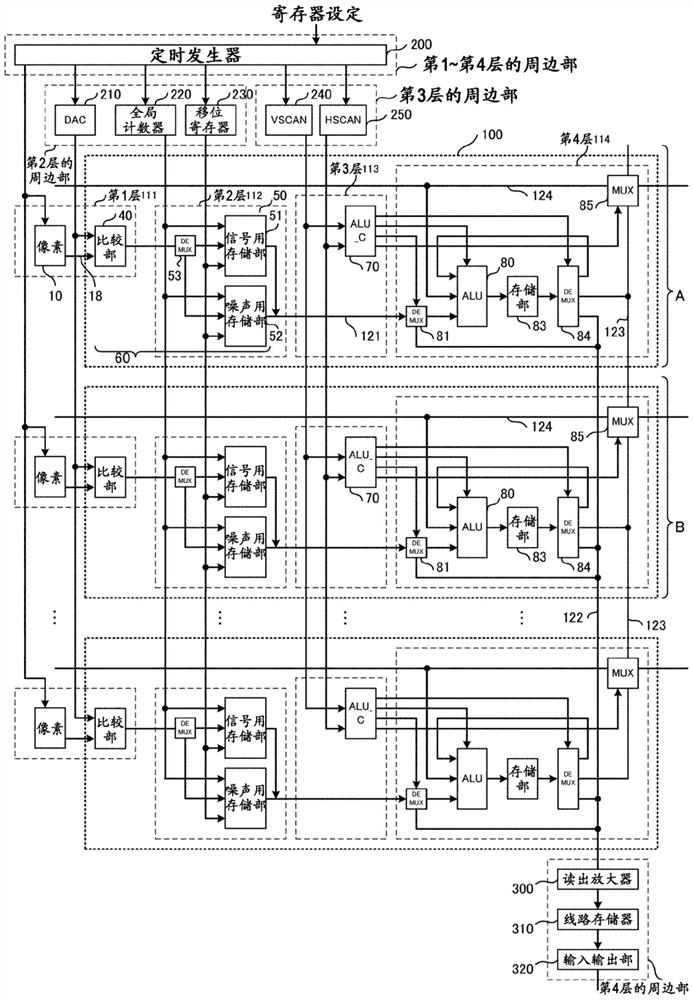

图1是表示第1实施方式的摄像装置的结构的框图。

图2是表示第1实施方式的摄像元件的截面构造的图。

图3是表示第1实施方式的摄像元件的构成的框图。

图4是表示第1实施方式的像素的构成的电路图。

图5是表示第1实施方式的摄像元件的构成的详细情况的框图。

图6是表示第1实施方式的摄像元件的动作的时间图。

图7是表示变形例1的摄像元件的构成的详细情况的框图。

附图标记说明

3:摄像元件,12:光电转换部,10:像素,40:比较部,60:AD转换部,100:运算部。

具体实施方式

(第1实施方式)

图1是表示第1实施方式的摄像装置的结构的框图。摄像装置1具备摄影光学系统2、摄像元件3、以及控制部4。摄像装置1是例如相机。摄影光学系统2使被拍摄体像在摄像元件3上成像。摄像元件3对由摄影光学系统2形成的被拍摄体像进行拍摄而生成图像信号。摄像元件3是例如CMOS图像传感器。控制部4将用于控制摄像元件3的动作的控制信号向摄像元件3输出。另外,控制部4作为图像生成部发挥功能,该图像生成部对从摄像元件3输出的图像信号实施各种图像处理,生成图像数据。此外,摄影光学系统2也可以能够相对于摄像装置1拆装。

图2是表示第1实施方式的摄像元件的截面构造的图。图2所示的摄像元件3是背面照射型的摄像元件。摄像元件3具备第1基板111、第2基板112、第3基板113、以及第4基板114。第1基板111、第2基板112、第3基板113以及第4基板114分别由半导体基板等构成。第1基板111层叠于第2基板112,第2基板112层叠于第3基板113,第3基板113层叠于第4基板114。以空心箭头表示的入射光L朝向Z轴正方向入射。另外,如坐标轴所示,将与Z轴正交的纸面左方向设为X轴正方向,将与Z轴和X轴正交的纸面近前方向设为Y轴正方向。

摄像元件3还具有微透镜层101、彩色滤光片层102、钝化层103。这些钝化层103、彩色滤光片层102以及微透镜层101依次层叠于第1基板111。微透镜层101具有多个微透镜ML。微透镜ML使所入射的光向随后说明的光电转换部12聚光。彩色滤光片层102具有多个彩色滤光片F。钝化层103由氮化膜或氧化膜构成。

第1基板111、第2基板112、第3基板113、以及第4基板114分别具有供栅电极、栅极绝缘膜设置的第1面105a、106a、107a、108a和与第1面不同的第2面105b、106b、107b、108b。另外,在第1面105a、106a、107a、108a分别设置有晶体管等各种元件。在第1基板111的第1面105a、第2基板112的第1面106a、第3基板113的第1面107a、以及第4基板114的第1面108a分别层叠设置有布线层140、141、144、145。另外,在第2基板112的第2面106b和第3基板113的第2面107b分别层叠设置有基板间连接层142、143。布线层140~布线层145是包括导体膜(金属膜)和绝缘膜的层,分别配置有多个布线、导通孔等。

第1基板111的第1面105a的元件和第2基板112的第1面106a的元件经由布线层140、141并通过焊盘、电极等的连接部109而电连接,同样地第3基板113的第1面107a的元件和第4基板114的第1面108a的元件也经由布线层144、145并通过焊盘、电极等的连接部109而电连接。另外,第2基板112和第3基板113具有从基板的第1面贯通到第2面的贯通孔120和从第1面经由贯通孔120配置到第2面的硅贯通电极等的多个贯通电极110。第2基板112的贯通电极110将设置于第2基板112的第1面106a和第2面106b的电路相互连接,第3基板113的贯通电极110将设置于第3基板113的第1面107a和第2面107b的电路相互连接。设置于第2基板112的第2面106b的电路和设置于第3基板113的第2面107b的电路经由基板间连接层142、143并通过焊盘、电极等的连接部109而电连接。

图3是表示第1实施方式的摄像元件的构成的框图。第1基板111具有配置成2维状的多个像素10和比较部40。像素10沿着图2所示的X轴方向和Y轴方向配置有多个。像素10将随后说明的光电转换信号和噪声信号向比较部40输出。比较部40针对每个像素10而设置,由比较电路等构成。比较部40将从像素10输出的光电转换信号和噪声信号分别与基准信号进行比较,并将比较结果向第2基板112输出。第2基板112具有多个存储部50。存储部50针对每个像素10而设置,由锁存电路等构成。存储部50基于比较部40的比较结果,将与从由比较部40进行的比较开始时起经过的经过时间相应的计数值存储为数字信号。存储部50存储与光电转换信号相应的数字信号和与噪声信号相应的数字信号。另外,存储部50也是对转换成数字信号的光电转换信号和噪声信号(重置信号)进行蓄积的蓄积部50。如随后详细说明那样,比较部40和存储部50构成将光电转换信号和噪声信号转换成数字信号的积分型的AD转换部。存储到存储部50的数字信号经由第3基板113向第4基板114输出。

第4基板114具有多个ALU(算术和逻辑单元,Arithmetic and Logic Unit)、即运算单元80。运算单元80针对每个像素10而设置,进行基于光电转换信号的数字信号与噪声信号的数字信号之间的减法运算的相关双采样(CDS;Correlated Double Sampling)、针对每个像素10生成的信号间的运算等信号处理。运算单元80包括加法电路、减法电路、触发电路、以及移相电路等而构成。各运算单元80经由信号线、开关SW等相互连接。

第3基板113具有对运算单元80进行控制的ALU控制部70(以下,称为控制部70)。控制部70按每个像素10设置,将控制信号向配置于第4基板114的运算单元80、开关SW等输出,控制运算单元80所进行的运算内容等。例如,控制部70通过对规定的开关SW进行接通控制来选择像素的信号,与该控制部70相对应的运算单元80对所选择的多个像素的信号进行运算处理。此外,第1基板111也是包括多个像素10的像素基板111,该多个像素10具有光电转换部12和随后说明的读出部(输出部),第2基板112也是包括蓄积部50(存储部50)的蓄积基板112。另外,第4基板114也是包括运算单元80的运算基板114。

在本实施方式中,在各像素10的信号间的运算前进行相关双采样。因此,能够使用将各像素10的噪声信号成分去除后的信号进行任意的像素10的信号间的运算。另外,运算单元80和控制部70分别层叠设置于对应的像素10。因此,能够防止像素10的开口率降低。而且,第3基板113的控制部70从图2所示的Z轴方向向第4基板114的运算单元80供给控制信号而进行运算单元80的控制。其结果,能够不使摄像元件3的芯片面积增大地进行针对任意的像素10的信号的运算。

图4是表示第1实施方式的摄像元件的像素的构成的电路图。像素10具有例如光电二极管(PD)等光电转换部12和读出部20。光电转换部12具有将所入射的光转换成电荷、并蓄积光电转换得到的电荷的功能。读出部20具有传输部13、释放部14、浮置扩散部(FD)15、放大部16、以及电流源17。

传输部13由信号Vtx控制,将由光电转换部12光电转换得到的电荷向浮置扩散部15传输。即,传输部13在光电转换部12与浮置扩散部15之间形成电荷传输路径。浮置扩散部15保持(蓄积)电荷。放大部16对基于保持于浮置扩散部15的电荷的信号进行放大,并向信号线18输出。在图4所示的例子中,放大部16由漏极端子、栅极端子和源极端子分别与电源VDD、浮置扩散部15以及电流源17连接的晶体管M3构成。

释放部(重置部)14由信号Vrst控制,释放浮置扩散部15的电荷,将浮置扩散部15的电位重置成重置电位(基准电位)。传输部13和释放部14例如分别由晶体管M1、晶体管M2构成。

读出部20将与由传输部13从光电转换部12传输到浮置扩散部15的电荷相应的信号(光电转换信号)、以及将浮置扩散部15的电位重置成重置电位时的信号(噪声信号)依次向信号线18读出。读出部20是生成并输出基于蓄积到浮置扩散部15的电荷的信号的输出部20,输出部20将光电转换信号、噪声信号向信号线18输出。

图5是表示第1实施方式的摄像元件的构成的详细情况的框图。摄像元件3具有多个像素10、针对每个像素10设置的运算部100、定时发生器200、DA转换部210、全局计数器220、移位寄存器230、VSCAN电路(垂直扫描电路)240、HSCAN电路(水平扫描电路)250、读出放大器300、线路存储器(line memory)310、以及输入输出部320。运算部100具有模拟/数字转换部(AD转换部)60、控制部70、运算单元80、存储部83、多路分配器(demultiplexer)81、多路分配器84、以及多路复用器(multiplexer)85。AD转换部60由比较部40、存储部50、以及多路分配器53构成。另外,存储部50具有与光电转换信号相应的数字信号用的信号用存储部51和与噪声信号相应的数字信号用的噪声用存储部52。信号用存储部51和噪声用存储部52与所存储的信号的位数相对应地由多个锁存电路构成。例如,信号用存储部51和噪声用存储部52分别由12个锁存电路构成,存储于信号用存储部51和噪声用存储部52的数字信号分别成为12位的并行信号。

在摄像元件3的第1层、即第1基板111设置有像素10、比较部40、以及定时发生器200的一部分。定时发生器200由多个电路构成,分开配置于第1基板111~第4基板114。此外,在图5中,将第1基板111、第2基板112、第3基板113、以及第4基板114分别称为第1层、第2层、第3层以及第4层。构成定时发生器200的各电路配置于像素10、运算部100所配置的区域的周边部。在第2层、即第2基板112设置有信号用存储部51、噪声用存储部52、多路分配器53、DA转换部210、全局计数器220、移位寄存器230、以及定时发生器200的一部分。

在第3基板113设置有控制部70、VSCAN电路240、HSCAN电路250、定时发生器200的一部分。在第4基板114设置有运算单元80、存储部83、多路分配器81、多路分配器84、多路复用器85、读出放大器300、线路存储器310、以及输入输出部320。另外,DA转换部210、全局计数器220、移位寄存器230、VSCAN电路240、HSCAN电路250、读出放大器300、线路存储器310、以及输入输出部320在各基板中配置于运算部100所配置的区域的周边部。

定时发生器200由脉冲生成电路等构成,基于从摄像装置1的控制部4输出的寄存器设定值生成脉冲信号等,并向各像素10、DA转换部210、全局计数器220、移位寄存器230、VSCAN电路240、以及HSCAN电路250输出。寄存器设定值能够根据例如快门速度(光电转换部的电荷蓄积时间)、ISO感光度、图像校正的有无等设定。DA转换部210基于来自定时发生器200的脉冲信号,生成信号电平变化的斜坡信号作为基准信号。另外,DA转换部210与针对每个像素10设置的各比较部40共同连接,将基准信号向各比较部40输出。全局计数器220基于来自定时发生器200的脉冲信号,生成表示计数值的时钟信号,并向信号用存储部51和噪声用存储部52输出。移位寄存器230基于来自定时发生器200的脉冲信号,生成定时信号并向信号用存储部51和噪声用存储部52输出。

VSCAN电路240和HSCAN电路250基于来自定时发生器200的信号依次选择各控制部70,将表示由运算单元80进行的运算内容(四则运算)和成为运算对象的像素10等的信号向各控制部70输出。读出放大器300与每个像素10的各运算部100所连接的信号线122连接,对向信号线122输入的信号进行放大而读出,从而高速地读出信号。由读出放大器300读出来的信号存储于线路存储器310。输入输出部320针对从线路存储器310输出的信号进行信号的位宽的调整、同步代码的附加等信号处理,作为图像信号向摄像装置1的控制部4输出。输入输出部320由与例如LVDS、SLVS等高速接口相对应的输入输出电路等构成而高速地传输信号。

图6是表示第1实施方式的摄像元件的动作例的时间图。在图6中,横轴表示时刻。在时刻t1~时刻t2的期间,从摄像装置1的控制部4向定时发生器200输入寄存器设定。在时刻t2~时刻t3的期间,定时发生器200基于寄存器设定值生成表示各运算单元80的运算内容等的信号,向VSCAN电路240和HSCAN电路250等输出。在时刻t3~时刻t4的期间,VSCAN电路240和HSCAN电路250将由定时发生器200生成的表示运算内容等的信号向针对每个像素10设置的各控制部70依次输出。

在时刻t10~时刻t11的期间,各像素10的噪声信号向比较部40输出。比较部40对从像素10读出来的噪声信号和由DA转换部210供给的基准信号进行比较,并将比较结果向多路分配器53输出。多路分配器53将比较部40的比较结果向噪声用存储部52输出。噪声用存储部52基于比较部40的比较结果和来自全局计数器220的时钟信号,将与从由比较部40进行的比较开始时到比较结果输出时的经过时间相应的计数值存储作为与噪声信号相应的数字信号。

在时刻t11~时刻t12的期间,各像素10的光电转换信号向比较部40输出。比较部40对光电转换信号和基准信号进行比较,并将比较结果向多路分配器53输出。多路分配器53将比较部40的比较结果向信号用存储部51输出。信号用存储部51基于比较部40的比较结果和时钟信号,将与从由比较部40进行的比较开始时到比较结果输出时的经过时间相应的计数值存储为与光电转换信号相应的数字信号。这样,在本实施方式中,在信号用存储部51和噪声用存储部52分别存储12位的数字信号。

另外,在从时刻t11到时刻t12的期间,噪声用存储部52基于来自移位寄存器230的定时信号,使存储到噪声用存储部52的12位的数字信号逐位地随着时间经过而移位,向图5所示的信号线121依次输出。向信号线121输出的串行信号被输入至多路分配器81。多路分配器81将来自噪声用存储部52的串行信号向运算单元80输出。运算单元80使与噪声信号相应的数字信号依次存储于存储部83。这样,存储部83存储与噪声信号有关的12位的数字信号。

信号线121成为将第2基板112的存储部50和第4基板114的多路分配器81连结的信号线,成为使用了图2所示的贯通电极110、焊盘等的信号线。一般而言,难以以窄间距形成许多贯通电极110,难以从第2基板112将许多并行信号向第4基板114同时传输。在本实施方式中,将存储到第2基板112的存储部50的并行信号转换成串行信号而向第4基板114输出。因此,能够减少将第2基板112和第4基板114连结的布线,能够同时输出关于各像素10的数字信号。另外,能够防止形成许多贯通电极110等而导致芯片面积增大。

在时刻t12~时刻t20的期间,信号用存储部51基于来自移位寄存器230的定时信号,将与存储到信号用存储部51的光电转换信号相应的数字信号转换成串行信号,经由信号线121向多路分配器81逐位地依次输出。多路分配器81将来自信号用存储部51的串行信号向运算单元80输出。运算单元80基于来自控制部70的控制信号,使与存储到存储部83的噪声信号相应的12位的数字信号逐位地向多路分配器84输出。多路分配器84基于来自控制部70的控制信号,将与噪声信号相应的数字信号向运算单元80输出(反馈)。

运算单元80进行与从信号用存储部51逐位地输出的光电转换信号相应的数字信号、和与从存储部83逐位地输出的噪声信号相应的数字信号之间的减法运算而生成校正信号。运算单元80使按照每1位生成的校正信号依次存储于存储部83。运算单元80与向存储部50存储的信号的位数相应地进行多次减法运算,使成为减法运算结果的校正信号依次存储于存储部83。在本实施方式中,在构成存储部50的信号用存储部51和噪声用存储部52中分别存储12位的数字信号,因此,进行12次减法运算处理。在存储部83中存储与12位的噪声信号相应的数字信号和12位的校正信号。因此,存储部83由24个锁存电路等构成。

如此,在本实施方式中,按照每1位分时地进行数字CDS,在该数字CDS中进行光电转换信号的数字信号与噪声信号的数字信号的差分处理。另外,运算单元80针对每个像素10而设置,在全部像素10中同时进行数字CDS。由于按照每1位进行数字CDS运算,因此在第4基板114中,能够避免配置多位(例如12位)的触发电路等许多数字电路。其结果,能够减少各像素10的电路数,能够防止芯片面积增大。

在时刻t30~时刻t40的期间,进行与在图5中例如分别配置于彼此相邻的区域A和区域B的两个像素10有关的校正信号间的运算。即,存储在区域A的存储部83中的区域A的像素10的12位的校正信号逐位地经由多路分配器84向区域A的运算单元80输入(反馈)。同样地,存储在区域B的存储部83中的区域B的像素10的12位的校正信号逐位地分别经由区域B的多路分配器84、区域B的多路复用器85以及区域A的多路复用器85向区域A的运算单元80输入。区域A的运算单元80对如此输入的区域A的12位的校正信号和区域B的12位的校正信号逐位地进行运算。以下详细地说明。

在配置于区域A的运算部100中,区域A的运算单元80使存储在区域A的存储部83中的区域A的像素10的12位的校正信号逐位地向多路分配器84输出。区域A的多路分配器84将校正信号向区域A的运算单元80输出(反馈)。另外,在配置于区域B的运算部100中,区域B的运算单元80使存储在区域B的存储部83中的区域B的像素10的校正信号逐位地向多路分配器84输出。区域B的多路分配器84将校正信号向区域B的多路复用器85输出。

在针对每个像素10设置的各多路复用器85连接有各运算部100所连接的信号线123和信号线124。信号线123和信号线124例如在第4基板114中沿着行方向和列方向配置成二维状,与每个像素10的各运算部100连接。多路复用器85由控制部70控制,从向信号线123和信号线124输入的校正信号选择成为运算单元80的运算对象的信号。区域B的多路复用器85将区域B的像素10的校正信号经由图5所示的信号线123向区域A的多路复用器85输出。区域A的多路复用器85将区域B的像素10的校正信号经由信号线124向区域A的运算单元80输出。区域A的像素10的校正信号和区域B的像素10的校正信号分别按照每1位依次输入区域A的运算单元80。

区域A的运算单元80进行从区域A的存储部83逐位地输出的校正信号、和从区域B的存储部83逐位地输出的校正信号的运算,生成像素信号。运算单元80使按照每1位生成的像素信号依次存储于存储部83。运算单元80与校正信号的位数相应地进行多次运算,使成为运算结果的像素信号依次存储于存储部83。在校正信号间的运算后,12位的校正信号和12位的像素信号存储于存储部83。

如此,在本实施方式中,在各像素10的校正信号间的运算前进行相关双采样而生成校正信号。因此,能够使用将各像素10的噪声信号成分去除后的信号来进行任意的像素10的校正信号间的运算。另外,在本实施方式中,按照每1位进行针对每个像素10生成的校正信号间的运算。其结果,在第4基板114中,能够避免配置多位(例如12位)的四则运算电路、多位(例如12位)的触发电路等多位的数字电路,能够防止芯片面积增大。由于按照每1位进行校正信号间的运算,因此能够减小运算单元80的电路面积。而且,运算单元80进行相关双采样,并且进行各像素10的校正信号间的运算。即,运算单元80作为校正及像素间运算部发挥功能,该校正及像素间运算部兼用作通过数字信号间之间的减法运算生成校正信号的校正部、和进行针对每个像素10生成的校正信号间的运算的像素间运算部。因此,与分别设置校正部和像素间运算部的情况相比较,能够减小芯片面积。

在本实施方式中,还具有除配置控制部70的第3基板113之外的第4基板114,将运算单元80和多路复用器85等配置于第4基板114。因此,能够不使芯片面积增大地将信号线123和信号线124配置成二维状并与全部的像素10的运算部100共同连接。从控制部70输出控制信号而对运算单元80和多路复用器85等进行控制,由此能够进行任意的像素10的校正信号间的运算。能够对相邻的像素间、配置于分开的区域的像素间进行运算。另外,运算部100进行运算的其他像素10的校正信号不经由锁存器、寄存器等,由信号线123和信号线124直接传输。不产生用于通过锁存器、寄存器等的延迟时间,因此,能够高速地读出信号,能够高速地进行关于任意的像素10间的运算。

在时刻t50~时刻t60的期间,运算单元80使存储到存储部83的像素信号向多路分配器84输出。多路分配器84将像素信号向信号线122输出。读出放大器300对输出到信号线122的像素信号进行放大而读出。按每个像素10设置的各运算部100向信号线122依次输出信号,读出放大器300将输出到信号线122的信号依次读出。

在时刻t70~时刻t80的期间,由读出放大器300读出来的像素信号依次存储于线路存储器310。输入输出部320对从线路存储器310依次输出的信号进行信号处理,将信号处理后的信号作为图像信号输出。

根据上述的实施方式,获得如下作用效果。

(1)摄像元件3具备:多个像素10,其具有光电转换部12;和运算部100,其针对每个像素10而设置,利用从像素10输出的光电转换信号和从像素10输出的噪声信号生成校正信号,进行针对每个像素10生成的校正信号间的运算。在本实施方式中,在各像素10的信号间的运算前进行相关双采样而生成校正信号。因此,能够使用将各像素10的噪声信号成分去除后的信号进行任意的像素10的信号间的运算。

(2)运算部100具有:AD转换部60,其将光电转换信号转换成第1数字信号,将噪声信号转换成第2数字信号;和校正及像素间运算部(运算单元80),其通过第1数字信号与第2数字信号之间的减法运算生成校正信号,进行针对每个像素10生成的校正信号间的运算。由于如此设置,从而与分别设置校正部和像素间运算部的情况相比较,而能够减小各像素10的周边电路的面积,能够减小芯片面积。

(3)光电转换部12配置于第1基板,运算部100的至少一部分配置于第2基板。由于如此设置,从而能够防止像素10的开口率降低。

(4)AD转换部60将光电转换信号转换成第1位数的第1数字信号,将噪声信号转换成第2位数的第2数字信号。由于如此设置,从而能够将光电转换信号和噪声信号分别转换成数字信号而使存储部50存储。

(5)运算部100具有存储第2位数的第2数字信号的存储部83。运算部100按照每1位进行所存储的第2数字信号与从AD转换部60输出的第1数字信号之间的减法运算。在本实施方式中,按照每1位进行光电转换信号的数字信号与噪声信号的数字信号的差分处理。由于如此设置,从而能够避免针对每个像素10设置许多触发电路等,能够防止芯片面积增大。

(6)运算部100按照每1位进行针对每个像素10生成的校正信号间的运算。由于如此设置,从而能够避免为了进行各像素10的信号间的运算的像素间运算而设置许多四则运算电路、触发电路等,能够防止芯片面积增大。

(7)摄像元件3还具备多个信号线(信号线123和信号线124),该多个信号线与多个运算部100连接,从运算部100向该多个信号线输出校正信号。运算部100具有从输出到多个信号线的校正信号选择运算部100进行运算的校正信号的第1选择部(多路复用器85)。在本实施方式中,利用控制部70对运算单元80和多路复用器85进行控制,选择并读出各像素10的校正信号。因此,能够进行任意的像素10的校正信号间的运算。

(8)摄像元件3具有像素基板(第1基板111)、和层叠于像素基板的运算基板(第4基板114),所述像素基板包括多个像素10,该多个像素10具有对入射光进行光电转换而生成电荷的光电转换部12、和生成并输出基于电荷的信号的输出部20(读出部20),所述运算基板包括运算部(运算单元80),该运算部利用将输出部20的电荷重置后的重置信号和基于由光电转换部12生成的电荷的光电转换信号生成校正信号,进行针对每个像素10生成的校正信号间的运算。由于如此设置,从而能够使用将各像素10的噪声信号成分去除后的信号进行任意的像素10的信号间的运算。另外,由于运算单元80分别层叠设置于所对应的像素10,从而能够防止像素10的开口率降低。

(9)摄像元件3具有蓄积基板(第2基板112),该蓄积基板(第2基板112)包括蓄积被转换成数字信号的光电转换信号和重置信号的蓄积部(存储部50)。蓄积基板层叠配置于像素基板与运算基板之间。由于如此设置,从而能够防止像素10的开口率降低。

如下那样的变形也在本发明的范围内,也能够将变形例的一个或者多个与上述的实施方式组合。

(变形例1)

在上述的实施方式中,对运算单元80共用于进行CDS处理的校正部和进行像素间运算的像素间运算的例子进行了说明。不过,如图7所示,也可以将进行CDS处理的校正部54与运算单元80分开地设置。在该情况下,运算单元80作为像素间运算部发挥功能。校正部54通过基于从信号用存储部51输出的光电转换信号的数字信号、和基于从噪声用存储部52输出的噪声信号的数字信号之间的减法运算来生成校正信号,经由多路分配器81向运算单元80输出。

(变形例2)

在上述的实施方式中,对将成为像素间运算的结果的像素信号经由信号线122向读出放大器300依次输出的例子进行了说明。不过,也可以是,运算部100将存储到存储部83的校正信号作为像素信号经由信号线122向读出放大器300输出。另外,也可以是,将与存储到信号用存储部51的光电转换信号相应的数字信号以及与存储到噪声用存储部52的噪声信号相应的数字信号分别经由多路分配器81向信号线122输出。

(变形例3)

在上述的实施方式中,说明了按照每1位分时地进行CDS处理和像素间运算的例子。不过,也可以利用控制部70对运算单元80等进行控制,而按照每多个位数进行运算。例如,可以按照每两位进行运算,也可以按照每比存储于噪声用存储部52的数字信号的位数少的位数进行。

(变形例4)

在上述的实施方式中,说明了在各像素10的信号间的运算前进行数字CDS的例子。不过,也可以在各像素10的信号间的运算前进行模拟CDS。例如,在AD转换部60中,进行光电转换信号与噪声信号的差分处理,将基于信号间的差分的模拟信号转换成数字信号。在存储部50中存储将各像素10的噪声信号成分去除后的数字信号。存储到存储部50的数字信号向运算单元80依次输出。

(变形例5)

在上述的实施方式中,对使用光电二极管作为光电转换部12的例子进行了说明。不过,也可以使用光电转换膜作为光电转换部12。

在上述内容中,对各种实施方式和变形例进行了说明,但本发明并不限定于这些内容。在本发明的技术思想的范围内所想到的其他形态也包含于本发明的范围内。

以下优先权基础申请的公开内容作为引用文编入于此。

日本专利申请2016年第60001号(2016年3月24日申请)。

- 摄像元件、摄像元件的驱动装置、摄像元件的驱动方法、图像处理装置、及摄像装置

- 固体摄像元件、具备该固体摄像元件的摄像装置、以及摄像控制方法和摄像控制程序