多赫蒂放大器和通信装置

文献发布时间:2023-06-19 13:46:35

技术领域

本发明涉及多赫蒂放大器和通信装置。

背景技术

一般的多赫蒂放大器在载波放大器的输出侧连接有相移要素,在峰值放大器的输入侧连接有相移要素。

与此相对,在以下的专利文献1中公开有如下的多赫蒂放大器:在载波放大器的输出信号与峰值放大器的输出信号之间,能够对振幅和相位分别进行匹配。

在专利文献1公开的多赫蒂放大器中,在载波放大器的前级连接有第1相位调整器,在峰值放大器的前级连接有第2相位调整器。

在专利文献1公开的多赫蒂放大器中,第1相位调整器对输入到载波放大器的信号的相位进行调整,第2相位调整器对输入到峰值放大器的信号的相位进行调整。

在专利文献1公开的多赫蒂放大器中,在载波放大器和峰值放大器双方进行动作时,载波放大器的输出功率和峰值放大器的输出功率被加法节点合成。

现有技术文献

专利文献

专利文献1:日本特开2015-89130号公报

发明内容

发明要解决的课题

在专利文献1公开的多赫蒂放大器中,即使输入信号的频率变化,也无法对从载波放大器观察加法节点时的阻抗进行调制。此外,即使输入信号的频率变化,也无法对从峰值放大器观察加法节点时的阻抗进行调制。因此,存在多赫蒂放大器的放大效率有时劣化这样的课题。

本发明正是为了解决上述课题而完成的,其目的在于,得到一种多赫蒂放大器和通信装置,即使由第1晶体管放大的第1信号的频率和由第2晶体管放大的第2信号的频率变化,也能够使回退时的效率特性宽带化。

用于解决课题的手段

本发明的多赫蒂放大器具有:第1晶体管,其对第1信号进行放大,输出放大后的第1信号;第2晶体管,其对第2信号进行放大,输出放大后的第2信号;以及合成电路,其对从第1晶体管输出的放大后的第1信号和从第2晶体管输出的放大后的第2信号进行合成,输出放大后的第1信号与放大后的第2信号的合成信号,根据频率以同相方式合成由第1晶体管放大的第1信号和由第2晶体管放大的第2信号的信号模式、以及以异相方式合成由第1晶体管放大的第1信号和由第2晶体管放大的第2信号的信号模式进行切换,动作模式根据切换后的信号模式而被切换成多赫蒂动作模式或异相动作模式。

发明效果

根据本发明,以如下方式构成多赫蒂放大器:根据频率对以同相方式合成由第1晶体管放大的第1信号和由第2晶体管放大的第2信号的信号模式、以及以异相方式合成由第1晶体管放大的第1信号和由第2晶体管放大的第2信号的信号模式进行切换,动作模式根据切换后的信号模式而被切换成多赫蒂动作模式或异相动作模式。因此,在本发明的多赫蒂放大器中,即使由第1晶体管放大的第1信号的频率和由第2晶体管放大的第2信号的频率变化,也能够使回退时的效率特性宽带化。

附图说明

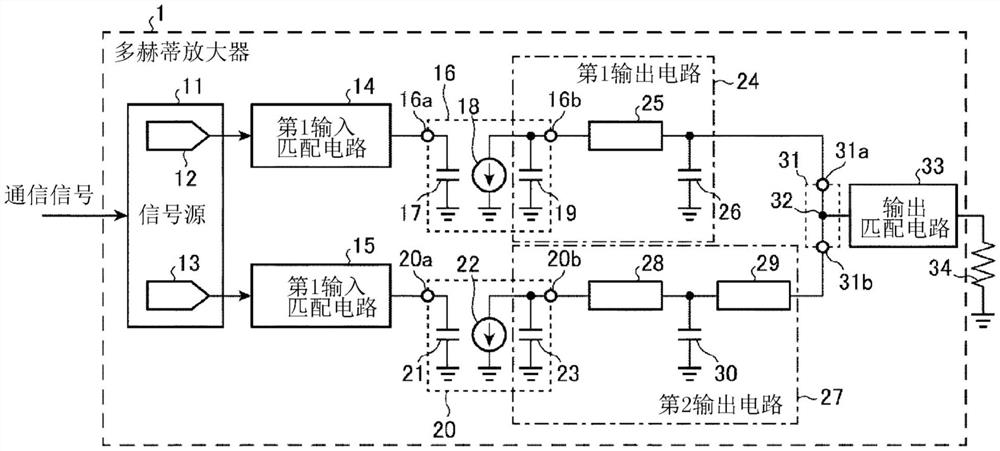

[图1]是示出具有实施方式1的多赫蒂放大器1的通信装置的结构图。

[图2]是示出多赫蒂放大器1具有的多个动作模式的频率的说明图。

[图3]是示出实施方式1的多赫蒂放大器1的结构图。

[图4]图4A是示出从第1输入信号源12输出的第1信号的振幅和从第2输入信号源13输出的第2信号的振幅的说明图,图4B是示出从第1输入信号源12输出的第1信号的相位和从第2输入信号源13输出的第2信号的相位的说明图,图4C是示出从第1输入信号源12输出的第1信号的相位与从第2输入信号源13输出的第2信号的相位的相位差的说明图。

[图5]是示出第1多赫蒂动作模式下的多赫蒂放大器1的回退时动作的说明图。

[图6]是示出第1多赫蒂动作模式下的多赫蒂放大器1的回退时动作中的负载变化的说明图。

[图7]图7A是示出从第1输入信号源12输出的第1信号的振幅和从第2输入信号源13输出的第2信号的振幅的说明图,图7B是示出从第1输入信号源12输出的第1信号的相位和从第2输入信号源13输出的第2信号的相位的说明图,图7C是示出从第1输入信号源12输出的第1信号的相位与从第2输入信号源13输出的第2信号的相位的相位差的说明图。

[图8]是示出第1异相动作模式下的多赫蒂放大器1的回退时动作的说明图。

[图9]是示出第1异相动作模式下的多赫蒂放大器1的回退时动作中的负载变化的说明图。

[图10]图10A是示出从第1输入信号源12输出的第1信号的振幅和从第2输入信号源13输出的第2信号的振幅的说明图,图10B是示出从第1输入信号源12输出的第1信号的相位和从第2输入信号源13输出的第2信号的相位的说明图,图10C是示出从第1输入信号源12输出的第1信号的相位与从第2输入信号源13输出的第2信号的相位的相位差的说明图。

[图11]是示出第2异相动作模式下的多赫蒂放大器1的回退时动作的说明图。

[图12]图12A是示出从第1输入信号源12输出的第1信号的振幅和从第2输入信号源13输出的第2信号的振幅的说明图,图12B是示出从第1输入信号源12输出的第1信号的相位和从第2输入信号源13输出的第2信号的相位的说明图,图12C是示出从第1输入信号源12输出的第1信号的相位与从第2输入信号源13输出的第2信号的相位的相位差的说明图。

[图13]是示出第2多赫蒂动作模式下的多赫蒂放大器1的回退时动作的说明图。

[图14]图14A是示出从第1输入信号源12输出的第1信号的振幅和从第2输入信号源13输出的第2信号的振幅的说明图,图14B是示出从第1输入信号源12输出的第1信号的相位和从第2输入信号源13输出的第2信号的相位的说明图,图14C是示出从第1输入信号源12输出的第1信号的相位与从第2输入信号源13输出的第2信号的相位的相位差的说明图。

[图15]是示出第3多赫蒂动作模式下的多赫蒂放大器1的回退时动作的说明图。

[图16]是示出实施方式5的多赫蒂放大器1的第1输出电路24的结构图。

[图17]是示出实施方式5的多赫蒂放大器1的第2输出电路27的结构图。

[图18]是示出实施方式6的多赫蒂放大器1的第1输出电路24的结构图。

[图19]是示出实施方式6的多赫蒂放大器1的第2输出电路27的结构图。

[图20]是示出实施方式8的多赫蒂放大器1的结构图。

[图21]是示出实施方式9的多赫蒂放大器1的结构图。

具体实施方式

下面,为了更加详细地说明本发明,按照附图对用于实施本发明的方式进行说明。

实施方式1

图1是示出具有实施方式1的多赫蒂放大器1的通信装置的结构图。

在图1中,多赫蒂放大器1将通信用信号分配成第1信号和第2信号,分别对第1信号和第2信号进行放大。

多赫蒂放大器1根据频率对以同相方式合成由第1晶体管16放大的第1信号和由第2晶体管20放大的第2信号的信号模式、以及以异相方式合成由第1晶体管16放大的第1信号和由第2晶体管20放大的第2信号的信号模式进行切换。

此外,多赫蒂放大器1的动作模式根据切换后的信号模式而被切换成多赫蒂动作模式或异相动作模式。

如图2所示,多赫蒂放大器1具有第1多赫蒂动作模式、第2多赫蒂动作模式和第3多赫蒂动作模式,作为使其作为多赫蒂放大器进行动作的同相的动作模式。

此外,如图2所示,多赫蒂放大器1具有第1异相动作模式和第2异相动作模式,作为使其作为异相放大器进行动作的异相的动作模式。

图2是示出多赫蒂放大器1具有的多个动作模式的频率的说明图。

多赫蒂放大器1的动作模式由从第1输入信号源12输出的第1信号的频率和从第2输入信号源13输出的第2信号的频率决定。第1输入信号源12和第2输入信号源13在后面叙述。

第1多赫蒂动作模式是从第1输入信号源12输出的第1信号的频率和从第2输入信号源13输出的第2信号的频率分别是第1频率f

第1异相动作模式是从第1输入信号源12输出的第1信号的频率和从第2输入信号源13输出的第2信号的频率分别是比第1频率f

第2异相动作模式是从第1输入信号源12输出的第1信号的频率和从第2输入信号源13输出的第2信号的频率分别是比第1频率f

第2多赫蒂动作模式是从第1输入信号源12输出的第1信号的频率和从第2输入信号源13输出的第2信号的频率分别是比第2频率f

第3多赫蒂动作模式是从第1输入信号源12输出的第1信号的频率和从第2输入信号源13输出的第2信号的频率分别是比第3频率f

多赫蒂放大器1具有的各个动作模式包含第1晶体管16和第2晶体管20双方的输出功率是饱和功率时的饱和输出时动作,作为第1晶体管16和第2晶体管20各自的动作。第1晶体管16和第2晶体管20在后面叙述。

此外,多赫蒂放大器1具有的各个动作模式包含第1晶体管16和第2晶体管20双方的输出功率为饱和功率以下时的回退时动作,作为第1晶体管16和第2晶体管20各自的动作。

在第1多赫蒂动作模式、第2多赫蒂动作模式和第3多赫蒂动作模式分别包含的回退时动作中,仅第1晶体管16或第2晶体管20中的一方进行动作,另一方停止动作。

在第1异相动作模式和第2异相动作模式分别包含的回退时动作中,第1晶体管16和第2晶体管20双方进行动作。

图2除了示出多赫蒂放大器1具有的各个动作模式的频率以外,还示出各个动作模式中包含的回退时动作时的多赫蒂放大器1的效率。

图3是示出实施方式1的多赫蒂放大器1的结构图。

在图3中,信号源11具有第1输入信号源12和第2输入信号源13。

信号源11将输入到该信号源11的通信信号分配成2个信号。

信号源11将2个信号中的一个信号输出到第1输入信号源12,将另一个信号输出到第2输入信号源13。

第1输入信号源12例如通过正交调制器、DAC(Digital Analog Convertor:数字模拟转换器)和DDS(Direct Digital Synthesize:直接数字合成)来实现。

第1输入信号源12根据多赫蒂放大器1的动作模式,分别决定振幅和相位,将分别具有已决定的振幅和相位的电压的信号作为第1信号经由第1输入匹配电路14输出到第1晶体管16。第1信号包含与一个信号中包含的信息相同的信息。

第2输入信号源13例如通过正交调制器、DAC和DDS来实现。

第2输入信号源13根据多赫蒂放大器1的动作模式,分别决定振幅和相位,将分别具有已决定的振幅和相位的电压的信号作为第2信号经由第2输入匹配电路15输出到第2晶体管20。第2信号包含与另一个信号中包含的信息相同的信息。

第1输入匹配电路14和第2输入匹配电路15分别例如通过使用集中常数元件的电路、使用分布常数线路的电路、组合集中常数和分布常数的电路、使用线圈和电容器的L-C型匹配电路或四分之一波长线路来实现。

第1输入匹配电路14的一端与第1输入信号源12连接,第1输入匹配电路14的另一端与第1晶体管16的输入端子16a连接。

第1输入匹配电路14将第1输入信号源12的阻抗转换成第1晶体管16的输入阻抗,将从第1输入信号源12输出的第1信号输出到第1晶体管16的输入端子16a。

第2输入匹配电路15的一端与第2输入信号源13连接,第2输入匹配电路15的另一端与第2晶体管20的输入端子20a连接。

第2输入匹配电路15将第2输入信号源13的阻抗转换成第2晶体管20的输入阻抗,将从第2输入信号源13输出的第2信号输出到第2晶体管20的输入端子20a。

第1晶体管16例如通过FET(Field Effect Transistor:场效应晶体管)、HBT(Heterojunction Bipolar Transistor:异质结双极性晶体管)或HEMT(High ElectronMobility Transistor:高电子迁移率晶体管)来实现。

在图3所示的多赫蒂放大器1中,示出第1晶体管16是源极接地的晶体管的例子。第1晶体管16的输入端子16a即栅极端子与第1输入匹配电路14的另一端连接,第1晶体管16的输出端子16b即漏极端子与第1输出电路24中的第1传输线路25的一端连接。第1输出电路24在后面叙述。

第1晶体管16根据频率对作为多赫蒂放大器进行动作的同相和作为异相放大器进行动作的异相进行切换。

第1晶体管16对从第1输入信号源12经由第1输入匹配电路14输出的第1信号进行放大,将放大后的第1信号输出到第1输出电路24的第1传输线路25。

对第1晶体管16的输入端子16a施加与临界电压大致相同的偏置电压。如果输入端子16a的电压比临界电压大,则第1晶体管16进行信号的放大动作,如果输入端子16a的电压为临界电压以下,则第1晶体管16不进行信号的放大动作。

因此,能够根据有无针对第1晶体管16的输入端子16a的第1信号,对第1晶体管16的动作进行切换。

在利用等效电路表示第1晶体管16时,第1晶体管16能够通过具有输入电容的电容器17、电流源18和具有输出电容的电容器19来表示。

第2晶体管20例如通过FET、HBT或HEMT来实现。

在图3所示的多赫蒂放大器1中,示出第2晶体管20是源极接地的晶体管的例子。第2晶体管20的输入端子20a即栅极端子与第2输入匹配电路15的另一端连接,第2晶体管20的输出端子20b即漏极端子与第2输出电路27中的第2传输线路28的一端连接。第2输出电路27在后面叙述。

第2晶体管20根据频率对作为多赫蒂放大器进行动作的同相和作为异相放大器进行动作的异相进行切换。

第2晶体管20对从第2输入信号源13经由第2输入匹配电路15输出的第2信号进行放大,将放大后的第2信号输出到第2输出电路27的第2传输线路28。

对第2晶体管20的输入端子20a施加与临界电压大致相同的偏置电压。如果输入端子20a的电压比临界电压大,则第2晶体管20进行信号的放大动作,如果输入端子20a的电压为临界电压以下,则第2晶体管20不进行信号的放大动作。

因此,能够根据有无针对第2晶体管20的输入端子20a的第2信号,对第2晶体管20的动作进行切换。

在利用等效电路表示第2晶体管20时,第2晶体管20能够通过具有输入电容的电容器21、电流源22和具有输出电容的电容器23来表示。

第1输出电路24具有电容器19、第1传输线路25和第1电容器26。

在图3所示的多赫蒂放大器1中,以共用具有第1晶体管16的输出电容的电容器19的方式描绘第1晶体管16和第1输出电路24。但是,这只不过是为了便于说明而以共用的方式进行描绘,第1输出电路24也可以不与第1晶体管16共用电容器19,而仅具有第1传输线路25和第1电容器26。

第1输出电路24传输从第1晶体管16输出的第1信号,将第1信号输出到合成电路31。

第1输出电路24根据由第1晶体管16放大的第1信号的频率,对从第1晶体管16观察合成电路31时的阻抗进行调制。

第1输出电路24的电长度根据第1信号的频率而变化。例如,在第1信号的频率是包含第1频率f

第1传输线路25的一端与第1晶体管16的输出端子16b连接,第1传输线路25的另一端与合成电路31的输入端子31a和第1电容器26的一端分别连接。

第1传输线路25例如是在第1信号的频率为第1频率f

第1传输线路25的特性阻抗比第1晶体管16的输出电阻高。

第1电容器26与第1传输线路25并联连接。即,第1电容器26的一端与第1传输线路25的另一端和合成电路31的输入端子31a分别连接,第1电容器26的另一端与地线连接。

第1电容器26具有的电容与第1晶体管16的输出电容即电容器19具有的电容相同。但是,第1电容器26具有的电容不限于与电容器19具有的电容严格一致,在实用方面没有问题的范围内,也可以与电容器19具有的电容不同。

第2输出电路27具有电容器23、第2传输线路28、第3传输线路29和第2电容器30。

在图3所示的多赫蒂放大器1中,以共用具有第2晶体管20的输出电容的电容器23的方式描绘第2晶体管20和第2输出电路27。但是,这只不过是为了便于说明而以共用的方式进行描绘,第2输出电路27也可以不与第2晶体管20共用电容器23,而仅具有第2传输线路28、第3传输线路29和第2电容器30。

第2输出电路27具有比第1传输线路25的电长度长的电长度,传输从第2晶体管20输出的第2信号,将第2信号输出到合成电路31。

第2输出电路27根据由第2晶体管20放大的第2信号的频率,对从第2晶体管20观察合成电路31时的阻抗进行调制。

第2输出电路27的电长度根据第2信号的频率而变化。例如,在第2信号的频率是包含第1频率f

第2传输线路28的一端与第2晶体管20的输出端子20b连接,第2传输线路28的另一端与第3传输线路29的一端和第2电容器30的一端分别连接。

第2传输线路28例如是在第2信号的频率为第1频率f

第2传输线路28的特性阻抗比第2晶体管20的输出电阻高。

第3传输线路29的一端与第2传输线路28的另一端和第2电容器30的一端分别连接,第3传输线路29的另一端与合成电路31的输入端子31b连接。

第3传输线路29例如是在第2信号的频率为中心频率f

第3传输线路29的特性阻抗与第2晶体管20的输出电阻相同。但是,第3传输线路29的特性阻抗不限于与第2晶体管20的输出电阻严格一致,在实用方面没有问题的范围内,也可以与第2晶体管20的输出电阻不同。

第2电容器30与第2传输线路28并联连接。即,第2电容器30的一端与第2传输线路28的另一端和第3传输线路29的一端分别连接,第2电容器30的另一端与地线连接。

第2电容器30具有的电容与第2晶体管20的输出电容即电容器23具有的电容相同。但是,第2电容器30具有的电容不限于与电容器23具有的电容严格一致,在实用方面没有问题的范围内,也可以与电容器23具有的电容不同。

合成电路31具有对由第1输出电路24传输的第1信号和由第2输出电路27传输的第2信号进行合成的合成点32。

合成电路31的输入端子31a与第1传输线路25的另一端和第1电容器26的一端分别连接。

合成电路31的输入端子31b与第3传输线路29的另一端连接。

合成电路31对从第1输出电路24输出的第1信号和从第2输出电路27输出的第2信号进行合成。

合成点32是从第1输出电路24输出的第1信号和从第2输出电路27输出的第2信号的合成点。如果包含合成点,则称作合成电路。

这里,同相是指在合成点32对由第1输出电路24传输的第1信号和由第2输出电路27传输的第2信号进行同相合成。例如,即使输入到第1晶体管16的第1信号和输入到第2晶体管20的第2信号在输入端面为异相,如果由第1输出电路24传输且相位变化的第1信号和由第2输出电路27传输且相位变化的第2信号在合成点32为同相,则为同相。异相是指在合成点32对由第1输出电路24传输的第1信号和由第2输出电路27传输的第2信号进行异相合成。例如,即使输入到第1晶体管16的第1信号和输入到第2晶体管20的第2信号在输入端面为同相,如果由第1输出电路24传输且相位变化的第1信号和由第2输出电路27传输且相位变化的第2信号在合成点32为异相,则为异相。

输出匹配电路33例如通过使用集中常数元件的电路、使用分布常数线路的电路、组合集中常数和分布常数的电路、使用线圈和电容器的L-C型匹配电路或四分之一波长线路来实现。

输出匹配电路33的一端与合成点32连接,输出匹配电路33的另一端与多赫蒂放大器1外部的负载34连接。

输出匹配电路33是使合成点32的阻抗与负载34的阻抗匹配的电路。

负载34是与输出匹配电路33的另一端连接的多赫蒂放大器1外部的负载。

图3所示的多赫蒂放大器1具有输出匹配电路33。但是,这只不过是一例,如果第1输出电路24和第2输出电路27分别具有与负载34的阻抗匹配的匹配功能,则多赫蒂放大器1也可以不具有输出匹配电路33。

接着,对图3所示的多赫蒂放大器1的动作进行说明。

在实施方式1中,为了便于说明,设被输入的通信信号的频率是第1频率f

因此,在实施方式1中,设图3所示的多赫蒂放大器以第1多赫蒂动作模式或第1异相动作模式进行动作。

最初,对多赫蒂放大器1的动作的概略进行说明。

信号源11将输入到该信号源11的通信信号分配成2个信号。

信号源11将2个信号中的一个信号输出到第1输入信号源12,将另一个信号输出到第2输入信号源13。

如果一个信号的频率是第1频率f

第1输入信号源12在将多赫蒂放大器1的动作模式决定为第1多赫蒂动作模式后,将与第1多赫蒂动作模式对应的具有振幅和相位的电压的信号作为第1信号经由第1输入匹配电路14输出到第1晶体管16。

第1输入信号源12在将多赫蒂放大器1的动作模式决定为第1异相动作模式后,将与第1异相动作模式对应的具有振幅和相位的电压的信号作为第1信号经由第1输入匹配电路14输出到第1晶体管16。

另外,第1信号包含与一个信号中包含的信息相同的信息。

如果从信号源11输出的另一个信号的频率是第1频率f

第2输入信号源13在将多赫蒂放大器1的动作模式决定为第1多赫蒂动作模式后,将与第1多赫蒂动作模式对应的具有振幅和相位的电压的信号作为第2信号经由第2输入匹配电路15输出到第2晶体管20。

第2输入信号源13在将多赫蒂放大器1的动作模式决定为第1异相动作模式后,将与第1异相动作模式对应的具有振幅和相位的电压的信号作为第2信号经由第2输入匹配电路15输出到第2晶体管20。

另外,第2信号包含与另一个信号中包含的信息相同的信息。

第1晶体管16在经由第1输入匹配电路14接受从第1输入信号源12输出的第1信号后,对第1信号进行放大,将放大后的第1信号输出到第1输出电路24中的第1传输线路25。

第2晶体管20在经由第2输入匹配电路15接受从第2输入信号源13输出的第2信号后,对第2信号进行放大,将放大后的第2信号输出到第2输出电路27中的第2传输线路28。

第1输出电路24在从第1晶体管16的输出端子16b输出第1信号后,传输第1信号,将第1信号输出到合成电路31。

第2输出电路27在从第2晶体管20的输出端子20b输出第2信号后,传输第2信号,将第2信号输出到合成电路31。

合成电路31对由第1输出电路24传输的第1信号和由第2输出电路27传输的第2信号进行合成。

合成电路31将第1信号与第2信号的合成信号经由输出匹配电路33输出到外部的负载34。

接着,对第1多赫蒂动作模式下的多赫蒂放大器1的饱和输出时动作和第1多赫蒂动作模式下的多赫蒂放大器1的回退时动作进行具体说明。

这里,为了便于说明,设第1晶体管16的输出电阻和第2晶体管20的输出电阻分别是Ropt。

此外,设第1输出电路24的特性阻抗和第2输出电路27的特性阻抗分别是Ropt。

此外,设从合成点32观察负载34时的阻抗是0.5×Ropt。

在第1多赫蒂动作模式下,第1信号的频率和第2信号的频率分别是第1频率f

下面,对第1频率f

图4是示出第1多赫蒂动作模式时的第1信号和第2信号的说明图。

图4A示出从第1输入信号源12输出的第1信号的振幅和从第2输入信号源13输出的第2信号的振幅。

图4B示出从第1输入信号源12输出的第1信号的相位和从第2输入信号源13输出的第2信号的相位。

图4C示出从第1输入信号源12输出的第1信号的相位与从第2输入信号源13输出的第2信号的相位的相位差。相位差是从第1输入信号源12输出的第1信号的相位减去从第2输入信号源13输出的第2信号的相位而得到的值。

图4A、图4B和图4C中的各个横轴示出从合成电路31输出的合成信号的电压。该电压是被归一化的电压。

[第1多赫蒂动作模式下的多赫蒂放大器1的饱和输出时动作]

对第1多赫蒂动作模式下的多赫蒂放大器1的饱和输出时动作进行说明。

第1输入信号源12将第1晶体管16的输出功率成为饱和功率的信号作为第1信号输出到第1输入匹配电路14。

具体而言,如图4A和图4B所示,第1输入信号源12将具有从合成电路31输出的合成信号的电压成为“1”的振幅且具有大约90度的相位的第1信号输出到第1输入匹配电路14。

第2输入信号源13将第2晶体管20的输出功率成为饱和功率的信号作为第2信号输出到第2输入匹配电路15。

具体而言,如图4A和图4B所示,第2输入信号源13将具有从合成电路31输出的合成信号的电压成为“1”的振幅且具有大约0度的相位的第2信号输出到第2输入匹配电路15。

第1输入匹配电路14在从第1输入信号源12接受第1信号后,将第1输入信号源12的阻抗转换成第1晶体管16的输入阻抗,将第1信号输出到第1晶体管16的输入端子16a。

第2输入匹配电路15在从第2输入信号源13接受第2信号后,将第2输入信号源13的阻抗转换成第2晶体管20的输入阻抗,将第2信号输出到第2晶体管20的输入端子20a。

第1晶体管16在从第1输入匹配电路14接受第1信号后,对第1信号进行放大,将放大后的第1信号输出到第1输出电路24。

第1输出电路24传输从第1晶体管16输出的第1信号,将第1信号输出到合成电路31。

第2晶体管20在从第2输入匹配电路15接受第2信号后,对第2信号进行放大,将放大后的第2信号输出到第2输出电路27。

第2输出电路27传输从第2晶体管20输出的第2信号,将第2信号输出到合成电路31。

在饱和输出时动作中,第1晶体管16和第2晶体管20双方进行信号的放大动作,从第1输入信号源12输出的第1信号的相位比从第2输入信号源13输出的第2信号的相位超前90度。此外,第2输出电路27的电长度比第1输出电路24的电长度长90度。

因此,从第1输出电路24向合成电路31输出的第1信号的相位和从第2输出电路27向合成电路31输出的第2信号的相位成为同相。

合成电路31对从第1输出电路24输出的第1信号和从第2输出电路27输出的第2信号进行同相合成。

合成电路31将第1信号与第2信号的合成信号输出到输出匹配电路33。

输出匹配电路33在从合成电路31接受合成信号后,将合成点32的阻抗转换成外部的负载34的阻抗,将合成信号输出到负载34。

在饱和输出时动作中,从第1输出电路24输出的第1信号和从第2输出电路27输出的第2信号在合成点32成为相同振幅,通过合成电路31对第1信号和第2信号进行同相合成。此时,第1晶体管16的输出负载和第2晶体管20的输出负载成为分摊合成点32的阻抗的形式。

因此,从第1输出电路24观察合成点32时的阻抗和从第2输出电路27观察合成点32时的阻抗均成为Ropt。

此时,第1输出电路24的特性阻抗和从第1输出电路24观察合成点32时的阻抗一致为Ropt,因此,第1输出电路24不根据Ropt对从第1晶体管16的电流源18观察合成点32时的阻抗进行调制。

此外,第2输出电路27的特性阻抗和从第2输出电路27观察合成点32时的阻抗一致为Ropt,因此,第2输出电路27不根据Ropt对从第2晶体管20的电流源22观察合成点32时的阻抗进行调制。

从第1晶体管16的电流源18观察时的阻抗和从第2晶体管20的电流源22观察时的阻抗均成为Ropt,从多赫蒂放大器1得到饱和功率。

[第1多赫蒂动作模式下的多赫蒂放大器1的回退时动作]

接着,对第1多赫蒂动作模式下的多赫蒂放大器1的回退时动作进行说明。

图5是示出第1多赫蒂动作模式下的多赫蒂放大器1的回退时动作的说明图。

图6是示出第1多赫蒂动作模式下的多赫蒂放大器1的回退时动作中的负载变化的说明图。

在回退时动作中,仅第1晶体管16进行信号的放大动作,第2晶体管20停止信号的放大动作。

第1输入信号源12将第1晶体管16的输出功率成为饱和功率的大约一半的功率的信号作为第1信号输出到第1输入匹配电路14。

具体而言,如图4A和图4B所示,第1输入信号源12将具有从合成电路31输出的合成信号的电压成为“0.5”的振幅且具有大约90度的相位的第1信号输出到第1输入匹配电路14。

从合成电路31输出的合成信号的电压成为“0.5”的第1信号的振幅大于零且小于振幅的最大值。

第2输入信号源13将第2晶体管20的输出功率成为零的信号作为第2信号输出到第2输入匹配电路15。

具体而言,如图4A和图4B所示,第2输入信号源13将具有从合成电路31输出的合成信号的电压成为“0.5”的振幅且具有大约0度的相位的第2信号输出到第2输入匹配电路15。

从合成电路31输出的合成信号的电压成为“0.5”的第2信号的振幅为零。

第1输入匹配电路14在从第1输入信号源12接受第1信号后,将第1输入信号源12的阻抗转换成第1晶体管16的输入阻抗,将第1信号输出到第1晶体管16的输入端子16a。

第1晶体管16在从第1输入匹配电路14接受第1信号后,对第1信号进行放大,将放大后的第1信号输出到第1输出电路24。

第1输出电路24传输从第1晶体管16输出的第1信号,将第1信号输出到合成电路31。

第2输入匹配电路15在从第2输入信号源13接受第2信号后,将第2输入信号源13的阻抗转换成第2晶体管20的输入阻抗,将第2信号输出到第2晶体管20的输入端子20a。

第2晶体管20即使从第2输入匹配电路15接受第2信号,由于第2信号的振幅为零,因此,第2晶体管20也停止而不进行信号的放大动作。

第2晶体管20停止,因此,如图5所示,第2晶体管20的电流源22成为开路的状态。

在回退时动作中,由于第2输出电路27的电长度为180度,因此,从合成点32观察第2晶体管20时的阻抗成为无限大。

从合成点32观察第2晶体管20时的阻抗无限大,因此,从第1输出电路24观察合成电路31时的阻抗成为0.5×Ropt。

第1输出电路24自身的特性阻抗为Ropt,从第1输出电路24观察合成电路31时的阻抗为0.5×Ropt,因此,如图6所示,将从第1晶体管16的电流源18观察合成点32时的阻抗从Ropt调制成2×Ropt。

第1输出电路24将从第1晶体管16的电流源18观察合成点32时的阻抗从Ropt调制成2×Ropt,由此,在第1晶体管16的输出功率比饱和功率低时,成为在第1晶体管16连接有高电阻的负载的状态。即,在第1晶体管16的输出功率比饱和功率低时,第1晶体管16的负载电阻成为比Ropt大的2×Ropt。

第1晶体管16成为连接有高电阻的负载的状态,因此,能够进行高效的放大动作。

接着,对以第1异相动作模式进行动作的多赫蒂放大器1进行说明。

如图2所示,第1异相动作模式是第1信号的频率和第2信号的频率分别是比第1频率f

图7是示出第1异相动作模式时的第1信号和第2信号的说明图。

图7A示出从第1输入信号源12输出的第1信号的振幅和从第2输入信号源13输出的第2信号的振幅。

图7B示出从第1输入信号源12输出的第1信号的相位和从第2输入信号源13输出的第2信号的相位。

图7C示出从第1输入信号源12输出的第1信号的相位与从第2输入信号源13输出的第2信号的相位的相位差。相位差是从第1输入信号源12输出的第1信号的相位减去从第2输入信号源13输出的第2信号的相位而得到的值。

图7A、图7B和图7C中的各个横轴示出从合成电路31输出的合成信号的电流。该电流是被归一化的电流。

在第1异相动作模式下,如图7A所示,从第1输入信号源12输出的第1信号的振幅和从第2输入信号源13输出的第2信号的振幅分别伴随着从合成电路31输出的合成信号的电流增加而单调递增。

从第1输入信号源12输出的第1信号的振幅是与从第2输入信号源13输出的第2信号的振幅相同的值。

第1晶体管16的输出功率在第1信号的振幅最大时成为饱和功率,第2晶体管20的输出功率在第2信号的振幅最大时成为饱和功率。

从第1输入信号源12输出的第1信号的相位伴随着从合成电路31输出的合成信号的电流增加而单调递减。

从第2输入信号源13输出的第2信号的相位伴随着从合成电路31输出的合成信号的电流增加而单调递增。

第1信号的相位和第2信号的相位的绝对值相等,第1信号的相位和第2信号的相位的符号彼此不同。第1信号的相位的符号是正符号,第2信号的相位的符号是负符号。

因此,从合成电路31输出的合成信号的电流越大,则从第1输入信号源12输出的第1信号的相位与从第2输入信号源13输出的第2信号的相位的相位差越小。

例如,如果从合成电路31输出的合成信号的电流为“0”,则相位差为240度,如果从合成电路31输出的合成信号的电流为“1”,则相位差为60度。

第1异相动作模式包含饱和输出时动作和回退时动作。

在第1异相动作模式中包含的回退时动作中,第2晶体管20不停止,第1晶体管16和第2晶体管20双方进行信号的放大动作。

在第1异相动作模式下,第1信号的频率和第2信号的频率分别是第2频率f

下面,对第2频率f

[第1异相动作模式下的多赫蒂放大器1的饱和输出时动作]

对第1异相动作模式下的多赫蒂放大器1的饱和输出时动作进行说明。

第1输入信号源12将第1晶体管16的输出功率成为饱和功率的信号作为第1信号输出到第1输入匹配电路14。

具体而言,如图7A和图7B所示,第1输入信号源12将具有从合成电路31输出的合成信号的电流成为“1”的振幅且具有大约30度的相位的第1信号输出到第1输入匹配电路14。

第2输入信号源13将第2晶体管20的输出功率成为饱和功率的信号作为第2信号输出到第2输入匹配电路15。

具体而言,如图7A和图7B所示,第2输入信号源13将具有从合成电路31输出的合成信号的电流成为“1”的振幅且具有大约-30度的相位的第2信号输出到第2输入匹配电路15。

第1输入匹配电路14在从第1输入信号源12接受第1信号后,将第1输入信号源12的阻抗转换成第1晶体管16的输入阻抗,将第1信号输出到第1晶体管16的输入端子16a。

第2输入匹配电路15在从第2输入信号源13接受第2信号后,将第2输入信号源13的阻抗转换成第2晶体管20的输入阻抗,将第2信号输出到第2晶体管20的输入端子20a。

第1晶体管16在从第1输入匹配电路14接受第1信号后,对第1信号进行放大,将放大后的第1信号输出到第1输出电路24。

第1输出电路24传输从第1晶体管16输出的第1信号,将第1信号输出到合成电路31。

第2晶体管20在从第2输入匹配电路15接受第2信号后,对第2信号进行放大,将放大后的第2信号输出到第2输出电路27。

第2输出电路27传输从第2晶体管20输出的第2信号,将第2信号输出到合成电路31。

在饱和输出时动作中,第1晶体管16和第2晶体管20双方进行信号的放大动作,从第1输入信号源12输出的第1信号的相位比从第2输入信号源13输出的第2信号的相位超前60度。此外,第2输出电路27的电长度比第1输出电路24的电长度长60度。

因此,从第1输出电路24向合成电路31输出的第1信号的相位和从第2输出电路27向合成电路31输出的第2信号的相位成为同相。

合成电路31对从第1输出电路24输出的第1信号和从第2输出电路27输出的第2信号进行同相合成。

合成电路31将第1信号与第2信号的合成信号输出到输出匹配电路33。

输出匹配电路33在从合成电路31接受合成信号后,将合成点32的阻抗转换成外部的负载34的阻抗,将合成信号输出到负载34。

在饱和输出时动作中,从第1输出电路24输出的第1信号和从第2输出电路27输出的第2信号在合成点32成为相同振幅,通过合成电路31对第1信号和第2信号进行同相合成。此时,第1晶体管16的输出负载和第2晶体管20的输出负载成为分摊合成点32的阻抗的形式。

因此,从第1输出电路24观察合成点32时的阻抗和从第2输出电路27观察合成点32时的阻抗均成为Ropt。

此时,第1输出电路24的特性阻抗和从第1输出电路24观察合成点32时的阻抗一致为Ropt,因此,第1输出电路24不根据Ropt对从第1晶体管16的电流源18观察合成点32时的阻抗进行调制。

此外,第2输出电路27的特性阻抗和从第2输出电路27观察合成点32时的阻抗一致为Ropt,因此,第2输出电路27不根据Ropt对从第2晶体管20的电流源22观察合成点32时的阻抗进行调制。

从第1晶体管16的电流源18观察时的阻抗和从第2晶体管20的电流源22观察时的阻抗均成为Ropt,从多赫蒂放大器1得到饱和功率。

[第1异相动作模式下的多赫蒂放大器1的回退时动作]

对第1异相动作模式下的多赫蒂放大器1的回退时动作进行说明。

图8是示出第1异相动作模式下的多赫蒂放大器1的回退时动作的说明图。

图9是示出第1异相动作模式下的多赫蒂放大器1的回退时动作中的负载变化的说明图。

这里,作为回退时动作的动作,例如,对第1晶体管16和第2晶体管20各自的输出功率成为饱和功率的大约三分之一时的动作进行说明。

第1输入信号源12将第1晶体管16的输出功率成为饱和功率的大约三分之一的信号作为第1信号输出到第1输入匹配电路14。

具体而言,第1输入信号源12将具有与第1晶体管16的输出功率成为饱和功率时的大约30度的相位相比相差+30度的大约60度的相位的第1信号输出到第1输入匹配电路14。此时的第1信号的振幅对应于与具有大约60度的相位的第1信号对应的合成信号的电流。

第2输入信号源13将第2晶体管20的输出功率成为饱和功率的大约三分之一的信号作为第2信号输出到第2输入匹配电路15。

具体而言,第2输入信号源13将具有与第2晶体管20的输出功率成为饱和功率时的大约-30度的相位相比相差-30度的大约-60度的相位的第2信号输出到第2输入匹配电路15。此时的第2信号的振幅对应于与具有大约-60度的相位的第2信号对应的合成信号的电流。

从第1输入信号源12输出的第1信号的相位与从第2输入信号源13输出的第2信号的相位的相位差为120度。

第1输入匹配电路14在从第1输入信号源12接受第1信号后,将第1输入信号源12的阻抗转换成第1晶体管16的输入阻抗,将第1信号输出到第1晶体管16的输入端子16a。

第2输入匹配电路15在从第2输入信号源13接受第2信号后,将第2输入信号源13的阻抗转换成第2晶体管20的输入阻抗,将第2信号输出到第2晶体管20的输入端子20a。

第1晶体管16在从第1输入匹配电路14接受第1信号后,对第1信号进行放大,将放大后的第1信号输出到第1输出电路24。

第1输出电路24传输从第1晶体管16输出的第1信号,将第1信号输出到合成电路31。

第2晶体管20在从第2输入匹配电路15接受第2信号后,对第2信号进行放大,将放大后的第2信号输出到第2输出电路27。

第2输出电路27传输从第2晶体管20输出的第2信号,将第2信号输出到合成电路31。

在第1异相动作模式中包含的回退时动作中,第1晶体管16的输出负载和第2晶体管20的输出负载成为分摊合成点32的阻抗的形式。

因此,从第1输出电路24观察合成点32时的阻抗和从第2输出电路27观察合成点32时的阻抗均成为Ropt。

此外,从第1输出电路24输出的第1信号的相位是与饱和输出时动作中的相位相比相差+30度的大约60度的相位,因此,从第1输出电路24观察合成点32时的阻抗Ropt变成感性区域。在图9中,从合成点32观察第2晶体管20时的阻抗变成X点。

第1输出电路24自身的特性阻抗为Ropt,第1输出电路24的电长度为大约60度。

因此,如图9所示,第1输出电路24根据大约60度的电长度将从第1晶体管16的电流源18观察合成点32时的阻抗从X点调制成3×Ropt。

此外,从第2输出电路27输出的第2信号的相位是与饱和输出时动作中的相位相比相差-30度的大约-60度的相位,因此,从第2输出电路27观察合成点32时的阻抗Ropt变成容性区域。在图9中,从合成点32观察第2晶体管20时的阻抗变成Y点。

第2输出电路27自身的特性阻抗为Ropt,第2输出电路27的电长度为大约120度。

因此,如图9所示,第2输出电路27根据大约120度的电长度将从第2晶体管20的电流源22观察合成点32时的阻抗从Y点调制成3×Ropt。

第1输出电路24将从第1晶体管16的电流源18观察合成点32时的阻抗调制成3×Ropt,由此,在第1晶体管16的输出功率比饱和功率低时,成为在第1晶体管16连接有高电阻的负载的状态。即,在第1晶体管16的输出功率比饱和功率低时,第1晶体管16的负载电阻成为比Ropt大的3×Ropt。

第1晶体管16成为连接有高电阻的负载的状态,因此,能够进行高效的放大动作。

第2输出电路27将从第2晶体管20的电流源22观察合成点32时的阻抗调制成3×Ropt,由此,在第2晶体管20的输出功率比饱和功率低时,成为在第2晶体管20连接有高电阻的负载的状态。即,在第2晶体管20的输出功率比饱和功率低时,第2晶体管20的负载电阻成为比Ropt大的3×Ropt。

第2晶体管20成为连接有高电阻的负载的状态,因此,能够进行高效的放大动作。

在以上的实施方式1中,以如下方式构成多赫蒂放大器1:根据频率对以同相方式合成由第1晶体管16放大的第1信号和由第2晶体管20放大的第2信号的信号模式、以及以异相方式合成由第1晶体管16放大的第1信号和由第2晶体管20放大的第2信号的信号模式进行切换,动作模式根据切换后的信号模式而被切换成多赫蒂动作模式或异相动作模式。因此,即使由第1晶体管16放大的第1信号的频率和由第2晶体管20放大的第2信号的频率变化,多赫蒂放大器1也能够使回退时的效率特性宽带化。

实施方式2

在实施方式2中,对以第2异相动作模式进行动作的多赫蒂放大器1进行说明。

实施方式2的多赫蒂放大器1的结构与实施方式1的多赫蒂放大器1的结构相同,示出实施方式2的多赫蒂放大器1的结构图是图3。

如图2所示,第2异相动作模式是第1信号的频率和第2信号的频率分别是比第1频率f

图10是示出第2异相动作模式时的第1信号和第2信号的说明图。

图10A示出从第1输入信号源12输出的第1信号的振幅和从第2输入信号源13输出的第2信号的振幅。

图10B示出从第1输入信号源12输出的第1信号的相位和从第2输入信号源13输出的第2信号的相位。

图10C示出从第1输入信号源12输出的第1信号的相位与从第2输入信号源13输出的第2信号的相位的相位差。相位差是从第1输入信号源12输出的第1信号的相位减去从第2输入信号源13输出的第2信号的相位而得到的值。

图10A、图10B和图10C中的各个横轴示出从合成电路31输出的合成信号的电流。该电流是被归一化的电流。

在第2异相动作模式下,如图10A所示,从第1输入信号源12输出的第1信号的振幅和从第2输入信号源13输出的第2信号的振幅分别伴随着从合成电路31输出的合成信号的电流增加而单调递增。

从第1输入信号源12输出的第1信号的振幅是与从第2输入信号源13输出的第2信号的振幅相同的值。

第1晶体管16的输出功率在第1信号的振幅最大时成为饱和功率,第2晶体管20的输出功率在第2信号的振幅最大时成为饱和功率。

从第1输入信号源12输出的第1信号的相位伴随着从合成电路31输出的合成信号的电流增加而单调递减。

从第2输入信号源13输出的第2信号的相位伴随着从合成电路31输出的合成信号的电流增加而单调递增。

第1信号的相位和第2信号的相位的绝对值相等,第1信号的相位和第2信号的相位的符号彼此不同。

例如,如果从合成电路31输出的合成信号的电流为“0”,则相位差为60度,如果从合成电路31输出的合成信号的电流为“1”,则相位差为120度。

在实施方式2的多赫蒂放大器1中,设第1晶体管16和第2晶体管20各自的输出电阻是Ropt,从合成点32观察负载34时的阻抗是0.5×Ropt。

第2异相动作模式包含饱和输出时动作和回退时动作。

在第2异相动作模式中包含的回退时动作中,第2晶体管20不停止,第1晶体管16和第2晶体管20双方进行信号的放大动作。

在第2异相动作模式下,第1信号的频率和第2信号的频率分别是第3频率f

下面,对第3频率f

[第2异相动作模式下的多赫蒂放大器1的饱和输出时动作]

对第2异相动作模式下的多赫蒂放大器1的饱和输出时动作进行说明。

第1输入信号源12将第1晶体管16的输出功率成为饱和功率的信号作为第1信号输出到第1输入匹配电路14。

具体而言,如图10A和图10B所示,第1输入信号源12将具有从合成电路31输出的信号的电流成为“1”的振幅且具有大约60度的相位的第1信号输出到第1输入匹配电路14。

第2输入信号源13将第2晶体管20的输出功率成为饱和功率的信号作为第2信号输出到第2输入匹配电路15。

具体而言,如图10A和图10B所示,第2输入信号源13将具有从合成电路31输出的信号的电流成为“1”的振幅且具有大约-60度的相位的第2信号输出到第2输入匹配电路15。

第1输入匹配电路14在从第1输入信号源12接受第1信号后,将第1输入信号源12的阻抗转换成第1晶体管16的输入阻抗,将第1信号输出到第1晶体管16的输入端子16a。

第2输入匹配电路15在从第2输入信号源13接受第2信号后,将第2输入信号源13的阻抗转换成第2晶体管20的输入阻抗,将第2信号输出到第2晶体管20的输入端子20a。

第1晶体管16在从第1输入匹配电路14接受第1信号后,对第1信号进行放大,将放大后的第1信号输出到第1输出电路24。

第1输出电路24传输从第1晶体管16输出的第1信号,将第1信号输出到合成电路31。

第2晶体管20在从第2输入匹配电路15接受第2信号后,对第2信号进行放大,将放大后的第2信号输出到第2输出电路27。

第2输出电路27传输从第2晶体管20输出的第2信号,将第2信号输出到合成电路31。

在饱和输出时动作中,第1晶体管16和第2晶体管20双方进行信号的放大动作,从第1输入信号源12输出的第1信号的相位比从第2输入信号源13输出的第2信号的相位超前120度。此外,第2输出电路27的电长度比第1输出电路24的电长度长120度。

因此,从第1输出电路24向合成电路31输出的第1信号的相位和从第2输出电路27向合成电路31输出的第2信号的相位成为同相。

合成电路31对从第1输出电路24输出的第1信号和从第2输出电路27输出的第2信号进行同相合成。

合成电路31将第1信号与第2信号的合成信号输出到输出匹配电路33。

输出匹配电路33在从合成电路31接受合成信号后,将合成点32的阻抗转换成外部的负载34的阻抗,将合成信号输出到负载34。

在饱和输出时动作中,从第1输出电路24输出的第1信号和从第2输出电路27输出的第2信号在合成点32成为相同振幅,通过合成电路31对第1信号和第2信号进行同相合成。此时,第1晶体管16的输出负载和第2晶体管20的输出负载成为分摊合成点32的阻抗的形式。

因此,从第1输出电路24观察合成点32时的阻抗和从第2输出电路27观察合成点32时的阻抗均成为Ropt。

此时,第1输出电路24的特性阻抗和从第1输出电路24观察合成点32时的阻抗一致为Ropt,因此,第1输出电路24不根据Ropt对从第1晶体管16的电流源18观察合成点32时的阻抗进行调制。

此外,第2输出电路27的特性阻抗和从第2输出电路27观察合成点32时的阻抗一致为Ropt,因此,第2输出电路27不根据Ropt对从第2晶体管20的电流源22观察合成点32时的阻抗进行调制。

从第1晶体管16的电流源18观察时的阻抗和从第2晶体管20的电流源22观察时的阻抗均成为Ropt,从多赫蒂放大器1得到饱和功率。

[第2异相动作模式下的多赫蒂放大器1的回退时动作]

对第2异相动作模式下的多赫蒂放大器1的回退时动作进行说明。

图11是示出第2异相动作模式下的多赫蒂放大器1的回退时动作的说明图。

这里,作为回退时动作的动作,例如,对第1晶体管16和第2晶体管20各自的输出功率成为饱和功率的大约三分之一时的动作进行说明。

第1输入信号源12将第1晶体管16的输出功率成为饱和功率的大约三分之一的信号作为第1信号输出到第1输入匹配电路14。

具体而言,第1输入信号源12将具有与第1晶体管16的输出功率成为饱和功率时的大约60度的相位相比相差-30度的大约30度的相位的第1信号输出到第1输入匹配电路14。此时的第1信号的振幅对应于与具有大约30度的相位的第1信号对应的合成信号的电流。

第2输入信号源13将第2晶体管20的输出功率成为饱和功率的大约三分之一的信号作为第2信号输出到第2输入匹配电路15。

具体而言,第2输入信号源13将具有与第2晶体管20的输出功率成为饱和功率时的大约-60度的相位相比相差+30度的大约-30度的相位的第2信号输出到第2输入匹配电路15。此时的第2信号的振幅对应于与具有大约-30度的相位的第2信号对应的合成信号的电流。

从第1输入信号源12输出的第1信号的相位与从第2输入信号源13输出的第2信号的相位的相位差为120度。

第1输入匹配电路14在从第1输入信号源12接受第1信号后,将第1输入信号源12的阻抗转换成第1晶体管16的输入阻抗,将第1信号输出到第1晶体管16的输入端子16a。

第2输入匹配电路15在从第2输入信号源13接受第2信号后,将第2输入信号源13的阻抗转换成第2晶体管20的输入阻抗,将第2信号输出到第2晶体管20的输入端子20a。

第1晶体管16在从第1输入匹配电路14接受第1信号后,对第1信号进行放大,将放大后的第1信号输出到第1输出电路24。

第1输出电路24传输从第1晶体管16输出的第1信号,将第1信号输出到合成电路31。

第2晶体管20在从第2输入匹配电路15接受第2信号后,对第2信号进行放大,将放大后的第2信号输出到第2输出电路27。

第2输出电路27传输从第2晶体管20输出的第2信号,将第2信号输出到合成电路31。

在第2异相动作模式中包含的回退时动作中,第1晶体管16的输出负载和第2晶体管20的输出负载成为分摊合成点32的阻抗的形式。

因此,从第1输出电路24观察合成点32时的阻抗和从第2输出电路27观察合成点32时的阻抗均成为Ropt。

此外,从第1输出电路24输出的第1信号的相位是与饱和输出时动作中的相位相比相差-30度的大约30度的相位,因此,从第1输出电路24观察合成点32时的阻抗即Ropt变成感性区域。

第1输出电路24自身的特性阻抗为Ropt,第1输出电路24的电长度为大约120度。

因此,第1输出电路24根据大约120度的电长度将从第1晶体管16的电流源18观察合成点32时的阻抗调制成3×Ropt。

此外,从第2输出电路27输出的第2信号的相位是与饱和输出时动作中的相位相比相差+30度的大约-30度的相位,因此,从第2输出电路27观察合成点32时的阻抗即Ropt变成容性区域。

第2输出电路27自身的特性阻抗为Ropt,第2输出电路27的电长度为大约240度。

因此,第2输出电路27根据大约240度的电长度将从第2晶体管20的电流源22观察合成点32时的阻抗调制成3×Ropt。

第1输出电路24将从第1晶体管16的电流源18观察合成点32时的阻抗调制成3×Ropt,由此,在第1晶体管16的输出功率比饱和功率低时,成为在第1晶体管16连接有高电阻的负载的状态。即,在第1晶体管16的输出功率比饱和功率低时,第1晶体管16的负载电阻成为比Ropt大的3×Ropt。

第1晶体管16成为连接有高电阻的负载的状态,因此,能够进行高效的放大动作。

第2输出电路27将从第2晶体管20的电流源22观察合成点32时的阻抗调制成3×Ropt,由此,在第2晶体管20的输出功率比饱和功率低时,成为在第2晶体管20连接有高电阻的负载的状态。即,在第2输出电路27的输出功率比饱和功率低时,第2输出电路27的负载电阻成为比Ropt大的3×Ropt。

第2晶体管20成为连接有高电阻的负载的状态,因此,能够进行高效的放大动作。

如上所述,在以第2异相动作模式进行动作的多赫蒂放大器1中,与以第1多赫蒂动作模式进行动作的多赫蒂放大器1同样,也能够使回退时的效率特性宽带化。

实施方式3

在实施方式3中,对以第2多赫蒂动作模式进行动作的多赫蒂放大器1进行说明。

实施方式3的多赫蒂放大器1的结构与实施方式1的多赫蒂放大器1的结构相同,示出实施方式3的多赫蒂放大器1的结构图是图3。

如图2所示,第2多赫蒂动作模式是第1信号的频率和第2信号的频率分别是比第2频率f

图12是示出第2多赫蒂动作模式时的第1信号和第2信号的说明图。

图12A示出从第1输入信号源12输出的第1信号的振幅和从第2输入信号源13输出的第2信号的振幅。

图12B示出从第1输入信号源12输出的第1信号的相位和从第2输入信号源13输出的第2信号的相位。

图12C示出从第1输入信号源12输出的第1信号的相位与从第2输入信号源13输出的第2信号的相位的相位差。相位差是从第1输入信号源12输出的第1信号的相位减去从第2输入信号源13输出的第2信号的相位而得到的值。

图12A、图12B和图12C中的各个横轴示出从合成电路31输出的合成信号的电压。该电压是被归一化的电压。

在第2多赫蒂动作模式下,如图12A所示,从第1输入信号源12输出的第1信号的振幅和从第2输入信号源13输出的第2信号的振幅分别伴随着从合成电路31输出的合成信号的电压增加而单调递增。第1信号的振幅为零时的第2信号的振幅大于零。

第1晶体管16的输出功率在第1信号的振幅最大时成为饱和功率,第2晶体管20的输出功率在第2信号的振幅最大时成为饱和功率。

如图12B所示,从第1输入信号源12输出的第1信号的相位大约为45度,从第2输入信号源13输出的第2信号的相位大约为0度,第1信号的相位比第2信号的相位超前大约45度。

在实施方式3的多赫蒂放大器1中,设第1晶体管16和第2晶体管20各自的输出电阻是Ropt,从合成点32观察负载34时的阻抗是0.5×Ropt。

第2多赫蒂动作模式包含饱和输出时动作和回退时动作。

在第2多赫蒂动作模式中包含的回退时动作中,第1晶体管16停止,仅第2晶体管20进行信号的放大动作。

第1信号的频率和第2信号的频率分别是第4频率f

下面,对第4频率f

[第2多赫蒂动作模式下的多赫蒂放大器1的饱和输出时动作]

对第2多赫蒂动作模式下的多赫蒂放大器1的饱和输出时动作进行说明。

第1输入信号源12将第1晶体管16的输出功率成为饱和功率的信号作为第1信号输出到第1输入匹配电路14。

具体而言,如图12A和图12B所示,第1输入信号源12将具有从合成电路31输出的信号的电压成为“1”的振幅且具有大约45度的相位的第1信号输出到第1输入匹配电路14。

第2输入信号源13将第2晶体管20的输出功率成为饱和功率的信号作为第2信号输出到第2输入匹配电路15。

具体而言,如图12A和图12B所示,第2输入信号源13将具有从合成电路31输出的信号的电压成为“1”的振幅且具有大约0度的相位的第2信号输出到第2输入匹配电路15。

第1输入匹配电路14在从第1输入信号源12接受第1信号后,将第1输入信号源12的阻抗转换成第1晶体管16的输入阻抗,将第1信号输出到第1晶体管16的输入端子16a。

第2输入匹配电路15在从第2输入信号源13接受第2信号后,将第2输入信号源13的阻抗转换成第2晶体管20的输入阻抗,将第2信号输出到第2晶体管20的输入端子20a。

第1晶体管16在从第1输入匹配电路14接受第1信号后,对第1信号进行放大,将放大后的第1信号输出到第1输出电路24。

第1输出电路24传输从第1晶体管16输出的第1信号,将第1信号输出到合成电路31。

第2晶体管20在从第2输入匹配电路15接受第2信号后,对第2信号进行放大,将放大后的第2信号输出到第2输出电路27。

第2输出电路27传输从第2晶体管20输出的第2信号,将第2信号输出到合成电路31。

在饱和输出时动作中,第1晶体管16和第2晶体管20双方进行信号的放大动作,从第1输入信号源12输出的第1信号的相位比从第2输入信号源13输出的第2信号的相位超前45度。此外,第2输出电路27的电长度比第1输出电路24的电长度长45度。

因此,从第1输出电路24向合成电路31输出的第1信号的相位和从第2输出电路27向合成电路31输出的第2信号的相位成为同相。

合成电路31对从第1输出电路24输出的第1信号和从第2输出电路27输出的第2信号进行同相合成。

合成电路31将第1信号与第2信号的合成信号输出到输出匹配电路33。

输出匹配电路33在从合成电路31接受合成信号后,将合成点32的阻抗转换成外部的负载34的阻抗,将合成信号输出到负载34。

在饱和输出时动作中,从第1输出电路24输出的第1信号和从第2输出电路27输出的第2信号在合成点32成为相同振幅,通过合成电路31对第1信号和第2信号进行同相合成。此时,第1晶体管16的输出负载和第2晶体管20的输出负载成为分摊合成点32的阻抗的形式。

因此,从第1输出电路24观察合成点32时的阻抗和从第2输出电路27观察合成点32时的阻抗均成为Ropt。

此时,第1输出电路24的特性阻抗和从第1输出电路24观察合成点32时的阻抗一致为Ropt,因此,第1输出电路24不根据Ropt对从第1晶体管16的电流源18观察合成点32时的阻抗进行调制。

此外,第2输出电路27的特性阻抗和从第2输出电路27观察合成点32时的阻抗一致为Ropt,因此,第2输出电路27不根据Ropt对从第2晶体管20的电流源22观察合成点32时的阻抗进行调制。

从第1晶体管16的电流源18观察时的阻抗和从第2晶体管20的电流源22观察时的阻抗均成为Ropt,从多赫蒂放大器1得到饱和功率。

[第2多赫蒂动作模式下的多赫蒂放大器1的回退时动作]

对第2多赫蒂动作模式下的多赫蒂放大器1的回退时动作进行说明。

图13是示出第2多赫蒂动作模式下的多赫蒂放大器1的回退时动作的说明图。

在回退时动作中,仅第2晶体管20进行信号的放大动作,第1晶体管16停止信号的放大动作。

第1输入信号源12将第1晶体管16的输出功率成为零的信号作为第1信号输出到第1输入匹配电路14。

具体而言,如图12A和图12B所示,第1输入信号源12将具有从合成电路31输出的信号的电压成为“0.5”的振幅且具有大约45度的相位的第1信号输出到第1输入匹配电路14。

从合成电路31输出的合成信号的电压成为“0.5”的第1信号的振幅为零。

第2输入信号源13将第2晶体管20的输出功率例如成为饱和功率的大约一半的功率的信号作为第2信号输出到第1输入匹配电路14。

具体而言,如图12A和图12B所示,第2输入信号源13将具有从合成电路31输出的信号的电压成为“0.5”的振幅且具有大约0度的相位的第2信号输出到第2输入匹配电路15。

从合成电路31输出的信号的电压成为“0.5”的第2信号的振幅大于零且小于振幅的最大值。

第1输入匹配电路14在从第1输入信号源12接受第1信号后,将第1输入信号源12的阻抗转换成第1晶体管16的输入阻抗,将第1信号输出到第1晶体管16的输入端子16a。

即使从第1输入匹配电路14接受第1信号,第1信号的振幅也为零,因此,第1晶体管16停止而不进行信号的放大动作。

第1晶体管16停止,因此,如图13所示,第1晶体管16的电流源18成为开路的状态。

第2输入匹配电路15在从第2输入信号源13接受第2信号后,将第2输入信号源13的阻抗转换成第2晶体管20的输入阻抗,将第2信号输出到第2晶体管20的输入端子20a。

第2晶体管20在从第2输入匹配电路15接受第2信号后,对第2信号进行放大,将放大后的第2信号输出到第2输出电路27。

第2输出电路27传输从第2晶体管20输出的第2信号,将第2信号输出到合成电路31。

在回退时动作中,从合成点32观察第1晶体管16时的阻抗无限大,因此,从第2输出电路27观察合成电路31时的阻抗成为0.5×Ropt。

第2输出电路27自身的特性阻抗为Ropt,从第2输出电路27观察合成电路31时的阻抗为0.5×Ropt,因此,将从第2晶体管20的电流源22观察合成点32时的阻抗从Ropt调制成2×Ropt。

第2输出电路27将从第2晶体管20的电流源22观察合成点32时的阻抗从Ropt调制成2×Ropt,由此,在第2晶体管20的输出功率比饱和功率低时,成为在第2晶体管20连接有高电阻的负载的状态。即,在第2输出电路27的输出功率比饱和功率低时,第2输出电路27的负载电阻成为比Ropt大的2×Ropt。

第2晶体管20成为连接有高电阻的负载的状态,因此,能够进行高效的放大动作。

如上所述,在以第2多赫蒂动作模式进行动作的多赫蒂放大器1中,与以第1多赫蒂动作模式进行动作的多赫蒂放大器1同样,也能够使回退时的效率特性宽带化。

实施方式4

在实施方式4中,对以第3多赫蒂动作模式进行动作的多赫蒂放大器1进行说明。

实施方式4的多赫蒂放大器1的结构与实施方式1的多赫蒂放大器1的结构相同,示出实施方式4的多赫蒂放大器1的结构图是图3。

如图2所示,第3多赫蒂动作模式是第1信号的频率和第2信号的频率分别是比第3频率f

图14是示出第3多赫蒂动作模式时的第1信号和第2信号的说明图。

图14A示出从第1输入信号源12输出的第1信号的振幅和从第2输入信号源13输出的第2信号的振幅。

图14B示出从第1输入信号源12输出的第1信号的相位和从第2输入信号源13输出的第2信号的相位。

图14C示出从第1输入信号源12输出的第1信号的相位与从第2输入信号源13输出的第2信号的相位的相位差。相位差是从第1输入信号源12输出的第1信号的相位减去从第2输入信号源13输出的第2信号的相位而得到的值。

图14A、图14B和图14C中的各个横轴示出从合成电路31输出的合成信号的电压。该电压是被归一化的电压。

在第3多赫蒂动作模式下,如图14A所示,从第1输入信号源12输出的第1信号的振幅和从第2输入信号源13输出的第2信号的振幅分别伴随着从合成电路31输出的合成信号的电压增加而单调递增。第1信号的振幅为零时的第2信号的振幅大于零。

第1晶体管16的输出功率在第1信号的振幅最大时成为饱和功率,第2晶体管20的输出功率在第2信号的振幅最大时成为饱和功率。

如图14B所示,从第1输入信号源12输出的第1信号的相位大约为135度,从第2输入信号源13输出的第2信号的相位大约为0度,第1信号的相位比第2信号的相位超前大约135度。

在实施方式4的多赫蒂放大器1中,设第1晶体管16和第2晶体管20各自的输出电阻是Ropt,从合成点32观察负载34时的阻抗是0.5×Ropt。

第3多赫蒂动作模式包含饱和输出时动作和回退时动作。

在第3多赫蒂动作模式中包含的回退时动作中,第1晶体管16停止,仅第2晶体管20进行信号的放大动作。

第1信号的频率和第2信号的频率分别是第5频率f

下面,对第5频率f

[第3多赫蒂动作模式下的多赫蒂放大器1的饱和输出时动作]

对第3多赫蒂动作模式下的多赫蒂放大器1的饱和输出时动作进行说明。

第1输入信号源12将第1晶体管16的输出功率成为饱和功率的信号作为第1信号输出到第1输入匹配电路14。

具体而言,如图14A和图14B所示,第1输入信号源12将具有从合成电路31输出的合成信号的电压成为“1”的振幅且具有大约135度的相位的第1信号输出到第1输入匹配电路14。

第2输入信号源13将第2晶体管20的输出功率成为饱和功率的信号作为第2信号输出到第2输入匹配电路15。

具体而言,如图14A和图14B所示,第2输入信号源13将具有从合成电路31输出的合成信号的电压成为“1”的振幅且具有大约0度的相位的第2信号输出到第2输入匹配电路15。

第1输入匹配电路14在从第1输入信号源12接受第1信号后,将第1输入信号源12的阻抗转换成第1晶体管16的输入阻抗,将第1信号输出到第1晶体管16的输入端子16a。

第2输入匹配电路15在从第2输入信号源13接受第2信号后,将第2输入信号源13的阻抗转换成第2晶体管20的输入阻抗,将第2信号输出到第2晶体管20的输入端子20a。

第1晶体管16在从第1输入匹配电路14接受第1信号后,对第1信号进行放大,将放大后的第1信号输出到第1输出电路24。

第1输出电路24传输从第1晶体管16输出的第1信号,将第1信号输出到合成电路31。

第2晶体管20在从第2输入匹配电路15接受第2信号后,对第2信号进行放大,将放大后的第2信号输出到第2输出电路27。

第2输出电路27传输从第2晶体管20输出的第2信号,将第2信号输出到合成电路31。

在饱和输出时动作中,第1晶体管16和第2晶体管20双方进行信号的放大动作,从第1输入信号源12输出的第1信号的相位比从第2输入信号源13输出的第2信号的相位超前135度。此外,第2输出电路27的电长度比第1输出电路24的电长度长135度。

因此,从第1输出电路24向合成电路31输出的第1信号的相位和从第2输出电路27向合成电路31输出的第2信号的相位成为同相。

合成电路31对从第1输出电路24输出的第1信号和从第2输出电路27输出的第2信号进行同相合成。

合成电路31将第1信号与第2信号的合成信号输出到输出匹配电路33。

输出匹配电路33在从合成电路31接受合成信号后,将合成点32的阻抗转换成外部的负载34的阻抗,将合成信号输出到负载34。

在饱和输出时动作中,从第1输出电路24输出的第1信号和从第2输出电路27输出的第2信号在合成点32成为相同振幅,通过合成电路31对第1信号和第2信号进行同相合成。此时,第1晶体管16的输出负载和第2晶体管20的输出负载成为分摊合成点32的阻抗的形式。

因此,从第1输出电路24观察合成点32时的阻抗和从第2输出电路27观察合成点32时的阻抗均成为Ropt。

此时,第1输出电路24的特性阻抗和从第1输出电路24观察合成点32时的阻抗一致为Ropt,因此,第1输出电路24不根据Ropt对从第1晶体管16的电流源18观察合成点32时的阻抗进行调制。

此外,第2输出电路27的特性阻抗和从第2输出电路27观察合成点32时的阻抗一致为Ropt,因此,第2输出电路27不根据Ropt对从第2晶体管20的电流源22观察合成点32时的阻抗进行调制。

从第1晶体管16的电流源18观察时的阻抗和从第2晶体管20的电流源22观察时的阻抗均成为Ropt,从多赫蒂放大器1得到饱和功率。

[第3多赫蒂动作模式下的多赫蒂放大器1的回退时动作]

对第3多赫蒂动作模式下的多赫蒂放大器1的回退时动作进行说明。

图15是示出第3多赫蒂动作模式下的多赫蒂放大器1的回退时动作的说明图。

在回退时动作中,仅第2晶体管20进行信号的放大动作,第1晶体管16停止信号的放大动作。

第1输入信号源12将第1晶体管16的输出功率成为零的信号作为第1信号输出到第1输入匹配电路14。

具体而言,如图14A和图14B所示,第1输入信号源12将具有从合成电路31输出的信号的电压成为“0.5”的振幅且具有大约135度的相位的第1信号输出到第1输入匹配电路14。

从合成电路31输出的合成信号的电压成为“0.5”的第1信号的振幅为零。

第2输入信号源13将第2晶体管20的输出功率例如成为饱和功率的大约一半的功率的信号作为第2信号输出到第1输入匹配电路14。

具体而言,如图14A和图14B所示,第2输入信号源13将具有从合成电路31输出的合成信号的电压成为“0.5”的振幅且具有大约0度的相位的第2信号输出到第2输入匹配电路15。

从合成电路31输出的合成信号的电压成为“0.5”的第2信号的振幅大于零且小于振幅的最大值。

第1输入匹配电路14在从第1输入信号源12接受第1信号后,将第1输入信号源12的阻抗转换成第1晶体管16的输入阻抗,将第1信号输出到第1晶体管16的输入端子16a。

即使从第1输入匹配电路14接受第1信号,第1信号的振幅也为零,因此,第1晶体管16停止而不进行信号的放大动作。

第1晶体管16停止,因此,如图15所示,第1晶体管16的电流源18成为开路的状态。

第2输入匹配电路15在从第2输入信号源13接受第2信号后,将第2输入信号源13的阻抗转换成第2晶体管20的输入阻抗,将第2信号输出到第2晶体管20的输入端子20a。

第2晶体管20在从第2输入匹配电路15接受第2信号后,对第2信号进行放大,将放大后的第2信号输出到第2输出电路27。

第2输出电路27将从第2晶体管20输出的第2信号传输到合成电路31。

在回退时动作中,从合成点32观察第1晶体管16时的阻抗无限大,因此,从第2输出电路27观察合成电路31时的阻抗成为0.5×Ropt。

第2输出电路27自身的特性阻抗为Ropt,从第2输出电路27观察合成电路31时的阻抗为0.5×Ropt,因此,将从第2晶体管20的电流源22观察合成点32时的阻抗从Ropt调制成2×Ropt。

第2输出电路27将从第2晶体管20的电流源22观察合成点32时的阻抗从Ropt调制成2×Ropt,由此,在第2晶体管20的输出功率比饱和功率低时,成为在第2晶体管20连接有高电阻的负载的状态。即,在第2输出电路27的输出功率比饱和功率低时,第2输出电路27的负载电阻成为比Ropt大的2×Ropt。

第2晶体管20成为连接有高电阻的负载的状态,因此,能够进行高效的放大动作。

如上所述,在以第3多赫蒂动作模式进行动作的多赫蒂放大器1中,与以第1多赫蒂动作模式进行动作的多赫蒂放大器1同样,也能够使回退时的效率特性宽带化。

实施方式5

在图3所示的多赫蒂放大器1中,第1输出电路24具有电容器19、第1传输线路25和第1电容器26。

此外,在图3所示的多赫蒂放大器1中,第2输出电路27具有电容器23、第2传输线路28、第3传输线路29和第2电容器30。

在实施方式5中,对第1输出电路24具有电容器19、电感器41和第1传输线路42且第2输出电路27具有电容器23、电感器43、第2传输线路44和第3传输线路45的多赫蒂放大器1进行说明。

实施方式5的多赫蒂放大器1的结构与实施方式1的多赫蒂放大器1的结构相同,示出实施方式5的多赫蒂放大器1的结构图是图3。

图16是示出实施方式5的多赫蒂放大器1的第1输出电路24的结构图。在图16中,与图3相同的标号表示相同或相当的部分,因此省略说明。

与图3所示的第1输出电路24同样,图16所示的第1输出电路24将从第1晶体管16输出的第1信号传输到合成电路31。

图16所示的第1输出电路24根据由第1晶体管16放大的第1信号的频率,对从第1晶体管16观察合成电路31时的阻抗进行调制。

与图3所示的第1输出电路24同样,图16所示的第1输出电路24的电长度根据第1信号的频率而变化。例如,在第1信号的频率是包含第1频率f

电感器41例如通过线来实现。

电感器41的一端与第1晶体管16的输出端子16b连接,电感器41的另一端与第1传输线路42的一端连接。

第1传输线路42的一端与电感器41的另一端连接,第1传输线路42的另一端与合成电路31的输入端子31a连接。

第1传输线路42例如是在第1信号的频率为第1频率f

图17是示出实施方式5的多赫蒂放大器1的第2输出电路27的结构图。在图17中,与图3相同的标号表示相同或相当的部分,因此省略说明。

与图3所示的第2输出电路27同样,图17所示的第2输出电路27将从第2晶体管20输出的第2信号传输到合成电路31。

图17所示的第2输出电路27根据由第2晶体管20放大的第2信号的频率,对从第2晶体管20观察合成电路31时的阻抗进行调制。

与图3所示的第2输出电路27同样,图17所示的第2输出电路27的电长度根据第2信号的频率而变化。例如,在第2信号的频率是中心频率f

电感器43例如通过线来实现。

电感器43的一端与第2晶体管20的输出端子20b连接,电感器43的另一端与第2传输线路44的一端连接。

第2传输线路44的一端与电感器43的另一端连接,第2传输线路44的另一端与第3传输线路45的一端连接。

第2传输线路44例如是在第2信号的频率为第1频率f

第3传输线路45的一端与第2传输线路44的另一端连接,第3传输线路45的另一端与合成电路31的输入端子31b连接。

第3传输线路45例如是在第2信号的频率为第1频率f

在第1输出电路24具有电容器19、电感器41和第1传输线路42的情况下,与图3所示的第1输出电路24同样,也能够根据第1信号的频率对从第1晶体管16观察合成电路31时的阻抗进行调制。

在第2输出电路27具有电容器23、电感器43、第2传输线路44和第3传输线路45的情况下,与图3所示的第2输出电路27同样,也能够根据第2信号的频率对从第2晶体管20观察合成电路31时的阻抗进行调制。

因此,在实施方式5的多赫蒂放大器1中,与实施方式1~4的多赫蒂放大器1同样,也能够使回退时的效率特性宽带化。

实施方式6

在图3所示的多赫蒂放大器1中,第1输出电路24具有电容器19、第1传输线路25和第1电容器26。

此外,在图3所示的多赫蒂放大器1中,第2输出电路27具有电容器23、第2传输线路28、第3传输线路29和第2电容器30。

在实施方式6中,对第1输出电路24具有电容器19、传输线路51、传输线路52、电容器53和电容器54且第2输出电路27具有电容器23、传输线路61、传输线路62、传输线路63、电容器64和电容器65的多赫蒂放大器1进行说明。

实施方式6的多赫蒂放大器1的结构与实施方式1的多赫蒂放大器1的结构相同,示出实施方式6的多赫蒂放大器1的结构图是图3。

图18是示出实施方式6的多赫蒂放大器1的第1输出电路24的结构图。在图18中,与图3相同的标号表示相同或相当的部分,因此省略说明。

与图3所示的第1输出电路24同样,图18所示的第1输出电路24传输从第1晶体管16输出的第1信号,将第1信号输出到合成电路31。

图18所示的第1输出电路24根据由第1晶体管16放大的第1信号的频率,对从第1晶体管16观察合成电路31时的阻抗进行调制。

与图3所示的第1输出电路24同样,图18所示的第1输出电路24的电长度根据第1信号的频率而变化。例如,在第1信号的频率是包含第1频率f

传输线路51的一端与第1晶体管16的输出端子16b连接,传输线路51的另一端与传输线路52的一端和电容器53的一端分别连接。

传输线路52的一端与传输线路51的另一端和电容器53的一端分别连接,传输线路52的另一端与合成电路31的输入端子31a和电容器54的一端分别连接。

例如,在第1信号的频率是第1频率f

电容器53与传输线路51并联连接。即,电容器53的一端与传输线路51的另一端和传输线路52的一端分别连接,电容器53的另一端与地线连接。

电容器54与传输线路52并联连接。即,电容器54的一端与传输线路52的另一端和合成电路31的输入端子31a分别连接,电容器54的另一端与地线连接。

图19是示出实施方式7的多赫蒂放大器1的第2输出电路27的结构图。在图19中,与图3相同的标号表示相同或相当的部分,因此省略说明。

与图3所示的第2输出电路27同样,图19所示的第2输出电路27传输从第2晶体管20输出的第2信号,将第2信号输出到合成电路31。

图19所示的第2输出电路27根据由第2晶体管20放大的第2信号的频率,对从第2晶体管20观察合成电路31时的阻抗进行调制。

与图3所示的第2输出电路27同样,图19所示的第2输出电路27的电长度根据第2信号的频率而变化。例如,在第2信号的频率是中心频率f

传输线路61的一端与第2晶体管20的输出端子20b连接,传输线路61的另一端与传输线路62的一端和电容器64的一端分别连接。

传输线路62的一端与传输线路61的另一端和电容器64的一端分别连接,传输线路62的另一端与传输线路63的一端和电容器65的一端分别连接。

传输线路63的一端与传输线路62的另一端和电容器65的一端分别连接,传输线路63的另一端与合成电路31的输入端子31b连接。

例如,在第1信号的频率是第1频率f

电容器64与传输线路61并联连接。即,电容器64的一端与传输线路61的另一端和传输线路62的一端分别连接,电容器64的另一端与地线连接。

电容器65与传输线路62并联连接。即,电容器65的一端与传输线路62的另一端和传输线路63的一端分别连接,电容器65的另一端与地线连接。

在第1输出电路24具有电容器19、传输线路51、传输线路52、电容器53和电容器54的情况下,与图3所示的第1输出电路24同样,也能够根据第1信号的频率对从第1晶体管16观察合成电路31时的阻抗进行调制。

在第2输出电路27具有电容器23、传输线路61、传输线路62、传输线路63、电容器64和电容器65的情况下,与图3所示的第2输出电路27同样,也能够根据第2信号的频率对从第2晶体管20观察合成电路31时的阻抗进行调制。

因此,在实施方式6的多赫蒂放大器1中,与实施方式1~4的多赫蒂放大器1同样,也能够使回退时的效率特性宽带化。

实施方式7

在图3所示的多赫蒂放大器1中,第1晶体管16的输入端子16a和第2晶体管20的输入端子20a分别被施加与临界电压大致相同的偏置电压。

第1晶体管16的输入端子16a也可以被施加比临界电压V

此外,第2晶体管20的输入端子20a也可以被施加比临界电压V

作为第1阈值电压V

实施方式7的多赫蒂放大器1的结构与实施方式1的多赫蒂放大器1的结构相同,示出实施方式7的多赫蒂放大器1的结构图是图3。

在第1晶体管16的输入端子16a被施加第1偏置电压V

此外,在第2晶体管20的输入端子20a被施加第1偏置电压V

第1晶体管16的输入端子16a也可以被施加比临界电压V

此外,第2晶体管20的输入端子20a也可以被施加比临界电压V

作为第2阈值电压V

在第1晶体管16的输入端子16a被施加第2偏置电压V

此外,在第2晶体管20的输入端子20a被施加第2偏置电压V

例如,在处于第1多赫蒂动作模式时,在第1晶体管16的输入端子16a被施加第1偏置电压V

例如,在处于第2多赫蒂动作模式或第3多赫蒂动作模式时,第1晶体管16的输入端子16a被施加第2偏置电压V

实施方式8

在实施方式8中,对具有控制电路71的多赫蒂放大器1进行说明,该控制电路71对分别施加给第1晶体管16的输入端子16a和第2晶体管20的输入端子20a的偏置电压进行控制。

图20是示出实施方式8的多赫蒂放大器1的结构图。在图20中,与图3相同的标号表示相同或相当的部分,因此省略说明。

控制电路71具有可变电源72、栅极偏置电路73和栅极偏置电路74。

控制电路71对分别施加给第1晶体管16的输入端子16a和第2晶体管20的输入端子20a的偏置电压进行控制。

可变电源72是能够使向栅极偏置电路73输出的电压和向栅极偏置电路74输出的电压分别可变的电源。

栅极偏置电路73例如通过电感器来实现。

栅极偏置电路73的一端与可变电源72连接,栅极偏置电路73的另一端与第1晶体管16的输入端子16a和第1输入匹配电路14b的另一端分别连接。

如果可变电源72的输出电压变高,则栅极偏置电路73提高施加给第1晶体管16的输入端子16a的偏置电压,如果可变电源72的输出电压变低,则栅极偏置电路73降低施加给第1晶体管16的输入端子16a的偏置电压。

栅极偏置电路74例如通过电感器来实现。

栅极偏置电路74的一端与可变电源72连接,栅极偏置电路74的另一端与第2晶体管20的输入端子20a和第2输入匹配电路15b的另一端分别连接。

如果可变电源72的输出电压变高,则栅极偏置电路74提高施加给第2晶体管20的输入端子20a的偏置电压,如果可变电源72的输出电压变低,则栅极偏置电路74降低施加给第2晶体管20的输入端子20a的偏置电压。

接着,对图20所示的多赫蒂放大器1的动作进行说明。但是,除了控制电路71以外的部分与图3所示的多赫蒂放大器1相同,因此,这里仅对控制电路71的动作进行说明。

控制电路71根据第1信号和第2信号各自的频率,对分别施加给第1晶体管16的输入端子16a和第2晶体管20的输入端子20a的偏置电压进行控制。

具体而言,如果第1信号的频率和第2信号的频率是第1频率f

如果第1信号的频率和第2信号的频率是第4频率f

如果第1信号的频率和第2信号的频率是第5频率f

如果第1信号的频率和第2信号的频率是第2频率f

如果第1信号的频率和第2信号的频率是第3频率f

控制电路71根据第1信号和第2信号各自的频率,对分别施加给第1晶体管16的输入端子16a和第2晶体管20的输入端子20a的偏置电压进行控制,由此,能够提高多赫蒂放大器1的增益和效率双方。

在图20所示的多赫蒂放大器1中,控制电路71根据第1信号和第2信号各自的频率,对分别施加给第1晶体管16的输入端子16a和第2晶体管20的输入端子20a的偏置电压进行控制。

但是,这只不过是一例,控制电路71也可以根据从信号源11输出的第1信号和第2信号各自的功率,对分别施加给第1晶体管16的输入端子16a和第2晶体管20的输入端子20a的偏置电压进行控制。

如果从第1输入信号源12输出的第1信号的功率变大,则控制电路71提高施加给第1晶体管16的输入端子16a的偏置电压,如果从第1输入信号源12输出的第1信号的功率变小,则控制电路71降低施加给第1晶体管16的输入端子16a的偏置电压。

如果从第2输入信号源13输出的第2信号的功率变大,则控制电路71提高施加给第2晶体管20的输入端子20a的偏置电压,如果从第2输入信号源13输出的第2信号的功率变小,则控制电路71降低施加给第2晶体管20的输入端子20a的偏置电压。

控制电路71根据从信号源11输出的第1信号和第2信号各自的功率,对分别施加给第1晶体管16的输入端子16a和第2晶体管20的输入端子20a的偏置电压进行控制,由此,能够抑制第1晶体管16和第2晶体管20各自的增益相对于输入功率的变动。

实施方式9

在实施方式9中,对具有控制电路81的多赫蒂放大器1进行说明,该控制电路81对分别施加给第1晶体管16的输出端子16b和第2晶体管20的输出端子20b的偏置电压进行控制。

图21是示出实施方式9的多赫蒂放大器1的结构图。在图21中,与图3和图20相同的标号表示相同或相当的部分,因此省略说明。

控制电路81具有可变电源82、栅极偏置电路73、栅极偏置电路74、漏极偏置电路83和漏极偏置电路84。

在图21所示的多赫蒂放大器1中,控制电路81具有栅极偏置电路73和栅极偏置电路74。但是,这只不过是一例,控制电路81也可以不具有栅极偏置电路73和栅极偏置电路74,而仅具有可变电源82、漏极偏置电路83和漏极偏置电路84。

与图20所示的控制电路71同样,控制电路81对分别施加给第1晶体管16的输入端子16a和第2晶体管20的输入端子20a的偏置电压进行控制。

此外,控制电路81对分别施加给第1晶体管16的输出端子16b和第2晶体管20的输出端子20b的偏置电压进行控制。

可变电源82是如下的电源:能够使向栅极偏置电路73输出的电压和向栅极偏置电路74输出的电压分别可变,此外,能够使向漏极偏置电路83输出的电压和向漏极偏置电路84输出的电压分别可变。

漏极偏置电路83例如通过电感器来实现。

漏极偏置电路83的一端与可变电源82连接,漏极偏置电路83的另一端与第1晶体管16的输出端子16b和第1传输线路25的一端分别连接。

如果可变电源82的输出电压变高,则漏极偏置电路83提高施加给第1晶体管16的输出端子16b的偏置电压,如果可变电源82的输出电压变低,则漏极偏置电路83降低施加给第1晶体管16的输出端子16b的偏置电压。

漏极偏置电路84例如通过电感器来实现。

漏极偏置电路84的一端与可变电源82连接,漏极偏置电路84的另一端与第2晶体管20的输出端子20b和第2传输线路28的一端分别连接。

如果可变电源82的输出电压变高,则漏极偏置电路84提高施加给第2晶体管20的输出端子20b的偏置电压,如果可变电源82的输出电压变低,则漏极偏置电路84降低施加给第2晶体管20的输出端子20b的偏置电压。

接着,对图21所示的多赫蒂放大器1的动作进行说明。但是,除了控制电路81以外的部分与图3和图20所示的多赫蒂放大器1相同,因此,这里仅对控制电路81的动作进行说明。

与图20所示的控制电路71同样,控制电路81对分别施加给第1晶体管16的输入端子16a和第2晶体管20的输入端子20a的偏置电压进行控制。

如果从第1输入信号源12输出的第1信号的功率变大,则控制电路81提高施加给第1晶体管16的输出端子16b的偏置电压,如果从第1输入信号源12输出的第1信号的功率变小,则控制电路81降低施加给第1晶体管16的输出端子16b的偏置电压。

如果从第2输入信号源13输出的第2信号的功率变大,则控制电路81提高施加给第2晶体管20的输出端子20b的偏置电压,如果从第2输入信号源13输出的第2信号的功率变小,则控制电路81降低施加给第2晶体管20的输出端子20b的偏置电压。

控制电路81根据从信号源11输出的第1信号和第2信号各自的功率,对分别施加给第1晶体管16的输出端子16b和第2晶体管20的输出端子20b的偏置电压进行控制,由此,能够根据第1晶体管16和第2晶体管20各自的输入功率,提高多赫蒂放大器1的增益和效率双方。

另外,本申请能够在其发明范围内进行各实施方式的自由组合、或各实施方式的任意结构要素的变形、或各实施方式中的任意结构要素的省略。

产业上的可利用性

本发明适用于对放大后的第1信号和放大后的第2信号进行合成的多赫蒂放大器和通信装置。

标号说明

1:多赫蒂放大器;11:信号源;12:第1输入信号源;13:第2输入信号源;14:第1输入匹配电路;15:第2输入匹配电路;16:第1晶体管;16a:输入端子;16b:输出端子;17:电容器;18:电流源;19:电容器;20:第2晶体管;20a:输入端子;20b:输出端子;21:电容器;22:电流源;23:电容器;24:第1输出电路;25:第1传输线路;26:第1电容器;27:第2输出电路;28:第2传输线路;29:第3传输线路;30:第2电容器;31:合成电路;31a:输入端子;31b:输入端子;32:合成点;33:输出匹配电路;34:负载;41:电感器;42:第1传输线路;43:电感器;44:第2传输线路;45:第3传输线路;51、52:传输线路;53、54:电容器;61、62、63:传输线路;64、65:电容器;71:控制电路;72:可变电源;73、74:栅极偏置电路;81:控制电路;82:可变电源;83、84:漏极偏置电路。

- 多赫蒂放大器和通信装置

- 陶赫蒂Doherty功率放大器、通信设备及系统