干蚀刻方法

文献发布时间:2023-06-19 11:27:38

技术领域

本发明涉及使用包含含氟不饱和烃的干蚀刻剂的干蚀刻方法。

背景技术

目前,在半导体制造中,微细化逐渐接近物理极限,为了弥补该情况,正在开发使结构物在高度方向上层叠而集成的方法。发现该倾向在NAND闪存中尤其显著,三维NAND闪存的研究开发正得以活跃化。

例如,三维NAND闪存采用如下构造:在基板上交替地层叠多层的多晶硅(以下称为poly-Si或p-Si)层和硅氧化物(以下称为SiO

因此,也正研究使用包含氮化硅(以下称为SiN)与SiO

在相对于该层叠膜的层的垂直方向上形成贯通孔的工序中,正研究对于SiN与SiO

然而,以独立的工序对每层进行蚀刻的情况,随着层叠数的增加,工序数也大幅增加。另外,仅为现有的CF系的气体的情况,SiN的蚀刻速度较慢,根据情况不同,SiN层上产生沉积,无法获得所需的蚀刻形状。因此,如专利文献1所示,在对包含至少1层氧化硅膜层与至少1层氮化硅膜层的层叠膜进行蚀刻的方法中,也存在使用通过包含CF系的气体与CHF系的气体的混合气体而以1次等离子体蚀刻同时蚀刻不同种类的层的方法的情况。

另外,专利文献2中公开了如下干蚀刻方法:其针对形成于基板上的硅氧化物层与硅氮化物层的层叠膜,将干蚀刻剂等离子体化而进行施加500V以上的偏压的蚀刻,从而形成相对于该层的垂直方向的贯通孔,该干蚀刻剂包含HFO-1234ze(E)与C

专利文献3中公开了一种干蚀刻方法,其将六氟丙烯与二氟甲烷的混合气体等离子体化,相对于硅氮化物而选择性地蚀刻硅氧化物。

专利文献4中公开了一种干蚀刻方法,其将包含六氟丙烯与氧气的干蚀刻气体等离子体化,并对硅氧化物、硅氮化物等硅系材料进行蚀刻。

现有技术文献

专利文献

专利文献1:日本特开2003-86568号公报

专利文献2:日本特开2017-50529号公报

专利文献3:日本特表2001-517868号公报

专利文献4:日本特开2017-92357号公报

发明内容

如上所述,专利文献1中公开了以设置于不同种类的层叠膜上部的抗蚀剂为掩膜,通过包含以C

另外,专利文献3中,由于选择性地蚀刻硅氧化物,因此无法在SiN与SiO

另一方面,根据专利文献2,通过使用包含HFO-1234ze(E)与C

然而,在通常的半导体元件中,为了防止因经蚀刻的孔的底部残留被蚀刻层所致的接触(导电)不良,通常将蚀刻时间延长1.1~2倍左右而以进行超出所需程度的蚀刻。然而,另一方面,为了防止产生过度的蚀刻,而在孔底部预先形成蚀刻终止层。该情况在形成较多的被称为3DNAND的元件的构造时也同样。即,在上述层叠膜蚀刻中虽存在高深宽比且深度数μm的蚀刻工序,但也需要利用存在于孔底部、即存在于贯通孔的底部的数nm至数十nm左右的蚀刻终止层使过度的蚀刻停止。

蚀刻终止层所使用的材质取决于前后的工序、元件整体的构造,因此不能一概而论,但大多数情况使用单晶Si、多晶Si(以下称p-Si)、W、WSi、Ti、TiN或TiO

本发明人使用专利文献2中记载的方法,结果获知:在高深宽比的层叠膜的蚀刻工序中确实可无形状不良地进行蚀刻,但另一方面,氟碳膜在蚀刻终止层上过度沉积而成为蚀刻残渣,结果存在产生孔底部的接触不良的情况。

认为只要深宽比为10左右较浅的孔,则通过蚀刻工序后的灰化、加热而蚀刻终止层上的氟碳膜也得以去除,但在深宽比20以上的较深的孔的情况下,无法有效地去除,存在残留的情况。

基于这些情况,期待在深宽比20以上的高深宽比蚀刻工序中也可进行无形状异常的蚀刻、且蚀刻终止层上不产生过度的沉积的蚀刻方法。

本发明是鉴于上述问题而完成的,提供可将用SiN的蚀刻速度除以SiO

本发明人等为实现上述目的而进行了各种研究,结果发现:在形成相对于基板上交替地层叠多层SiN与SiO

即,本发明提供一种干蚀刻方法,其特征在于,针对形成于基板上的硅氧化物层与硅氮化物层的层叠膜,经由形成于上述层叠膜上的具有特定的开口图案的掩膜,将干蚀刻剂等离子体化而进行施加绝对值为500V以上的负直流自偏压的蚀刻,从而形成相对于层叠膜的垂直方向的贯通孔,上述干蚀刻剂至少包含C

附图说明

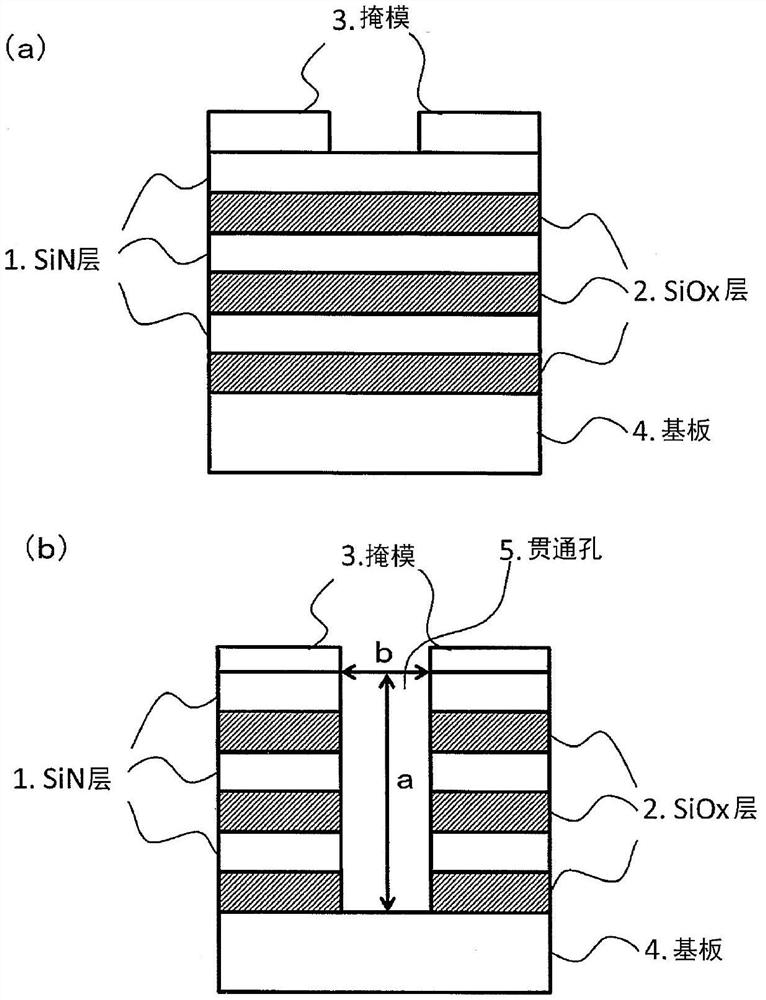

图1(a)、(b)是形成贯通孔的前与之后的元件的层叠构造的概略图。

图2是实施例、比较例中使用的反应装置的概略图。

图3(a)~(c)是示出实施例及比较例的SiN/SiO

具体实施方式

以下对本发明的实施方法进行说明。需要说明的是,本发明的范围并不限定于这些说明,除以下示例以外,也可在不损害本发明的主旨的范围内进行适当变更而实施。

本发明的干蚀刻方法中,如图1(a)所示,在基板4上预先制作包含SiN层1与SiO

本发明的干蚀刻方法中,使用包含C

作为C

若C

需要说明的是,C

如C

另一方面,对使用广泛用作蚀刻气体的C

从获得充分的蚀刻率的方面考虑,相对于除C

另外,C

本发明中,由于可任意地控制SiN层与SiO

另外,在干蚀刻剂中添加氧化性气体。作为氧化性气体,可使用O

另外,为了降低成本且提高操作的安全性,干蚀刻剂中优选包含非活性气体。作为非活性气体,可以使用氩气、氦气、氖气、氪气、氙气的稀有气体类、氮气。其中,从获得的容易度、相互作用较少的方面考虑,特别优选氩气。

另外,干蚀刻剂可仅由C

对于所产生的负直流自偏压,为了在相对于层的垂直方向上进行直线性较高的蚀刻,要求绝对值为500V以上,优选绝对值为1000V以上。负直流自偏压的绝对值越高则越可减少侧向蚀刻,但另一方面,若负直流自偏压的绝对值超过10000V,则对基板的损害变大而不优选。

关于蚀刻气体中含有的气体成分,可分别独立地导入至腔室内,或也可预先作为混合气体调整之后导入至腔室内。导入至反应腔室的干蚀刻剂的总流量可根据反应腔室的容积及排气部的排气能力,考虑前述浓度条件与压力条件而适当选择。

为了获得稳定的等离子体及为了提高离子的直线性而抑制侧向蚀刻,进行蚀刻时的压力优选10Pa以下,更优选5Pa以下,进一步优选1Pa以下。另一方面,若腔室内的压力过低,则电离离子变少而无法获得充分的等离子体密度,因此优选0.05Pa以上。

另外,进行蚀刻时的基板温度优选50℃以下,尤其是为了进行各向异性蚀刻,期望的是设为20℃以下。若为超过50℃的高温,则在侧壁生成的以氟碳自由基为主成分的保护膜的量减少,进行各向同性蚀刻的倾向增强,无法获得必需的加工精度。另外,有抗蚀剂等掩模材料被显著蚀刻的情况。

若考虑到元件制造工艺的效率,蚀刻时间优选60分钟以内。此处,蚀刻时间是指在腔室内产生等离子体、并使干蚀刻剂与试样反应的时间。

层叠膜中的层数、形成的贯通孔的深度没有特别限定,从获得利用层叠的集成效果的方面考虑,优选层数为6层以上,且贯通孔的深度为0.5μm以上。

另外,使用本发明的干蚀刻剂的蚀刻方法可不限定于电容耦合型等离子体(CCP)蚀刻、反应性离子蚀刻(RIE)、电感耦合型等离子体(ICP)蚀刻、电子回旋共振(ECR)等离子体蚀刻及微波蚀刻等各种蚀刻方法而进行。

另外,在包含SiN层与SiO

进而,在形成贯通孔时,可包括不向干蚀刻剂添加C

作为一例,例如考虑在蚀刻至交替层叠膜的一半左右(例如,交替层叠膜的厚度的1/2~5/8)时,使用添加有C

通过该方法,在开始切削不易进行水平方向的SiN蚀刻的贯通孔的阶段,可添加C

另外,作为其它例,考虑在蚀刻交替层叠膜的SiN层时应用本发明的蚀刻方法,在蚀刻SiO

通过该方法,在蚀刻SiN层时,可利用与SiO

需要说明的是,该方法中,必须根据SiN层与SiO

本发明的蚀刻方法中,优选使用SiN的蚀刻速度除以SiO

另外,本发明的蚀刻方法中,蚀刻时形成于基板上的源自干蚀刻剂的氟碳膜的生成速度优选1nm/分钟以下,更优选0.5nm/分钟以下。

另外,本发明的蚀刻方法中,作为用硅氧化物的蚀刻速度除以抗蚀剂的蚀刻速度而得到的值即SiO

进而,本发明的蚀刻方法对掩模也具有较高的选择性。因此,可将本发明的蚀刻方法用于制造三维NAND闪存的过程中在SiN与SiO

需要说明的是,通过本发明的蚀刻方法在包含SiN层与SiO

实施例

以下列举本发明的实施例及比较例,但本发明并不受以下实施例限制。

[实施例1]

(蚀刻工序)

图2是实施例、比较例中使用的反应装置10的概略图。腔室11内设置有具有保持试样18的功能且也作为载置台发挥作用的下部电极14、上部电极15及压力计12。另外,腔室11上部连接有气体导入口16。腔室11内可调整压力,且可通过高频电源(13.56MHz)13激发干蚀刻剂。由此,可使激发的干蚀刻剂与设置于下部电极14上的试样18接触而对试样18进行蚀刻。以如下方式构成:若在导入干蚀刻剂的状态下自高频电源13施加高频电力,则可由等离子体中的离子与电子的移动速度之差而在上部电极15与下部电极14之间产生被称为自偏压的直流电压。腔室11内的气体经由气体排出管线17排出。

作为试样18,将具有SiN层的硅晶圆A及具有SiO

此处,作为蚀刻剂,分别以相对于总流量为10体积%、5体积%、15体积%、70体积%将C

基于硅晶圆A的SiN层、硅晶圆B的SiO

[实施例2~12、比较例1~6]

使用CHF

将各实施例、比较例的结果记载于表1。表1中的蚀刻速度比为用SiN的蚀刻速度除以SiO

[表1]

使用以特定的比例至少包含C

另一方面,比较例1中,由于不包含含氢饱和氟碳,因此SiN蚀刻速度较低,SiN蚀刻速度与SiO

比较例4、5中,将不含氢的饱和或不饱和氟碳用作添加气体。在这些情况时,SiN的蚀刻速度不充分,SiN蚀刻速度与SiO

比较例6中,以相对于C

图3(a)、(b)、(c)是表示实施例1至12及比较例1至6的SiN/SiO

如此,在使用C

比较例1中,由于仅使用C

本发明在半导体制造工艺中对于三维集成的NAND闪存等元件形成布线是有效的。

1:SiN层

2:SiO

3:掩模

4:基板

5:贯通孔

10:反应装置

11:腔室

12:压力计

13:高频电源

14:下部电极

15:上部电极

16:气体导入口

17:排气管线

18:试样

- 过滤器及其制造方法以及干蚀刻用装置和干蚀刻方法

- 干式蚀刻方法、干式蚀刻气体及全氟-2-戊炔的制备方法