一种晶圆电容的制作方法、晶圆电容及电子设备

文献发布时间:2023-06-19 10:11:51

技术领域

本发明涉及半导体制造技术领域,尤其涉及一种晶圆电容的制作方法、晶圆电容及电子设备。

背景技术

在半导体制造过程当中,现有技术是使用MOS管(Metal-Oxide-Semiconductor即金属-氧化物-半导体,又称场效应管)替代电容进行电路设计,或者专门使用现有的技术在二维平面上制作电容,这种电容容量小,同一频率下,阻抗较大。现有的技术方案中,还可以采用上下两层金属,中间使用CVD方法(即气相沉积法)沉积二氧化硅,或其他介电物质,由于本身材质应力的问题,沉积的介电物质,厚度薄,且材质较为单一,不适用制作大电容,同时由于现在制作工艺的缺陷,不耐高压,容易击穿,容易使整个电路损坏。

发明内容

本申请实施例通过提供一种晶圆电容的制作方法、晶圆电容及电子设备,本发明提供的晶圆电容可以耐高压,不容易被击穿。

本发明提供一种晶圆电容的制作方法,包括:

对晶圆基底的背面进行打薄处理,使得所述晶圆基底的厚度达到设定厚度,所述晶圆基底设置有孔道,所述孔道中填充有铜柱,所述晶圆基底上设置有孔道的一面为正面,与所述正面相对的一面为所述背面;

对所述晶圆基底的背面做图像化处理,并对所述晶圆基底的背面进行刻蚀得到凹槽,通过所述凹槽露出所述晶圆基底的孔道中的铜柱;

在所述凹槽中制备接触金属层,得到晶圆电极;

选取两个所述晶圆电极,在其中一个所述晶圆电极的所述接触金属层表面制备介电材料层,所述介电材料层的介电常数大于200C

将两个所述晶圆电极键合形成晶圆电容,所述介电材料层位于两个所述晶圆电极的接触金属层之间。

优选的,所述在所述凹槽中制备接触金属层,得到晶圆电极,包括:

在所述凹槽的表面依次制备第一铜层、第二铜层、镍层以及金层,形成所述接触金属层。

优选的,所述在所述凹槽的表面依次形成第一铜层、第二铜层、镍层以及金层,包括:

在所述凹槽底面及侧壁形成所述第一铜层,

在所述第一铜层表面以及所述凹槽侧壁形成所述第二铜层,

在所述第二铜层表面形成所述镍层,以及

在所述镍层表面形成所述金层。

优选的,所述凹槽侧壁的所述第二铜层厚度,与所述凹槽底面的所述第二铜层厚度的比例在1:5~1:10之间。

优选的,所述在所述凹槽的表面依次制备第一铜层、第二铜层、镍层以及金层,还包括:

在通过溅射方法在所述凹槽底面及侧壁形成所述第一铜层,通过电镀方法在所述第一铜层表面以及所述凹槽侧壁形成所述第二铜层之后,通过湿法刻蚀的方法去除所述凹槽侧壁上的所述第一铜层和所述第二铜层。

优选的,所述介电材料层的材料二氧化钛和/或钛酸钡;所述湿法刻蚀采用的刻蚀液为三氯化铁、硫酸铁、双氧水中的一种。

优选的,所述对所述晶圆基底进行刻蚀得到凹槽,具体为:

通过深硅干法刻蚀方法对所述晶圆基底进行刻蚀,得到所述凹槽。

优选的,所述在其中一个所述晶圆电极的所述接触金属层表面制备介电材料层,包括:

通过旋涂或印刷的方法在所述接触金属层表面制备所述介电材料层。

本发明还提供一种晶圆电容,所述晶圆电容为上述的制作方法制备而成。

本发明还提供一种电子设备,其包含上述制作方法制备而成的晶圆电容。实施本发明,具有如下有益效果:本发明中的晶圆电容的介电材料层的材料为二氧化钛和/或钛酸钡,二氧化钛和钛酸钡的介电常数大于二氧化硅,可以耐高压,不易被击穿,可以作为大容量的电容,而且二氧化钛和钛酸钡的介电常数较大,介电材料层的厚度可以制备得较薄,解决材质应力的问题,不容易被折断。

附图说明

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

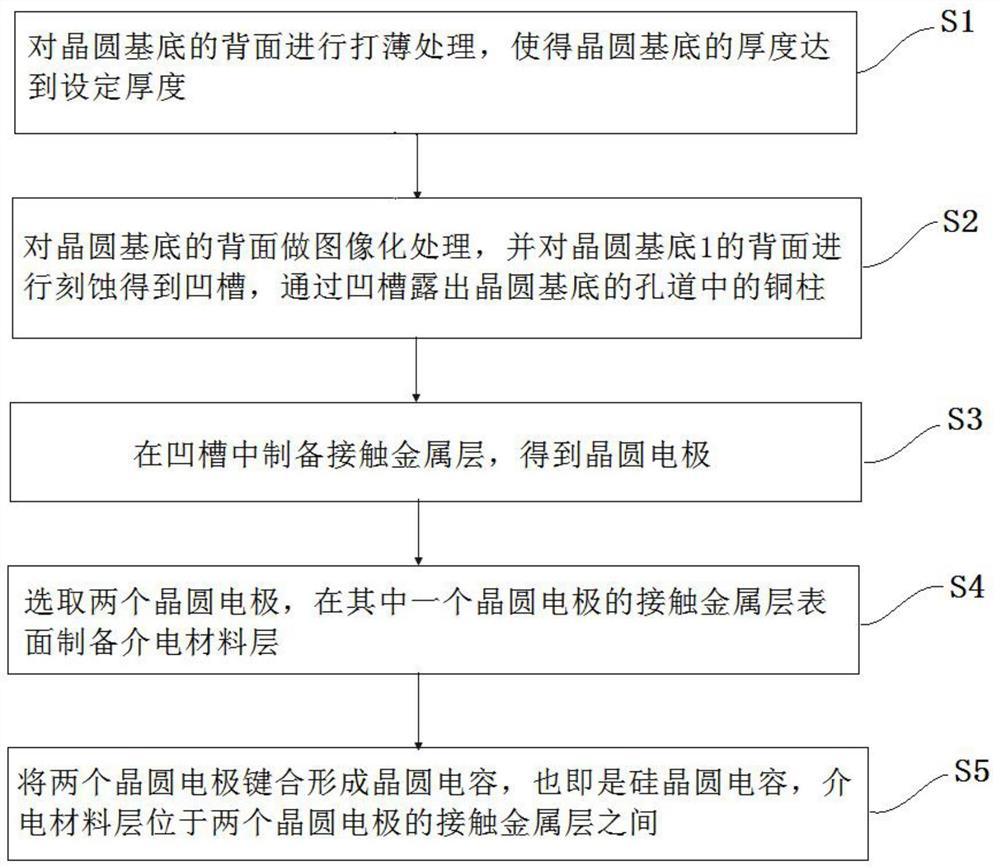

图1是本发明提供的晶圆电容的制作方法流程图;

图2是本发明提供的晶圆基底的示意图;

图3是本发明提供的图2中晶圆基底的孔道示意图;

图4是本发明提供的在图2所述的晶圆基底的背面形成凹槽的示意图;

图5是本发明提供的在图4所述的凹槽上制备接触金属层和介质材料层的示意图;

图6是本发明提供的将两个晶圆电极进行键合形成晶圆电容的示意图。

为了使本申请所属技术领域中的技术人员更清楚地理解本申请,下面结合附图,通过具体实施例对本申请技术方案作详细描述。

本发明提供了一种晶圆电容的制作方法,如图1所示,该制造方法包括:

S1、对图2所示的晶圆基底1的背面进行打薄处理,使得晶圆基底1的厚度达到设定厚度;如图3所示,晶圆基底1设置有孔道,孔道11中填充有铜柱2,晶圆基底1上设置有孔道11的一面为正面,与正面相对的一面为背面;晶圆基底1为硅晶圆基底,即在硅材料层上形成孔道11,孔道11中填充有铜柱2;

提供一种晶圆,晶圆包括相对设置的第一表面及第二表面,在第一表面设置孔道11,对第二表面进行打薄处理,使得晶圆1的厚度达到设定厚度。

在一实施例中,对图2所示的晶圆基底1的背面进行打薄处理,可以采用晶圆背面研磨工艺或者半导体磨片机进行打薄处理。

孔道11可以通过TSV(Through SiliconVia,,硅通孔技术)方法进行打孔。

S2、对晶圆基底1的背面做图像化处理,并对晶圆基底1的背面进行刻蚀得到图4所示的凹槽12,通过凹槽12露出晶圆基底1的孔道11中的铜柱2。

S3、如图5所示,在凹槽12中制备接触金属层3,得到晶圆电极,晶圆电极包括晶圆基底1、铜柱2和接触金属层3。

S4、选取两个晶圆电极,在其中一个晶圆电极的接触金属层3表面制备介电材料层4。

S5、如图6所示,将两个晶圆电极键合形成晶圆电容,也即是硅晶圆电容,介电材料层4位于两个晶圆电极的接触金属层3之间;晶圆电容包括两个晶圆电极以及介电材料层4,介电材料层的介电常数大于200C

在凹槽12中制备接触金属层3,得到晶圆电极,包括:

在凹槽12的表面依次制备第一铜层31、第二铜层32、镍层33以及金层34,形成接触金属层3。

在凹槽12的表面依次制备第一铜层31、第二铜层32、镍层33以及金层34,包括:

通过溅射方法在凹槽12底面及侧壁形成第一铜层31,通过电镀方法在第一铜层31表面以及凹槽12侧壁形成第二铜层32,通过化学镀方法在第二铜层32表面形成镍层33,以及通过化学镀方法在镍层33表面形成金层34。

通过溅射方法形成第一铜层31,可以保证第一铜层31的厚度均匀,进而保证电容两个电极之间的厚度均匀,通过电镀方法形成第二铜层32,可以保证电容电极增厚,并且增厚速度快。

镍层33设置在第二铜层32与金层34之间,可以将第二铜层32与金层34隔开,防止第二铜层32与金层34之间的原子扩散;当铜原子扩散到金层34中时,介电材料层4中的氧会渗透到金层34中,将铜氧化,使得电容电极生锈,降低电容使用寿命,因而本发明采用的制备方法还可以避免电容电极被氧化,延长了晶圆电容的使用寿命。

而且,本发明中的电容电极采用铜作为电极,任何一个电极作为正负极都可以,提高了晶圆电容的应用范围。

在一实施例中,镍层33可以是镍金属层或者镍钯合金层34。

在凹槽12的表面依次制备第一铜层31、第二铜层32、镍层33以及金层34,还包括:

在通过溅射方法在凹槽12底面及侧壁形成第一铜层31,通过电镀方法在第一铜层31表面以及凹槽12侧壁形成第二铜层32之后,通过湿法刻蚀的方法去除凹槽12侧壁上的第一铜层31和第二铜层32。

通过电镀的方式可以在第一铜层31表面形成一层较厚的铜层,使其第二铜层32的厚度可以满足电容电极的要求。第二铜层的厚度大于第一铜层的厚度。

在采用湿法刻蚀的方法去除凹槽12侧壁上的第一铜层31和第二铜层32时,湿法刻蚀采用的刻蚀液可以是三氯化铁、硫酸铁、双氧水中的一种。刻蚀液具有各向同性,通过调整刻蚀液的刻蚀时间,可以将凹槽12侧壁的第一铜层31和第二铜层32刻蚀掉,保留凹槽12底面的第一铜层31和第二铜层32。

其中,通过溅射方法在凹槽12底面及侧壁形成第一铜层31,凹槽12底面的第一铜层31与凹槽12侧壁的第一铜层31的厚度比为1:1,凹槽12侧壁的第二铜层厚度,与凹槽12底面的第二铜层32厚度的比例在1:5~1:10之间。

在通过电镀方法制备第二铜层32时,通过孔道11中的铜柱2以及与铜柱2电性连接的第一铜层31接通电流,通过控制第一铜层31接入电流的大小及时间,使得第二铜层32的厚度达到预设厚度值,再结合电镀经验得到的凹槽12底面第二铜层32与凹槽12侧壁第二铜层32的厚度比,计算出凹槽12侧壁的第二铜层厚度值。

在另一实施例中,还可以通过扫描电子显微镜或者X射线分析方法测量凹槽12侧壁的第二铜层的厚度值。

在通过湿法刻蚀的方法去除凹槽12侧壁上的第一铜层31和第二铜层32时,可以结合刻蚀液的刻蚀速度以及凹槽12侧壁的第二铜层厚度值,计算出刻蚀液刻蚀的时间,进而可以准确控制湿法刻蚀的进度。

对晶圆基底1进行刻蚀得到凹槽12,具体为:

通过深硅干法刻蚀方法对晶圆基底1进行刻蚀,得到凹槽12。

在其中一个晶圆电极的接触金属层3表面制备介电材料层4,包括:

通过旋涂或印刷的方法在接触金属层3表面制备介电材料层4。

介电材料层4的材料可以包含有二氧化钛和/或钛酸钡。其中钛酸钡的介电常数在1800~2700C

传统电容中采用二氧化硅作为介电材料,其介电常数较小,电容容量较小,二氧化钛和钛酸钡制备的介电常数大于二氧化硅,因此本发明提供的晶圆电容的容量比传统电容容量更大,储能效果较好,在电路断电时,可以缓慢放电。

本发明还提供一种晶圆电容,晶圆电容为上述的制作方法制备而成。

本发明还提供一种电子设备,该电子设备包含上述制作方法制备而成的晶圆电容。

综上所述,本发明提供的晶圆电容的制作方法、晶圆电容及电子设备,可以直接在晶圆上制备电容,不需要在PCB(Printed Circuit Board,印刷电路板)上制备电容,节省了PCB的使用面积。而且,本发明中的晶圆电容的介电材料层4的材料为二氧化钛和/或钛酸钡,二氧化钛和钛酸钡的介电常数大于二氧化硅,可以耐高压,不易被击穿,可以作为大容量的电容。此外,现有技术中在PCB上制备电容,再将PCB上的电容集成到晶圆上,PCB上的电容与晶圆集成电路之间的导线长度大于1毫米,本发明中提供的晶圆电容,电容与晶圆集成电路之间的导线长度相当于孔道11的深度,即50微米~200微米,因此,本发明提供的晶圆电容与晶圆集成电路之间的导线长度相对较短,减小了电流的传输距离,减少了电路的功耗。

尽管已描述了本发明的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本发明范围的所有变更和修改。

显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

- 一种晶圆电容的制作方法、晶圆电容及电子设备

- 集成无源电容扇出型晶圆级封装结构及制作方法