FPGA在模组信号发生器中管理存储Bmp图片的方法、系统及操控方法和操控系统

文献发布时间:2023-06-19 10:54:12

技术领域

本发明涉及液晶模组测试设备以及图像处理技术领域,尤其涉及一种FPGA在模组信号发生器中管理存储Bmp图片的方法、系统及操控方法和操控系统。

背景技术

在液晶模组测试领域,客户需要模组信号发生器支持不同分辨率、色深,刷新率等屏体点屏需求;需要实现翻转、水平移动、垂直移动等特殊画面功能;而且需要支持水平分屏、垂直分屏、田字分屏等多种分屏模式。

液晶模组测试设备领域中的模组信号发生器的主控芯片比较典型有两种选择:ARM和FPGA。

其中ARM实现有一个致命的缺点,大分辨率的屏无法满足画面刷新率带宽的要求。

其中FPGA是市场上主流的选择,FPGA典型在内存中存储bmp图片数据的方法一般都是直接存储于内存中,不做任何处理。不足地方在于:实现6、8、10bit不同色深,不同分辨率的图片移动,分屏功能时逻辑代码会非常复杂,消耗大量的逻辑资源,很难简易实现移动和分屏等复杂的特殊功能,甚至出现Fmax(Frequency max)无法满足要求的情况。

发明内容

为了解决现有技术中的问题,本发明提供了一种液晶模组测试设备领域中的模组信号发生器的主控芯片FPGA在内存中存储Bmp图片的方法,其目的在于在满足客户所有功能需求的前提下,提供一种简单,低成本,易实现的方法。

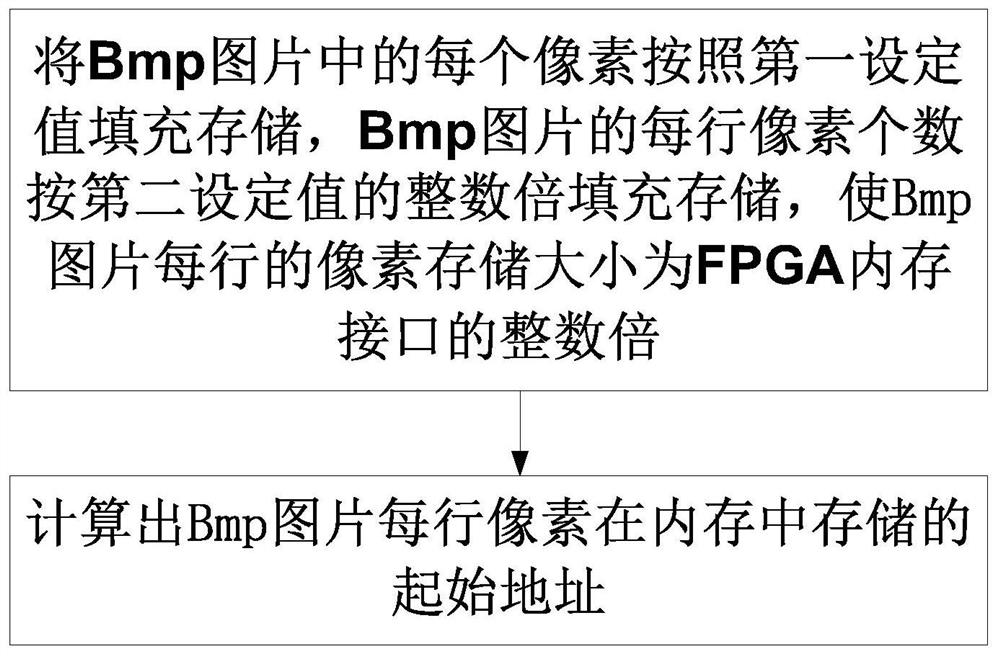

本发明提供了一种FPGA在模组信号发生器中管理存储Bmp图片的方法,包括如下步骤:

存储调整步骤:将Bmp图片中的每个像素按照第一设定值填充存储,Bmp图片的每行像素个数按第二设定值的整数倍填充存储,使Bmp图片每行的像素存储大小为FPGA内存接口的整数倍;

计算步骤:计算出Bmp图片每行像素在内存中存储的起始地址。

作为本发明的进一步改进,所述第一设定值为32bit。

作为本发明的进一步改进,所述第二设定值为2的整数倍个像素,暂取为16个像素。

作为本发明的进一步改进,该方法能够同时满足存储RGB 6bit、8bit、10bit三种类型的像素。

作为本发明的进一步改进,针对位图RGB 6bit单个像素存储,每个像素按32bit存储在内存中,其中R[5:0],G[5:0],B[5:0]为Bmp图片的RGB分量值,RGB一共18bit,组成32bit需要填充14bit的数据;

针对位图RGB 8bit单个像素存储,每个像素按32bit存储在内存中,其中R[7:0],G[7:0],B[7:0]为Bmp图片的RGB分量值,RGB一共24bit,组成32bit需要填充8bit的数据;

针对位图RGB 10bit单个像素存储,每个像素按32bit存储在内存中,其中R[9:0],G[9:0],B[9:0]为Bmp图片的RGB分量值,RGB一共18bit,组成32bit需要填充2bit的数据。

作为本发明的进一步改进,在所述计算步骤中,Bmp图片每行像素在内存中存储的起始地址的计算公式如下:如果H/第二设定值为整数,则:R*(H/第二设定值)*第一设定值/内存位宽;如果H/第二设定值不为整数,则:R*(H/第二设定值+1)*第一设定值/内存位宽;其中,H表示行像素个数,R表示第几行像素,R=0,1,2,......。

本发明还提供了一种FPGA在模组信号发生器中管理存储Bmp图片的系统,包括:

存储调整模块:用于将Bmp图片中的每个像素按照第一设定值填充存储,Bmp图片的每行像素个数按第二设定值的整数倍填充存储,使Bmp图片每行的像素存储大小为FPGA内存接口的整数倍;

计算模块:用于计算出Bmp图片每行像素在内存中存储的起始地址。

作为本发明的进一步改进,所述第一设定值为32bit,所述第二设定值为2的整数倍个像素,暂取值为16。

作为本发明的进一步改进,该系统能够同时满足存储RGB 6bit、8bit、10bit三种类型的像素。

作为本发明的进一步改进,在所述计算模块中,Bmp图片每行像素在内存中存储的起始地址的计算公式如下:如果H/第二设定值为整数,则:R*(H/第二设定值)*第一设定值/内存位宽;如果H/第二设定值不为整数,则:R*(H/第二设定值+1)*第一设定值/内存位宽;其中,H表示行像素个数,R表示第几行像素,R=0,1,2,......。

本发明还提供了一种FPGA在模组信号发生器中对Bmp图片的操控方法,使用本发明FPGA在内存中存储Bmp图片的方法计算出Bmp图片每行像素在内存中存储的起始地址后,根据得到的起始地址,FPGA实现对Bmp图片的移动和分屏。

本发明还提供了一种FPGA在模组信号发生器中对Bmp图片的操控系统,使用本发明的FPGA在内存中存储Bmp图片的系统计算出Bmp图片每行像素在内存中存储的起始地址后,根据得到的起始地址,FPGA实现对Bmp图片的移动和分屏。

本发明的有益效果是:本发明可以同时满足在不同分辨率、色深、刷新率条件下的,高分辨率的画面刷新带宽、移动、分屏等不同的功能需求;通过本发明,FPGA逻辑代码实现简易,消耗更少的逻辑资源。

附图说明

图1是位图RGB 6bit单个像素存储样式的示意图;

图2是位图RGB 8bit单个像素存储样式的示意图;

图3是位图RGB 10bit单个像素存储样式的示意图;

图4是每行像素存储样式的示意图;

图5是整帧图片存储样式的示意图;

图6是本发明的方法流程图。

具体实施方式

如图6所示,本发明公开了一种FPGA在模组信号发生器中管理存储Bmp(Bitmap)图片的方法,包括如下步骤:

存储调整步骤:将Bmp图片中的每个像素按照第一设定值(第一设定值为32bit)填充存储,每行像素个数按第二设定值(第二设定值可以是16个像素或32个像素等值,暂选为16个像素)整数倍填充存储,FPGA操作内存接口一般常见为256、512bit,这样使Bmp图片每行的像素存储大小为FPGA内存接口的整数倍。

计算步骤:使Bmp图片每行像素起始位置为一个确切的地址(即,计算出Bmp图片每行像素在内存中存储的起始地址),知道每行的像素的起始地址即可简易地完成移动、分屏的功能。

在所述计算步骤中,Bmp图片每行像素在内存中存储的起始地址的计算公式如下:如果H/第二设定值为整数,则:R*(H/第二设定值)*第一设定值/内存位宽;如果H/第二设定值不为整数,则:R*(H/第二设定值+1)*第一设定值/内存位宽;其中,H表示行像素个数,R表示第几行像素,R=0,1,2,......。

具体为:第一设定值为32,第二设定值为16;R表示第几行像素,R从0开始。

该方法能够同时满足存储RGB 6bit、8bit、10bit三种类型的像素,下面进行详细说明:

图1为本发明对位图RGB 6bit单个像素存储样式,每个像素按32bit存储在内存中;其中R[5:0],G[5:0],B[5:0]为Bmp图片的RGB分量值,RGB一共18bit,组成32bit需要填充14bit的数据。填充位置和内容可以按上述样式填充,亦可调整为其它位置和内容。

图2为本发明对位图RGB 8bit单个像素存储样式,每个像素按32bit存储在内存中;其中R[7:0],G[7:0],B[7:0]为Bmp图片的RGB分量值,RGB一共24bit,组成32bit需要填充8bit的数据。填充位置和内容可以按图中样式填充,亦可调整为其它位置和内容。

图3为本发明对位图RGB 10bit单个像素存储样式,每个像素按32bit存储在内存中;其中R[9:0],G[9:0],B[9:0]为Bmp图片的RGB分量值,RGB一共18bit,组成32bit需要填充2bit的数据。填充位置和内容可以按上述样式填充,亦可调整为其它位置和内容。

图4每行像素存储样式,每行像素个数按16的整数倍填充存储,图示例行像素值为1366,1366需补充10个像素1376可被16整除。图4中1表示,Pixel 1360-1365有真实像素,1366-1375为Dummy填充像素。填充位置和内容可以按图4所示样式,亦可调整为其它位置和内容。

图5整帧图片存储样式,图中示例1366x768这种分辨率图片在内存中的存储结构,1366不被16整除,则填充10个像素。这种存储方式,易于寻找到每一行像素在内存的中的起始位置,从而易于实现移动、分屏等功能。

本发明还公开了一种FPGA在模组信号发生器中管理存储Bmp图片的系统,包括:

存储调整模块:用于将Bmp图片中的每个像素按照第一设定值填充存储,Bmp图片的每行像素个数按第二设定值的整数倍填充存储,使Bmp图片每行的像素存储大小为FPGA内存接口的整数倍。

计算模块:用于计算出Bmp图片每行像素在内存中存储的起始地址。

所述第一设定值为32bit,所述第二设定值为16个像素。

该系统能够同时满足存储RGB 6bit、8bit、10bit三种类型的像素。

针对位图RGB 6bit单个像素存储,每个像素按32bit存储在内存中,其中R[5:0],G[5:0],B[5:0]为Bmp图片的RGB分量值,RGB一共18bit,组成32bit需要填充14bit的数据。

针对位图RGB 8bit单个像素存储,每个像素按32bit存储在内存中,其中R[7:0],G[7:0],B[7:0]为Bmp图片的RGB分量值,RGB一共24bit,组成32bit需要填充8bit的数据。

针对位图RGB 10bit单个像素存储,每个像素按32bit存储在内存中,其中R[9:0],G[9:0],B[9:0]为Bmp图片的RGB分量值,RGB一共18bit,组成32bit需要填充2bit的数据。

在所述计算模块中,如果H/第二设定值为整数,则:R*(H/第二设定值)*第一设定值/内存位宽;如果H/第二设定值不为整数,则:R*(H/第二设定值+1)*第一设定值/内存位宽;其中,H表示行像素个数,R表示第几行像素,R=0,1,2,......。

本发明还公开了一种FPGA在模组信号发生器中对Bmp图片的操控方法,使用本发明的FPGA在内存中存储Bmp图片的方法计算出Bmp图片每行像素在内存中存储的起始地址后,根据得到的起始地址,FPGA实现对Bmp图片的移动和分屏。移动包括翻转、水平移动、垂直移动,分屏包括水平分屏、垂直分屏、田字分屏等多种分屏模式。

例如,在计算出Bmp图片每行像素在内存中存储的起始地址后,FPGA可以简易实现移动和分屏的功能,图片垂直方向(上移/下移)的移动,当前帧从0行开始刷图,下一帧从x行开始刷图,下下帧从2x行开始刷图,其中x表示每帧移动的步进。

例如,在计算出Bmp图片每行像素在内存中存储的起始地址后,FPGA即可实现图片移动的效果,图片垂直方向的两分屏,第一分屏从0行到r/2-1行,第二分屏从r/2到r-1行(其中r为整幅图片的行数),根据简易计算每行像素在内存中存储的起始地址,即可完成分屏操作。

本发明还公开了一种FPGA在模组信号发生器中对Bmp图片的操控系统,使用本发明的FPGA在内存中存储Bmp图片的系统计算出Bmp图片每行像素在内存中存储的起始地址后,根据得到的起始地址,FPGA实现对Bmp图片的移动和分屏。

本发明可以同时满足在不同分辨率、色深、刷新率条件下的,高分辨率的画面刷新带宽、移动、分屏等不同的功能需求;通过本发明,FPGA逻辑代码实现简易,消耗更少的逻辑资源。

以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

- FPGA在模组信号发生器中管理存储Bmp图片的方法、系统及操控方法和操控系统

- 一种单BMP图片存储多张图片的方法及系统