计算机实施方法、计算机实施系统及计算机可读媒体

文献发布时间:2023-06-19 13:49:36

技术领域

本揭露中所描述的技术通常涉及集成电路系统芯片设计实施流程,且更具体地说,涉及用于在集成电路上实施的优化电路合成。

背景技术

可使用多种技术来优化设计具有半导体装置的专用集成电路(applicationspecific integrated circuits;ASIC)和片上系统(System on Chips;SoC)。此类设计可为一系列变化的硅设计、实施以及制造技术,但不限于3纳米、5纳米、7纳米、10纳米、12纳米、16纳米、28纳米及/或许多其它技术。可基于使用例如功率性能面积的多种技术来优化例如随机存取存储器(random access memory;RAM)等的这些芯片的存储元件。此优化可为劳动密集的且耗时的。

发明内容

本揭露的计算机实施方法用于在集成电路上实施的优化电路合成。计算机实施方法包括:输入电路的逻辑行为的寄存器传输级代码描述;将寄存器传输级代码描述转换成用于多种类型的组件及特征尺寸技术的结构上界定的电路设计;产生每一结构上界定的电路设计的平面布局图;对每一平面布局图创建实体模拟电路;以及扫描一系列操作条件以分析每一实体模拟电路的功率、性能以及面积。

本揭露的计算机实施系统用于在集成电路上实施的优化电路合成。计算机实施系统包括转换模块、模拟模块以及分析模块。转换模块配置成存取电路的行为的寄存器传输级代码描述,并将寄存器传输级代码转换成用于多种类型的组件及特征尺寸技术的一组结构上界定的电路设计。模拟模块配置成存取所述一组结构上界定的电路设计并对每一平面布局图创建实体模拟电路。分析模块配置成存取实体模拟电路并扫描实体模拟电路的一系列操作条件,以产生对于实体模拟电路的功率、性能以及面积特性的一组分析。

本揭露的非暂时性计算机可读媒体对用于制造集成电路的存储器存储指令进行编码。所述指令在被执行时引起包括以下各项的操作:产生每一结构上界定的电路设计的平面布局图;对每一平面布局图创建实体模拟电路;以及扫描一系列操作条件以分析每一实体模拟电路的功率、性能以及面积。

附图说明

结合附图阅读以下详细描述会最佳地理解本揭露的各方面。应注意,根据业界中的标准惯例,各种特征未按比例绘制。实际上,为了论述清楚起见,可任意增大或减小各种特征的尺寸。

图1是根据本揭露的各种实施例的用于分析和提取来自跨各种技术尺寸(例如,5纳米、7纳米、10纳米、12纳米、16纳米、28纳米等)的RAM配置和寄存器堆的数据的示例性系统的框图。

图2是根据本揭露的各种实施例的用于分析和提取来自跨各种技术尺寸(例如,5纳米、7纳米、10纳米、12纳米、16纳米、28纳米等)的RAM配置和寄存器堆的数据的另一示例性系统的框图。

图3是根据本揭露的各种实施例的用于分析和提取来自跨各种技术尺寸(例如,5纳米、7纳米、10纳米、12纳米、16纳米、28纳米等)的RAM配置和寄存器堆的数据的另一示例性系统的框图。

图4是示出根据本揭露的各种实施例的合成网表的产生的示例性框图。

图5是示出根据本揭露的各种实施例的合成CPU网表的产生的示例性框图。

图6是示出根据本揭露的各种实施例的PPA分析的示例性图解。

图7是示出根据本揭露的各种实施例的合成ML网表的产生的示例性框图。

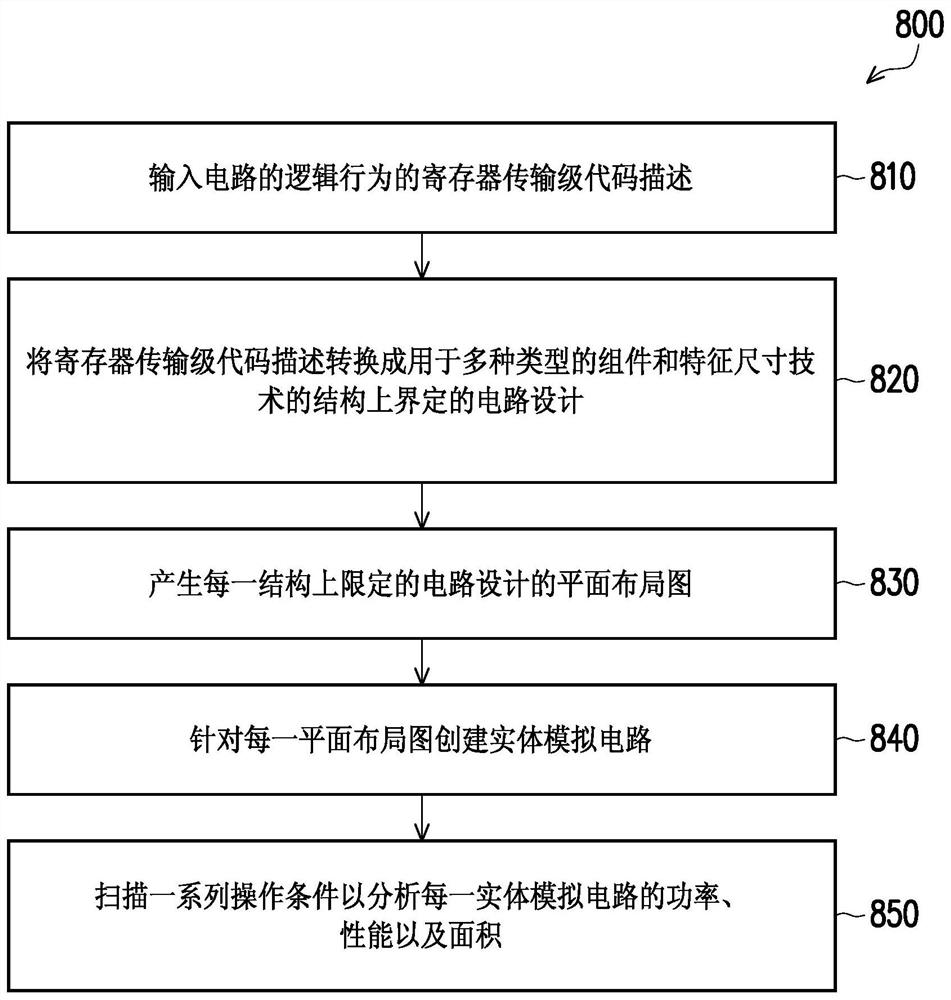

图8是示出根据本揭露的各种实施例的用于在集成电路上实施的优化电路合成的方法的示例性流程图。

图9是示出用于实施本文中所描述的各种方面的样本计算装置架构的示例性框图。

附图标号说明

100、200、300:系统;

210:转换模块;

220:平面布局图映射模块;

230:模拟模块;

240:分析模块;

310:分类模块;

320:显示模块;

330:电路设计模块;

340:合成模块;

350:网表创建模块;

400、500、700、900:框图;

402、404、406、501、502、503、504、505、701、702、703、704、705:文件列表;

410:存储器尺寸提取器;

412:追踪器;

422、424、426:逻辑门配置;

431:单端口静态随机存取存储器;

432:双端口静态随机存取存储器;

433:复式端口静态随机存取存储器;

434:2P RF组件;

436、520:寄存器编译器;

437:1P RF组件;

440:包装器;

452、454、456:网表;

460:区块;

511、512、513、514:编译;

515:寄存器触发器存储;

521、522、523、524、525:CPU网表;

530:用户界定;

600:图解;

721、722、723、724、725:ML网表;

800:流程图;

810、820、830、840、850:步骤;

904:总线;

908:处理系统;

912:只读存储器;

914:显示界面;

916:随机存取存储器;

920:通信端口;

928:输入装置界面;

932:输入装置;

936:键盘;

940:显示装置;

948:磁盘控制器;

952、956:磁盘驱动器。

具体实施方式

以下公开内容提供用于实施所提供主题的不同特征的许多不同实施例或实例。下文描述组件和布置的具体实例以简化本揭露。当然,这些仅为实例且并不意图为限制性的。举例来说,在以下描述中,第一特征在第二特征上方或第二特征上的形成可包含第一特征与第二特征直接接触地形成的实施例,且还可包含可在第一特征与第二特征之间形成额外特征从而使得第一特征与第二特征可不直接接触的实施例。另外,本揭露可在各种实例中重复附图标号和/或字母。此重复是出于简化和清楚的目的,且本身并不指示所论述的各种实施例和/或配置之间的关系。

随着电子组件的尺寸持续减小且电路布局变得更复杂,电路布局的模拟可帮助优化电路设计和安置。数千种ASIC设计存在以用于各种RAM、寄存器以及其它存储元件。这些设计可大大地不同于彼此,因为每一种设计可考虑各种类型的RAM编译器、单元类型(例如,6T或8T)、装置速度或密度、组件阈值电压、功率需求等。一起编译这些设计可有助于优化新电路设计。新设计可以优化用于特定目的的布局的方式从现存设计中并入适当特征。换句话说,设计可为可合成的,以用于跨各种装置尺寸(5纳米、7纳米、10纳米、12纳米、16纳米、28纳米等)的硅实施。编译设计(例如,提取的数据)包含电路行为的描述。使用提取的数据,可通过将电路行为翻译成界定各种电子组件尺寸和布局的一组结构上界定的电路布局来实体模拟新电路。布局可被分析以存取实体模拟电路且接着可扫描实体模拟电路的一系列操作条件(例如,使用合成变量扫描系统(synthesis variable sweep system;SVSS)),以产生具有对于实体模拟电路的功率、性能以及面积(power,performance,and area;PPA)特性的一组分析的优化的网表(netlist)。此输出可提供优化的实体模拟电路。可在例如高效计算(high performance computing;HPC)、5G移动设备、汽车、人工智能或物联网(internet of things;IoT)的许多不同行业中应用此类电路。

图1是根据本揭露的各种实施例的用于分析和提取来自跨各种技术尺寸(例如,5纳米、7纳米、10纳米、12纳米、16纳米、28纳米等)的RAM配置和寄存器堆的数据的示例性系统100的框图。系统100可为接收界定各种电路的逻辑行为的RAM行为模型的寄存器传输级(register transfer level;RTL)设计的数据处理计算机系统。RTL是根据硬件寄存器之间的数字信号流和对那些信号执行的逻辑操作来模型化同步数字电路的设计抽象概念。如图2至图3中更详细描述,系统100使用多个模块以产生用于新电路设计的优化的设计网表。优化的设计网表具有对于实体模拟电路的功率、性能以及面积特性的一组分析。网表是电子电路的连接的描述。网表是界定各种电子组件和那些组件之间的节点连接的列表。新电路设计可为基于输入到系统100中的RTL设计的优化的设计。通过系统100输出的网表还包含优化的功率、性能以及面积(PPA)特征。PPA分析用于优化设计,因为电路设计的功率、性能以及面积中的每一个都是设计不可或缺的方面。PPA分析在电路设计期间被使用。

图2是根据本揭露的各种实施例的用于分析和提取来自跨各种技术尺寸(例如,5纳米、7纳米、10纳米、12纳米、16纳米、28纳米等)的RAM配置和寄存器堆的数据的另一示例性系统200的框图。系统200包含转换模块210、平面布局图(Floor Plan)映射模块220、模拟模块230以及分析模块240。转换模块210接收如图1中所描述的寄存器传输级代码(RTL)。寄存器传输级代码是硬件描述语言内使用的软件代码。可使用寄存器传输级代码来描述实体电路,所述寄存器传输级代码描述硬寄存器之间的数字信号流以及由实体电路的组件对数字信号执行的逻辑操作(例如,AND、NAND、OR、NOR)。转换模块210存取所述电路逻辑行为的寄存器传输级代码描述。转换模型210接着将寄存器传输级代码转换成用于多种类型组件(例如,CPU、GPU、ML-NPU)的一组结构上界定的电路设计(例如,与(AND)门、与非(NAND)电路、或(OR)门、或非(NOR)电路)以及特征尺寸技术(例如,5纳米、7纳米、10纳米、12纳米、16纳米、28纳米等)。平面布局图映射模块220存取一组结构上界定的电路设计,并将所述一组结构上界定的电路设计转换成一组平面布局图。平面布局图界定电路设计内的电子组件以及所述组件在特定区域(例如,底层)中的实体安置。模拟模块230存取一组平面布局图并针对每一平面布局图创建可模拟的电路。分析模块240存取实体模拟电路并扫描实体模拟电路的一系列操作条件,以产生具有对于实体模拟电路的功率、性能以及面积特性的一组分析的优化的设计网表。分析模块240还针对多个实体模拟电路同时并行(例如,同时)扫描一系列操作条件(例如,各种输入电压、例如高温/低温、高湿度/低湿度等各种环境)。

图3是根据本揭露的各种实施例的用于分析和提取来自跨各种技术尺寸(例如,5纳米、7纳米、10纳米、12纳米、16纳米、28纳米等)的RAM配置和寄存器堆的数据的另一示例性系统300的框图。与图2的系统200类似,系统300可包含转换模块210、平面布局图映射模块220、模拟模块230以及分析模块240。另外,系统可包含分类模块310、显示模块320、电路设计模块330、合成模块340以及网表创建模块350中的一或多个。

分类模块310存取分析并通过功率、性能以及面积特性产生一组实体模拟电路的分类列表,所述功率、性能以及面积特性界定电路的功耗、性能(也就是电路操作的频率)以及电路所占用的面积。这些特性可基于功率、性能以及面积值被分类。显示模块320存取实体模拟电路的分类列表并在图形用户界面上显示实体模拟电路的分类列表。电路设计模块330存取一组结构上界定的电路设计,并将结构上所界定的电路设计转换成用于功率、性能以及面积特性的多简档配置(multiple profiled configurations)的合成的一组文件列表(filelist)。文件列表界定电路的组件以及组件之间的互连点。合成模块340存取一组文件列表,并使用设计编译器将一组文件列表合成为一组逻辑门配置。电路的合成包含将寄存器传输级代码翻译成通用布尔模型(Boolean model)。可在逻辑电平处优化所述布尔模型以将多个操作组合成更简单的操作。举例来说,组件可被重新布置、组合以及/或再组合成不同组件以致力于减少操作时间以及电路内的总体组件的数目。另外,优化可包含组件的连续映射,其中可在单元内吸收环绕连续单元的逻辑以节省面积。设计编译器也可执行各种优化操作,例如去除不具有输出端口连接的逻辑、去除冗余组件(例如,如两个连续反相器)及/或传播常量以减少电路内的总体逻辑组件。网表创建模块350存取一组逻辑门配置并将一组逻辑门配置转换成将由模拟模块230使用的一组网表。逻辑门配置含有界定组件互连的逻辑示意图。这些逻辑门配置可翻译成配置内的节点、配置内的组件以及其互连的文本表示。此文本表示为网表。

图4是示出根据本揭露的各种实施例的合成网表的产生的示例性框图400。文件列表(例如,描述电路逻辑行为的RTL设计-界定电路的逻辑行为的软件代码)可涉及多种技术,例如中央处理单元(central processing unit;CPU)(例如,CPU-IP1 402)、图形处理单元(graphical processing unit;GPU)(例如,GPU-IP1)、机器学习网络处理器(machinelearning network processor;ML-NPU)(例如,ML-NPU-IP1)等。每一组文件列表可包含与不同模块设计相关联的一或多个文件列表,如图6至图7中更详细地描述。存储器尺寸提取器410(例如,合成模块340)处理给定组网表以产生对应于每一组的逻辑门配置,所述逻辑门配置界定被评估的给定存储器单元的尺寸。举例来说,逻辑门配置422(例如,config.CPU)对应于CPU-IP1文件列表402。存储器尺寸提取器410还包含追踪器412。追踪器412产生与对应于半导体装置的RTL设计的至少一部分相关联的行为信息。举例来说,此行为信息可包含装置尺寸(例如,字线的数目和位线的数目)。类似地,逻辑门配置424(例如,config.GPU)对应于GPU-IP1文件列表404。逻辑门配置426(例如,config.ML-NPU)对应于ML-NPU-IP1文件列表406。如先前详细描述,逻辑门配置例如使用如单端口(single-port;SP)静态随机存取存储器(static random access memory;SRAM)431、双端口SRAM 432、复式端口(dual-port;DP)SRAM 433、1P RF组件437、2P RF组件434以及任何其它类型的寄存器编译器436的寄存器编译器被编译。这些编译配置接着通过包装器440来被翻译成对应于输入文件列表(例如,文件列表402、文件列表404、文件列表406)的网表。包装器是被界定以包封经包装的代码的软件,使得经包装的代码的代码复杂度对另一界面连接软件组件不可见。实际上,包装器自身含有更简单的代码,所述代码创建与所述另一软件组件的界面从而简化两个软件组件之间的互动。举例来说,两个软件组件可在具有彼此不兼容的不同类型的软件代码时使用包装器。举例来说,网表CPU-IP1 452与文件列表CPU-IP1 402对应。网表GPU-IP2 454与文件列表GPU-IP1 404对应。网表MP-NPU-IP1 456与ML-NPU-IP1 406对应。这些网表用以使用组件的自动安置和/或信号的路由来产生优化的电路设计(例如,区块460)。优化的网表被传输回到编译器且将其存储以使得其可用于将来的电路布局中。

图5是示出根据本揭露的各种实施例的合成CPU网表的产生的示例性框图500。在此实例中,一组文件列表对应于N个模块(例如,文件列表501、文件列表502、文件列表503、文件列表504、文件列表505等)。每一文件列表包含与所述特定模块相关联的特定行为逻辑。使用寄存器编译器或触发器编译器520将一组文件列表一起编译成基于技术尺寸(例如,5纳米、7纳米、16纳米等)的分组。编译用于产生用于布局中的SRAM块的布局。每一编译包含所有实体存储器配置以及与输入文件列表501、文件列表502、文件列表503、文件列表504、文件列表505相关联的PPA配置。换句话说,一起编译跨各种技术尺寸(例如,5纳米、7纳米、16纳米等)的具有一个字线和一个位线(例如文件列表502的模块-1)的所有模块。类似地,跨各种技术尺寸(例如,5纳米、7纳米、16纳米等)的具有两个字线和两个位线(例如文件列表052的模块-2)的所有模块一起被编译。针对跨所有各种技术尺寸(例如,5纳米、7纳米、16纳米等)的所有模块继续此操作。PPA简档器针对每一技术尺寸(例如,5纳米、7纳米、16纳米等)存储的编译(例如,编译511、编译512、编译513、编译514)到逻辑门配置进行评估。在图6中更详细地描述PPA分析。寄存器编译器520设定可存储于寄存器触发器存储515中。编译511、编译512、编译513、编译514随着寄存器触发器存储515可被包装和编译以产生具有包装的PPA简档的对应网表(例如,CPU网表521、CPU网表522、CPU网表523、CPU网表524、CPU网表525),其界定各种模块的功率、性能以及面积特性。包装器是被界定以包封经包装的代码的软件,使得经包装的代码的代码复杂度对另一界面连接软件组件不可见。实际上,包装器自身含有更简单的代码,所述代码创建与所述另一软件组件的界面从而简化两个软件组件之间的互动。举例来说,可在两个软件组件具有彼此不兼容的不同类型的软件代码时使用包装器。在图5中示出的实施例的实例中,PPA简档界定与不同模块尺寸(例如,一个字线/位线、两个字线/位线等)关联的特定功率、性能以及面积需求。在一些实施例中,项目用户界定的配置器可为待优化的电路设置特定尺寸界定(例如,用户界定530)。换句话说,用户可经由用户输入来设置电路的特定尺寸。

图6是示出PPA分析的示例性图解600。使用PPA分析器评估各种文件列表以同时增加性能、维持低功耗且最小化装置面积。通过三角测量与功率(例如,sp、Ip)、面积(例如,udh)以及性能(例如,hs)相关联的常量来执行这些计算。这些常量界定由电子装置消耗的功率,电子装置组件占据的面积,以及操作电子装置需要的时钟频率(例如,性能)。三角测量是测量常量(例如,图解600上所示出的点)中的每一个之间的距离的工艺。最终目标是使功率常量sp、功率常量Ip以及面积常量udh处于其最低可能值而不牺牲电路性能hs。所有这些三个度量值(例如,功率、面积、性能)是相互依存的,因此修改这些值中的一个会影响另外两个。

图7是示出根据本揭露的各种实施例的合成ML网表的产生的示例性框图700。在此实例中,一组文件列表对应于N个模块(例如,文件列表701、文件列表702、文件列表703、文件列表704、文件列表705等)。每一文件列表包含与所述特定模块相关联的特定行为逻辑。文件列表701描述具有一个字线和一个位线的第一模块(例如,模块-1)。文件列表702描述具有两个字线和两个位线的第二模块(例如,模块-2)。文件列表703描述具有三个字线和三个位线的第三模块(例如,模块-3)。文件列表704描述具有至少四个字线和至少四个位线的较小RAM。文件列表705描述具有任何数目(例如,N)字线和任何数目(例如,N)位线的第N模块。如在图5中详细描述,处理文件列表701、文件列表702、文件列表703、文件列表704、文件列表705,且产生具有包装的PPA简档的对应网表(例如,ML网表721、ML网表722、ML网表723、ML网表724、ML网表725)。

图8是示出根据本揭露的各种实施例的用于在集成电路上实施的优化电路合成的方法的示例性流程图800。虽然为易于理解在本文中参考先前描述的结构描述图8,但应理解,所述方法还适用于许多其它结构。通过转换模块210输入电路的逻辑行为的寄存器传输级代码描述(例如,步骤810)。使用转换模块210将寄存器传输级代码描述转换成用于多种类型的组件和特征尺寸技术的结构上界定的电路设计(例如,步骤820)。使用平面布局图映射模块220基于结构设计电路产生每一结构上界定的电路设计的平面布局图(例如,步骤830)。针对每一平面布局图创建实体模拟电路以使用模拟模块230产生实体模拟电路(例如,步骤840)。扫描一系列操作条件以使用分析模块240分析每一实体模拟电路的功率、性能以及面积(例如,步骤850)。

图9是示出用于实施本文所描述的各种方面的样本计算装置架构的示例性框图900。总线904可充当与硬件的其它示出的组件互连的信息高速公路。标记为中央处理单元(CPU)的处理系统908(例如,在给定计算机或多个计算机处的一或多个计算机处理器/数据处理器)可进行执行程序所需的计算和逻辑操作。非暂时性处理器可读存储媒体,例如只读存储器(read only memory;ROM)912和随机存取存储器(random access memory;RAM)916可与处理系统908通信,且可包含用于此处指定的操作的一或多个编程指令。任选地,程序指令可存储于非暂时性计算机可读存储媒体上,例如磁盘、光盘、可记录存储装置、快闪存储器或其它实体存储媒体。

在一个实例中,磁盘控制器948可将一或多个可选磁盘驱动器介接到系统总线904。这些磁盘驱动器可为外部或内部CD-ROM、CD-R、CD-RW或DVD,或例如952的固态驱动器,或外部或内部硬盘驱动器956。如先前所指示,这些各种磁盘驱动器952、磁盘驱动器956以及磁盘控制器为任选装置。系统总线904还可包含至少一个通信端口920,以允许与实体连接到计算系统或可通过有线或无线网络从外部获得的外部装置进行通信。在一些情况下,通信端口920包含或以其它方式包括网络界面。

为提供与用户的互动,本文中所描述的主题可在具有显示装置940(例如,阴极射线管(cathode ray tube;CRT)或液晶显示器(liquid crystal display;LCD)监视器)的计算装置上实施,以用于将从总线904获得的信息显示给用户和用户可借以将输入提供到计算机的输入装置932,例如键盘936和/或指向装置(例如鼠标或导航球)和/或触摸屏。其它种类的输入装置932也可用于提供与用户的互动;例如,提供给用户的反馈可以是任何形式的感觉反馈(例如视觉反馈、通过麦克风的听觉反馈或触觉反馈);且来自用户的输入可以任何形式被接收,包含声波、语音或触觉输入。在输入装置932和键盘936中可借助于输入装置界面928耦合到总线904且经由总线904传送信息。例如专用服务器的其它计算装置可省略显示器940和显示界面914、输入装置932、键盘936以及输入装置界面928中的一或多个。

另外,可通过包括可由装置处理子系统执行的程序指令的程序代码在许多不同类型的处理装置上实施本文中所描述的方法和系统。软件程序指令可包含可操作以使处理系统执行本文中所描述的方法和操作的源代码、目标代码、机器代码或任何其它存储数据,且可将所述软件程序指令设置于例如C、C++、JAVA、Perl、Python、Tcl的任何适合的语言或任何其它适合的编程语言中。然而,还可使用其它实施,例如经配置以进行本文中所描述的方法和系统的固件或甚至适当设计的硬件。

系统数据和方法数据(例如,关联、映射、数据输入、数据输出、中间数据结果、最终数据结果等)可存储且实施于一或多个不同类型的计算机实施数据存储器中,例如不同类型的存储装置和程序构建体(例如,RAM、ROM、快闪存储器、平面文件、数据库、程序数据结构、程序变量、IF-THEN(或类似类型)表述构建体等)。应注意,数据结构描述用于在数据库、程序、存储器或由计算机程序使用的其它计算机可读媒体中组织和存储数据的格式。

本文中所描述的计算机组件、软件模块、功能、数据存储装置以及数据结构可彼此直接或间接连接以允许数据由于其操作所需而流动。还应注意,模块或处理器包含但不限于执行软件操作的代码单元,且可例如实施作为代码的子例程单元,或作为代码的软件功能单元,或作为对象(如在面向对象的范式表中),或作为小程序,或实施于计算机脚本语言中,或作为另一类型的计算机代码。软件组件和/或功能性可取决于迫切情况而位于单个计算机上或跨越多个计算机分布。

本文中所描述的各种工艺的使用可提供数个优势。举例来说,主题的使用可缩短ASIC开发进度,因为电路是通过设计自动优化的且无需重新设计的工作最少。本文中所描述的模拟还促进装置验证,而没有与产生和手动测试装置相关联的时间延迟。

在一个实施例中,一种用于在集成电路上实施的优化电路合成的方法包含输入电路的逻辑行为的寄存器传输级代码描述。将寄存器传输级代码描述转换成用于多种类型的组件及特征尺寸技术的结构上界定的电路设计。产生每一结构上界定的电路设计的平面布局图。针对每一平面布局图创建实体模拟电路。扫描一系列操作条件以分析每一实体模拟电路的功率、性能以及面积。

在一些实施例中,计算机实施方法更包括按功率、性能以及面积特性来对实体模拟电路进行分类。

在一些实施例中,计算机实施方法更包括在图形用户界面上显示按功率、性能以及面积特性依次分类的实体模拟电路。

在一些实施例中,计算机实施方法更包括在产生每一结构上界定的电路设计的平面布局图之前,产生文件列表以用于功率、性能以及面积特性的多简档配置的合成。

在一些实施例中,计算机实施方法更包括使用设计编译器将文件列表合成为逻辑门配置。

在一些实施例中,计算机实施方法更包括产生每一逻辑门配置的网表。

在一些实施例中,计算机实施方法扫描一系列操作条件是对多个实体模拟电路同时并行进行。

在另一实施例中,一种用于在集成电路上实施的优化电路合成的计算机实施系统包含转换模块、平面布局图映射模块、模拟模块以及分析模块。转换模块配置成存取电路的行为的寄存器传输级代码描述,并将寄存器传输级代码转换成用于多种类型的组件和特征尺寸技术的一组结构上界定的电路设计。模拟模块配置成存取一组结构上界定的电路设计并针对每一平面布局图创建实体模拟电路。分析模块配置成存取实体模拟电路并扫描实体模拟电路的一系列操作状态,以产生实体模拟电路的功率、性能以及面积特性的一组分析。

在一些实施例中,计算机实施系统更包括分类模块。分类模块配置成存取分析并产生按功率、性能以及面积特性的所述一组实体模拟电路的分类列表。

在一些实施例中,计算机实施系统更包括显示模块。显示模块配置成存取实体模拟电路的分类列表并在图形用户界面上显示实体模拟电路的分类列表。

在一些实施例中,计算机实施系统更包括电路设计模块。电路设计模块配置成存取所述一组结构上界定的电路设计并将结构上界定的电路设计转换成用于功率、性能以及面积特性的多简档配置的合成的一组文件列表。

在一些实施例中,计算机实施系统更包括合成模块。合成模块配置成存取所述一组文件列表并使用设计编译器将所述一组文件列表合成为一组逻辑门配置。

在一些实施例中,计算机实施系统更包括网表创建模块。网表创建模块配置成存取所述一组逻辑门配置并将所述一组逻辑门配置转换成一组网表。

在一些实施例中,分析模块对多个实体模拟电路同时并行扫描一系列操作条件。

在又一实施例中,一种非暂时性计算机可读媒体编码有用于制造集成电路的存储器存储指令,所述指令在被执行时引起各种操作,例如产生每一结构上界定的电路设计的平面布局图。针对每一平面布局图创建实体模拟电路。扫描一系列操作条件以分析每一实体模拟电路的功率、性能以及面积。

在一些实施例中,非暂时性计算机可读媒体包括按功率、性能以及面积特性来对实体模拟电路进行分类的操作。

在一些实施例中,非暂时性计算机可读媒体包括在产生每一结构上界定的电路设计的平面布局图之前,产生文件列表以用于功率、性能以及面积特性的多简档配置的合成的操作。

在一些实施例中,非暂时性计算机可读媒体包括使用设计编译器将文件列表合成为逻辑门配置的操作。

在一些实施例中,非暂时性计算机可读媒体包括产生每一逻辑门配置的网表的操作。

在一些实施例中,所述扫描一系列操作条件是对多个实体模拟电路同时并行进行。

前文概述若干实施例的特征,使得本领域的技术人员可更好地理解本揭露的各方面。本领域的技术人员应了解,其可容易地将本揭露用作设计或修改用于实现本文中所引入的实施例的相同目的和/或达成相同优势的其它工艺和结构的基础。本领域的技术人员还应认识到,此类等效构造并不脱离本揭露的精神和范围,且其可在不脱离本揭露的精神和范围的情况下在本文中进行各种改变、替代以及更改。