半导体器件及其制造方法

文献发布时间:2024-01-17 01:24:51

技术领域

本发明涉及半导体集成电路制造领域,特别涉及一种半导体器件及其的制造方法。

背景技术

随着集成电路工艺线宽的持续缩小和功能密度的持续提升,IC电路中的噪声对于芯片工作性能的影响越来越大。而深沟槽电容(DTC,Deep trench capacitor)作为无源电容器,能够很好的去耦滤波,滤除高频噪声,降低最小电压,对于IC器件提高工作性能有很大的帮助。

参阅图1a~图1c,目前IC器件的制作步骤包括:首先,如图1a~图1b所示,分别制作用于提供深沟槽电容111的第一晶圆11以及用于提供器件结构121的第二晶圆12,第一晶圆11包括第一衬底112和形成于第一衬底112上的第一绝缘介质层113,深沟槽电容111从第一衬底112中延伸至第一衬底112与第一绝缘介质层113之间,第一绝缘介质层113中形成有第一金属互连结构114、与第一金属互连结构114电连接的第一焊盘115、第三金属互连结构117以及与第三金属互连结构117电连接的第三焊盘118,深沟槽电容111中的部分电极板通过第一金属互连结构114电连接至第一焊盘115,深沟槽电容111中的另一部分电极板通过第三金属互连结构117电连接至第三焊盘118,第一衬底112中还形成有导电结构116,且第一金属互连结构114和第三金属互连结构117均单独与一导电结构116电连接(需要说明的是,与第一金属互连结构114电连接的导电结构116未示意出),第二晶圆12包括第二衬底122和形成于第二衬底122上的第二绝缘介质层123,器件结构121形成于第二衬底122中,第二绝缘介质层123中形成有第二金属互连结构124以及与第二金属互连结构124电连接的第二焊盘125,器件结构121通过第二金属互连结构124与第二焊盘125电连接;然后,如图1c所示,将第一晶圆11与第二晶圆12通过微凸块13键合,微凸块13位于第一焊盘115和第二焊盘125之间以及第三焊盘118和第二焊盘125之间,以实现第一焊盘115和第二焊盘125的电连接以及第三焊盘118和第二焊盘125的电连接;然后,在第一衬底112的背面制作通孔插塞结构(未图示)以及与通孔插塞结构电连接的焊盘(未图示),且通孔插塞结构与导电结构116电连接,以将深沟槽电容111和器件结构121引出。

但是,在上述步骤制作的器件中,深沟槽电容与器件结构形成于不同的晶圆中,导致将深沟槽电容和器件结构引出的电路路径长,进而导致去耦效率低。

因此,如何缩短电路路径,以提高去耦效率是目前亟需解决的问题。

发明内容

本发明的目的在于提供一种半导体器件及其制造方法,缩短了将深沟槽电容与器件结构电引出的电路路径,使得去耦效率得到提高;且增大了单位面积集成度。

为实现上述目的,本发明提供了一种半导体器件,包括:

第一基板,所述第一基板包括正面以及与所述正面相背的背面,所述第一基板正面形成有器件结构,所述第一基板背面形成有深沟槽电容;

第一绝缘层、第二绝缘层,分别形成于所述第一基板的正面与背面;

第一互联结构、第二互联结构,所述第一互联结构形成于所述第一绝缘层中,所述第二互联结构形成于所述第二绝缘层中;

插塞结构,形成于所述第一绝缘层中,所述插塞结构的一端通过所述第一互联结构与所述器件结构电连接,所述插塞结构的另一端通过所述第二互联结构与所述深沟槽电容电连接。

可选地,所述插塞结构从所述第一绝缘层延伸至所述第一基板内并贯穿所述第一基板。

可选地,所述插塞结构位于所述第一绝缘层的一端表面与所述第一互联结构中的任一导电层在同一层。

可选地,所述深沟槽电容包括:

堆叠的至少两层导电材料层以及位于相邻两层所述导电材料层之间的介电材料层,共形地形成于所述第一基板背面的深沟槽内,所述导电材料层与所述介电材料层还延伸至所述深沟槽外围的所述第一基板背面;所述导电材料层与所述第一基板之间电性隔离。

可选地,所述半导体器件还包括:

第一焊盘、第二焊盘和第三互联结构,所述第一焊盘和所述第二焊盘形成于所述第二绝缘层远离所述第一基板的一面,所述第一焊盘通过所述第二互联结构与所述深沟槽电容的部分导电材料层和所述插塞结构的另一端电连接;所述第三互联结构形成于所述第二绝缘层中,所述第二焊盘通过所述第三互联结构与所述深沟槽电容的另一部分导电材料层电连接;

钝化层,形成于所述第二绝缘层远离所述第一基板的一面上,且所述钝化层从所述第二绝缘层上延伸至部分所述第一焊盘和部分所述第二焊盘上。

可选地,所述半导体器件还包括第二基板,所述第二基板键合于所述第一绝缘层远离所述第一基板的一面。

本发明还提供一种半导体器件的制造方法,包括:

提供第一基板,所述第一基板包括正面以及与所述正面相背的背面,所述第一基板正面形成有器件结构;

在所述第一基板正面形成第一绝缘层并在所述第一绝缘层中形成第一互联结构与插塞结构,其中,所述插塞结构从所述第一绝缘层延伸至所述第一基板内,所述插塞结构的一端通过所述第一互联结构与所述器件结构电连接;

在所述第一基板背面形成深沟槽电容;

在所述第一基板背面形成第二绝缘层并在所述第二绝缘层中形成第二互联结构,所述第二绝缘层覆盖所述深沟槽电容与所述插塞结构的另一端,所述插塞结构的另一端通过所述第二互联结构与所述深沟槽电容电连接。

可选地,所述插塞结构从所述第一绝缘层延伸至所述第一基板内并贯穿所述第一基板。

可选地,在所述第一绝缘层中形成第一互联结构时,形成所述第一互联结构中的任一导电层时于所述第一绝缘层形成通孔,在所述通孔内填充导电材料形成插塞结构,所述插塞结构位于所述第一绝缘层的一端表面与所述第一互联结构中的任一导电层在同一层。

可选地,在所述第一基板背面形成深沟槽电容之前,所述半导体器件的制造方法还包括:

将所述第一绝缘层与第二基板键合,并从所述第一基板背面去除部分所述第一基板以暴露所述插塞结构的另一端。

可选地,在所述第一基板背面形成深沟槽电容的步骤包括:

形成深沟槽于所述第一基板背面;

在所述深沟槽内共形地形成堆叠的至少两层导电材料层以及位于相邻两层所述导电材料层之间的介电材料层,以形成深沟槽电容,所述导电材料层与所述介电材料层还延伸至所述深沟槽外围的所述第一基板背面;所述导电材料层与所述第一基板之间电性隔离。

可选地,在所述第二绝缘层中形成第二互联结构时,还在所述第二绝缘层中形成第三互联结构;所述半导体器件的制造方法还包括:

形成第一焊盘和第二焊盘于所述第二绝缘层远离所述第一基板的一面,所述第一焊盘通过所述第二互联结构与所述深沟槽电容的部分导电材料层和所述通孔插塞结构的另一端电连接,所述第二焊盘通过所述第三互联结构与所述深沟槽电容的另一部分导电材料层电连接;

形成钝化层于所述第二绝缘层远离所述第一基板的一面,且所述钝化层从所述第二绝缘层上延伸至部分所述第一焊盘和部分所述第二焊盘上。

与现有技术相比,本发明的技术方案具有以下有益效果:

1、本发明的半导体器件,由于包括:第一基板,所述第一基板包括正面以及与所述正面相背的背面,所述第一基板正面形成有器件结构,所述第一基板背面形成有深沟槽电容;第一绝缘层、第二绝缘层,分别形成于所述第一基板的正面与背面;第一互联结构、第二互联结构,所述第一互联结构形成于所述第一绝缘层中,所述第二互联结构形成于所述第二绝缘层中;插塞结构,形成于所述第一绝缘层中,所述插塞结构的一端通过所述第一互联结构与所述器件结构电连接,所述插塞结构的另一端通过所述第二互联结构与所述深沟槽电容电连接,使得缩短了将深沟槽电容与器件结构电引出的电路路径,进而使得去耦效率得到提高;且增大了单位面积集成度。

2、本发明的半导体器件的制造方法,通过提供第一基板,所述第一基板包括正面以及与所述正面相背的背面,所述第一基板正面形成有器件结构;在所述第一基板正面形成第一绝缘层并在所述第一绝缘层中形成第一互联结构与插塞结构,其中,所述插塞结构从所述第一绝缘层延伸至所述第一基板内,所述插塞结构的一端通过所述第一互联结构与所述器件结构电连接;在所述第一基板背面形成深沟槽电容;在所述第一基板背面形成第二绝缘层并在所述第二绝缘层中形成第二互联结构,所述第二绝缘层覆盖所述深沟槽电容与所述插塞结构的另一端,所述插塞结构的另一端通过所述第二互联结构与所述深沟槽电容电连接,使得缩短了将深沟槽电容与器件结构电引出的电路路径,进而使得去耦效率得到提高;且增大了单位面积集成度。

附图说明

图1a~图1c是一种半导体器件的制造方法中的器件示意图;

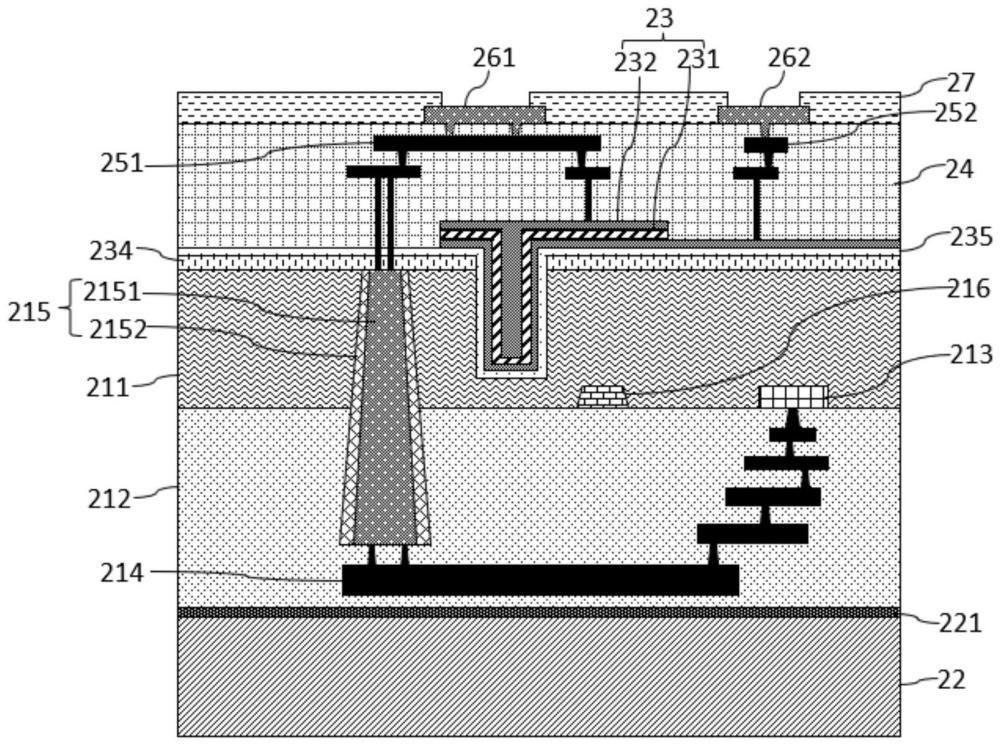

图2是本发明一实施例的半导体器件的纵向剖面示意图;

图3是本发明一实施例的半导体器件的制造方法的流程图;

图4a~图4f是图3所示的半导体器件的制造方法中的器件示意图。

其中,附图1~图4f的附图标记说明如下:

11-第一晶圆;111-深沟槽电容;112-第一衬底;113-第一绝缘介质层;114-第一金属互连结构;115-第一焊盘;116-导电结构;117-第三金属互连结构;118-第三焊盘;12-第二晶圆;121-器件结构;122-第二衬底;123-第二绝缘介质层;124-第二金属互连结构;125-第二焊盘;13-微凸块;211-第一基板;212-第一绝缘层;213-器件结构;214-第一互联结构;215-插塞结构;2151-导电结构;2152-第三绝缘层;216-浅沟槽隔离结构;22-第二基板;221-键合层;23-深沟槽电容;231-介电材料层;232-导电材料层;233-深沟槽;234-硬掩膜层;235-隔离层;24-第二绝缘层;251-第二互联结构;252-第三互联结构;261-第一焊盘;262-第二焊盘;27-钝化层。

具体实施方式

为使本发明的目的、优点和特征更加清楚,以下结合附图对本发明提出的半导体器件及其制造方法作进一步详细说明。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

本发明一实施例提供了一种半导体器件,包括:第一基板,所述第一基板包括正面以及与所述正面相背的背面,所述第一基板正面形成有器件结构,所述第一基板背面形成有深沟槽电容;第一绝缘层、第二绝缘层,分别形成于所述第一基板的正面与背面;第一互联结构、第二互联结构,所述第一互联结构形成于所述第一绝缘层中,所述第二互联结构形成于所述第二绝缘层中;插塞结构,形成于所述第一绝缘层中,所述插塞结构的一端通过所述第一互联结构与所述器件结构电连接,所述插塞结构的另一端通过所述第二互联结构与所述深沟槽电容电连接。

下面参阅图2详细描述本实施例提供的半导体器件。

所述第一基板211包括正面以及与所述正面相背的背面,所述第一基板211正面形成有器件结构213,所述第一基板211背面形成有深沟槽电容23。

所述第一基板211可以包括衬底,或者衬底以及形成在衬底正面和/或背面的单层或多层膜层。衬底材料可以为半导体材料、玻璃、陶瓷或者其他材料,衬底材料为半导体材料时,可以包括但不限于掺杂或未掺杂的硅、掺杂或未掺杂的锗、绝缘体上半导体(SOI)、碳化硅、砷化镓、磷化镓、磷化铟、砷化铟和/或锑化铟、SiGe、GaAsP、AlInAs、AlGaAs、GaInAs、GaInP和/或GaInAsP等或它们的组合。在一些实施例中,第一基板211可以是晶圆或者芯片。

所述第一基板211中还可以形成有浅沟槽隔离结构216等。

所述器件结构213可以是有源器件(例如,晶体管、二极管、三极管等)、无源器件(例如,电容器、电阻器、电感器等)等或它们的组合。器件可以使用适合于形成器件的任何方法来形成。

所述第一基板211的背面可以形成有硬掩膜层234,所述硬掩膜层234中形成有暴露出所述第一基板211背面的开口,所述开口暴露出的所述第一基板211背面形成有深沟槽;所述深沟槽的内壁上可以形成有隔离层235,所述隔离层235还可延伸至所述深沟槽外围的所述第一基板211背面;所述深沟槽电容23包括共形地形成于所述深沟槽内的堆叠的至少两层导电材料层232以及位于相邻两层所述导电材料层232之间的介电材料层231,所述导电材料层232与所述介电材料层231还延伸至所述深沟槽外围的所述隔离层235上,且延伸至所述深沟槽外围的各层导电材料层232均可以部分被暴露出来进行电性引出,所述导电材料层232通过所述隔离层235与所述第一基板211之间电性隔离。

所述第一绝缘层212和/或所述第二绝缘层24,分别形成于第一基板211的正面与背面。若所述第一基板211的背面还形成有所述硬掩膜层234和所述隔离层235,则所述第二绝缘层24形成于所述隔离层235上。

所述第一绝缘层212和/或所述第二绝缘层24可以包括单层或者多层介电层,介电层可以包括但不限于低k介电材料、磷硅酸盐玻璃(PSG)、硼硅酸盐玻璃(BSG)、硼掺杂的磷硅酸盐玻璃(BPSG)、未掺杂的硅酸盐玻璃(USG)、氧化硅、氮化硅、氮氧硅化合物、碳化硅或掺碳二氧化硅等,并且可以使用旋涂、层压、原子层沉积(ALD)、化学气相沉积(CVD)等形成。

所述第一互联结构214形成于所述第一绝缘层212中,所述第二互联结构251形成于所述第二绝缘层24中。

所述第一互联结构214和/或所述第二互联结构251包括多层堆叠的导电层M1至Mt以及连接相邻导电层的导电插塞,导电层M1也可以称为最底部导电层,导电层Mt也可以称为最顶部导电层。第一互联结构214和/或第二互联结构251可以包括导电材料,诸如钨、钴、镍、铜、银、金、铝等或它们的组合。每一导电层对应形成在第一绝缘层212和/或第二绝缘层24对应的介电层内。

所述插塞结构215形成于所述第一绝缘层212中,所述插塞结构215的一端通过所述第一互联结构214与所述器件结构213电连接,所述插塞结构215的另一端通过所述第二互联结构251与所述深沟槽电容23电连接。

在一实施例中,所述插塞结构215的另一端可以从所述第一绝缘层212延伸至所述第一基板211内并刚好贯穿所述第一基板211,所述硬掩膜层234覆盖所述插塞结构215的另一端。在其他实施例中,所述插塞结构215的另一端可以从所述第一绝缘层212延伸至所述第一基板211内但未贯穿所述第一基板211,此时,所述第二互联结构251从所述第二绝缘层24中延伸至所述第一基板211中,以与所述插塞结构215电连接,所述第二互联结构251延伸至所述第一基板211中的部分与所述第一基板211之间绝缘;或者,所述插塞结构215的另一端可以从所述第一绝缘层212延伸至所述第一基板211内并贯穿所述第一基板211且进入所述第二绝缘层24中,以与所述插塞结构215电连接。

所述插塞结构215位于所述第一绝缘层212的一端表面与所述第一互联结构214中的任一导电层在同一层。

所述插塞结构215包括导电结构2151和第三绝缘层2152,所述导电结构2151的一端通过所述第一互联结构214与所述器件结构213电连接,所述导电结构2151的另一端通过所述第二互联结构251与所述深沟槽电容23电连接。并且,以所述插塞结构215的另一端从所述第一绝缘层212延伸至所述第一基板211内并贯穿所述第一基板211为例,所述第一绝缘层212中形成有一通孔(未图示),且通孔延伸至所述第一基板211内并贯穿所述第一基板211,所述导电结构2151填充所述通孔,所述第三绝缘层2152夹于所述导电结构2151与所述通孔的侧壁之间,所述导电结构2151通过所述第三绝缘层2152与所述基底211之间绝缘。

所述半导体器件还可包括第二基板22,所述第二基板22键合于所述第一绝缘层212远离所述第一基板211的一面,或者,所述第二基板22键合于所述第二绝缘层24远离所述第一基板211的一面。

所述第二基板22可以未包含功能结构;或者,所述第二基板22可以包含功能结构,在一些实施例中,所述第二基板22包含的功能结构也可以位于第二基板22的内部和/或边缘的内部和/或表面。

在一些实施例中,所述第二基板22可以是晶圆或者芯片。

所述第二基板22上可以形成有键合层221,通过将所述第一绝缘层212或所述第二绝缘层24与所述键合层221键合来实现所述第一基板211与所述第二基板22的键合。

其中,所述键合层221可以包括覆盖在所述第二基板22上的绝缘层(未图示)以及位于绝缘层中的金属层(未图示),且绝缘层暴露出金属层;所述第一绝缘层212或所述第二绝缘层24中也可以形成有焊盘(未图示),且所述第一绝缘层212或所述第二绝缘层24暴露出焊盘,使得绝缘层与所述第一绝缘层212或所述第二绝缘层24之间键合,绝缘层暴露出的金属层与焊盘之间键合。

所述半导体器件还可包括:第三互联结构252,所述第三互联结构252形成于所述第二绝缘层24中,所述第三互联结构252与所述第二互联结构251之间绝缘;所述第二互联结构251与所述深沟槽电容23的部分导电材料层232电连接,所述第三互联结构252与所述深沟槽电容23的另一部分导电材料层232电连接。

所述半导体器件还包括:

第一焊盘261和第二焊盘262,形成于所述第二绝缘层24远离所述第一基板211的一面,所述第一焊盘261通过所述第二互联结构251与所述深沟槽电容23的部分导电材料层232和所述插塞结构215中的导电结构2151的另一端电连接,所述第二焊盘262通过所述第三互联结构252与所述深沟槽电容23的另一部分导电材料层232电连接;

钝化层27,形成于所述第二绝缘层24远离所述第一基板211的一面上,且所述钝化层27从所述第二绝缘层24上延伸至部分所述第一焊盘261和部分所述第二焊盘262上,即所述钝化层27暴露出部分所述第一焊盘261和部分所述第二焊盘262。

由于所述器件结构213通过所述第一互联结构214与所述插塞结构215的一端实现电连接,所述插塞结构215的另一端通过所述第二互联结构251与所述深沟槽电容23实现电连接,且所述第一焊盘261通过所述第二互联结构251与所述深沟槽电容23的部分导电材料层232和所述插塞结构215实现电连接,使得所述第一焊盘261能够将所述器件结构213和所述深沟槽电容23中的部分导电材料层232电引出;由于所述第二焊盘262通过所述第三互联结构252与所述深沟槽电容23中的另一部分导电材料层232电连接,使得所述第二焊盘262能够将所述深沟槽电容23中的另一部分导电材料层232电引出。

所述第一焊盘261和所述第二焊盘262能够分别与电源的正极和负极连接,且所述器件结构213与所述深沟槽电容23并联。

从上述内容可知,在本发明提供的半导体器件中,由于所述深沟槽电容23和所述器件结构213均形成于所述第一基板211中,且用于将所述深沟槽电容23与所述器件结构213实现电连接的结构(即所述第一互联结构214、所述插塞结构215和所述第二互联结构251)也形成于所述第一基板211上,而未形成于所述第二基板22中,即所述深沟槽电容23、所述器件结构213以及用于将所述深沟槽电容23与所述器件结构213实现电连接的结构均形成于同一基底中,使得与深沟槽电容和器件结构分别位于第一基板和第二基板(即不同基底)中的结构相比,本发明提供的半导体器件缩短了将所述深沟槽电容23与所述器件结构213电引出的电路路径,进而使得去耦效率得到提高。

并且,在本发明提供的半导体器件中,由于所述深沟槽电容23、所述器件结构213分别形成于所述第一基板211正面与背面,充分利用了所述第一基板211有效面积,能够增大单位面积集成度。本发明提供的半导体器件,包括:第一基板,所述第一基板包括正面以及与所述正面相背的背面,所述第一基板正面形成有器件结构,所述第一基板背面形成有深沟槽电容;第一绝缘层、第二绝缘层,分别形成于所述第一基板的正面与背面;第一互联结构、第二互联结构,所述第一互联结构形成于所述第一绝缘层中,所述第二互联结构形成于所述第二绝缘层中;插塞结构,形成于所述第一绝缘层中,所述插塞结构的一端通过所述第一互联结构与所述器件结构电连接,所述插塞结构的另一端通过所述第二互联结构与所述深沟槽电容电连接。本发明的半导体器件缩短了将深沟槽电容与器件结构电引出的电路路径,使得去耦效率得到提高;且增大了单位面积集成度。

本发明一实施例提供一种半导体器件的制造方法,参阅图3,图3是本发明一实施例的半导体器件的制造方法的流程图,所述半导体器件的制造方法包括:

步骤S1,提供第一基板,所述第一基板包括正面以及与所述正面相背的背面,所述第一基板正面形成有器件结构;

步骤S2,在所述第一基板正面形成第一绝缘层并在所述第一绝缘层中形成第一互联结构与插塞结构,其中,所述插塞结构从所述第一绝缘层延伸至所述第一基板内,所述插塞结构的一端通过所述第一互联结构与所述器件结构电连接;

步骤S3,在所述第一基板背面形成深沟槽电容;

步骤S4,在所述第一基板背面形成第二绝缘层并在所述第二绝缘层中形成第二互联结构,所述第二绝缘层覆盖所述深沟槽电容与所述插塞结构的另一端,所述插塞结构的另一端通过所述第二互联结构与所述深沟槽电容电连接。

下面参阅4a~图4f对本实施例提供的半导体器件的制造方法进行详细介绍。

按照步骤S1,如图4a所示,提供第一基板211,所述第一基板211包括正面以及与所述正面相背的背面,所述第一基板211正面形成有器件结构213。

所述第一基板211可以包括衬底,或者衬底以及形成在衬底正面和/或背面的单层或多层膜层。衬底材料可以为半导体材料、玻璃、陶瓷或者其他材料,衬底材料为半导体材料时,可以包括但不限于掺杂或未掺杂的硅、掺杂或未掺杂的锗、绝缘体上半导体(SOI)、碳化硅、砷化镓、磷化镓、磷化铟、砷化铟和/或锑化铟、SiGe、GaAsP、AlInAs、AlGaAs、GaInAs、GaInP和/或GaInAsP等或它们的组合。在一些实施例中,第一基板211可以是晶圆或者芯片。

所述第一基板211中还可以形成有浅沟槽隔离结构216等。

所述器件结构213可以是有源器件(例如,晶体管、二极管等)、无源器件(例如,电容器、电阻器、电感器等)等或它们的组合。器件可以使用适合于形成器件的任何方法来形成。

按照步骤S2,如图4a所示,在所述第一基板211正面形成第一绝缘层212,并在所述第一绝缘层212中形成第一互联结构214与插塞结构215,其中,所述插塞结构215从所述第一绝缘层212延伸至所述第一基板211内,所述插塞结构215的一端通过所述第一互联结构214与所述器件结构213电连接。

所述第一绝缘层212可以包括单层或者多层介电层,介电层可以包括但不限于低k介电材料、磷硅酸盐玻璃(PSG)、硼硅酸盐玻璃(BSG)、硼掺杂的磷硅酸盐玻璃(BPSG)、未掺杂的硅酸盐玻璃(USG)、氧化硅、氮化硅、氮氧硅化合物、碳化硅或掺碳二氧化硅等,并且可以使用旋涂、层压、原子层沉积(ALD)、化学气相沉积(CVD)等形成。

所述第一互联结构214包括多层堆叠的导电层M1至Mt以及连接相邻导电层的导电插塞,导电层M1也可以称为最底部导电层,导电层Mt也可以称为最顶部导电层。第一互联结构214可以包括导电材料,诸如钨、钴、镍、铜、银、金、铝等或它们的组合。每一导电层对应形成在第一绝缘层212对应的介电层内。

在所述第一绝缘层212中形成第一互联结构214时,形成所述第一互联结构214中的任一导电层时于所述第一绝缘层212中形成通孔,且通孔延伸至所述第一基板211中,在所述通孔内填充导电材料形成插塞结构215,所述插塞结构215位于所述第一绝缘层212的一端表面与所述第一互联结构214中的任一导电层在同一层。

并且,在所述通孔内填充导电材料之前,先在所述通孔的内壁形成第三绝缘层2152,填充的导电材料作为所述插塞结构215的导电结构2151,所述导电结构2151通过所述第三绝缘层2152与所述第一基板211之间绝缘,所述导电结构2151的一端通过所述第一互联结构214与所述器件结构213电连接。

在一实施例中,如图4b所示,在后续所述第一基板211背面形成深沟槽电容23以及第二绝缘层24之前,所述半导体器件的制造方法还可包括:将所述第一绝缘层212与第二基板22键合;或者,在后续所述第一基板211背面形成第二绝缘层24和第二互联结构251之后,所述半导体器件的制造方法还可包括:将所述第二绝缘层24与第二基板22键合。

所述第二基板22可以未包含功能结构;或者,所述第二基板22可以包含功能结构,在一些实施例中,所述第二基板22包含的功能结构也可以位于第二基板22的内部和/或边缘的内部和/或表面。

在一些实施例中,所述第二基板22可以是晶圆或者芯片。

所述第二基板22上可以形成有键合层221,通过将所述第一绝缘层212或所述第二绝缘层24与所述键合层221键合来实现所述第一基板211与所述第二基板22的键合。

其中,所述键合层221可以包括覆盖在所述第二基板22上的绝缘层(未图示)以及位于绝缘层中的金属层(未图示),且绝缘层暴露出金属层;所述第一绝缘层212或所述第二绝缘层24中也可以形成有焊盘(未图示),且所述第一绝缘层212或所述第二绝缘层24暴露出焊盘,使得绝缘层与所述第一绝缘层212或所述第二绝缘层24之间键合,绝缘层暴露出的金属层与焊盘之间键合。

并且,键合方法可以包括熔融键合、热压键合、低温真空键合、阳极键合、共晶键合或者混合键合等。

并且,在将所述第一绝缘层212与所述第二基板22键合之前或之后,从所述第一基板211背面去除部分所述第一基板211以暴露所述插塞结构215的另一端的表面,以使得所述插塞结构215从所述第一绝缘层212延伸至所述第一基板211内并刚好贯穿所述第一基板211,如图4c所示;或者,从所述第一基板211背面去除部分所述第一基板211以暴露所述插塞结构215的另一端的表面和侧壁,以使得所述插塞结构215从所述第一绝缘层212延伸至所述第一基板211内并从所述第一基板211内贯穿出来,即所述插塞结构215的另一端凸出于所述第一基板211。其中,所述插塞结构215的另一端的所述第三绝缘层2152也被去除,以暴露出所述导电结构2151。

在其他实施例中,从所述第一基板211背面去除部分所述第一基板211之后可以未暴露出所述插塞结构215的另一端,或者,未从所述第一基板211背面去除部分所述第一基板211,使得所述插塞结构215的另一端从所述第一绝缘层212延伸至所述第一基板211内但未贯穿所述第一基板211。

其中,可以采用化学机械研磨工艺或刻蚀工艺去除部分所述第一基板211。

按照步骤S3,如图4d~图4e所示,在所述第一基板211背面形成深沟槽电容23。

在所述第一基板211背面形成深沟槽电容23的步骤可以包括:首先,如图4d所示,形成硬掩膜层234于所述第一基板211背面,所述硬掩膜层234覆盖所述插塞结构215的另一端,所述硬掩膜层234中形成有暴露出所述第一基板211背面的开口;然后,如图4d所示,以所述硬掩膜层234为掩膜,刻蚀所述开口暴露出的所述第一基板211背面,以形成深沟槽233于所述第一基板211背面;然后,如图4e所示,在所述深沟槽233内共形地形成隔离层235,所述隔离层235还延伸至所述深沟槽233外围的所述硬掩膜层234上;然后,如图4e所示,在所述深沟槽233内共形地形成堆叠的至少两层导电材料层232以及位于相邻两层所述导电材料层232之间的介电材料层231,以形成深沟槽电容23,所述导电材料层232与所述介电材料层231还延伸至所述深沟槽233外围的所述隔离层235上,所述导电材料层232通过所述隔离层235与所述第一基板211之间电性隔离;然后,如图4e所示,采用刻蚀工艺刻蚀延伸至所述深沟槽233外围的所述导电材料层232和所述介电材料层231,以暴露出延伸至所述深沟槽233外围的各层导电材料层232。

按照步骤S4,如图4f所示,在所述第一基板211背面形成第二绝缘层24并在所述第二绝缘层24中形成第二互联结构251,所述第二绝缘层24覆盖所述深沟槽电容23与所述插塞结构215的另一端,所述插塞结构215的另一端通过所述第二互联结构251与所述深沟槽电容23电连接。

若所述第一基板211的背面还形成有所述硬掩膜层234和所述隔离层235,则所述第二绝缘层24形成于所述隔离层235上。

所述第二绝缘层24可以包括单层或者多层介电层,介电层可以包括但不限于低k介电材料、磷硅酸盐玻璃(PSG)、硼硅酸盐玻璃(BSG)、硼掺杂的磷硅酸盐玻璃(BPSG)、未掺杂的硅酸盐玻璃(USG)、氧化硅、氮化硅、氮氧硅化合物、碳化硅或掺碳二氧化硅等,并且可以使用旋涂、层压、原子层沉积(ALD)、化学气相沉积(CVD)等形成。

当所述插塞结构215的另一端从所述第一绝缘层212延伸至所述第一基板211内并刚好贯穿所述第一基板211或所述插塞结构215的另一端凸出于所述第一基板211时,所述第二互联结构251可以贯穿所述第二绝缘层24、所述隔离层235和所述硬掩膜层234后与所述插塞结构215中的导电结构2151电连接;当所述插塞结构215的另一端从所述第一绝缘层212延伸至所述第一基板211内但未贯穿所述第一基板211时,所述第二互联结构251可以贯穿所述第二绝缘层24、所述隔离层235和所述硬掩膜层234后并延伸至所述第一基板211内与所述插塞结构215中的导电结构2151电连接。

另外,在所述第二绝缘层24中形成第二互联结构251时,还在所述第二绝缘层24中形成第三互联结构252,所述第三互联结构252与所述第二互联结构251之间绝缘;所述第二互联结构251与所述深沟槽电容23的部分导电材料层232电连接,所述第三互联结构252与所述深沟槽电容23的另一部分导电材料层232电连接。

所述第二互联结构251和/或所述第三互联结构252包括多层堆叠的导电层M1至Mt以及连接相邻导电层的导电插塞,导电层M1也可以称为最底部导电层,导电层Mt也可以称为最顶部导电层。所述第二互联结构251和/或所述第三互联结构252可以包括导电材料,诸如钨、钴、镍、铜、银、金、铝等或它们的组合。每一导电层对应形成在第二绝缘层24对应的介电层内。

所述半导体器件的制造方法还可包括:

形成第一焊盘261和第二焊盘262于所述第二绝缘层24远离所述第一基板211的一面,所述第一焊盘261通过所述第二互联结构251与所述深沟槽电容23的部分导电材料层232和所述插塞结构215中的导电结构2151的另一端电连接,所述第二焊盘262通过所述第三互联结构252与所述深沟槽电容23的另一部分导电材料层232电连接。

形成钝化层27于所述第二绝缘层24远离所述第一基板211的一面上,且所述钝化层27从所述第二绝缘层24上延伸至部分所述第一焊盘261和部分所述第二焊盘262上,即所述钝化层27暴露出部分所述第一焊盘261和部分所述第二焊盘262。

由于所述器件结构213通过所述第一互联结构214与所述插塞结构215实现电连接,所述插塞结构215的另一端通过所述第二互联结构251与所述深沟槽电容23实现电连接,且所述第一焊盘261通过所述第二互联结构251与所述深沟槽电容23的部分导电材料层232和所述插塞结构215实现电连接,使得所述第一焊盘261能够将所述器件结构213和所述深沟槽电容23中的部分导电材料层232电引出;由于所述第二焊盘262通过所述第三互联结构252与所述深沟槽电容23的另一部分导电材料层232电连接,使得所述第二焊盘262能够将所述深沟槽电容23中的另一部分导电材料层232电引出。

所述第一焊盘261和所述第二焊盘262能够分别与电源的正极和负极连接,且所述器件结构213与所述深沟槽电容23并联。

从上述内容可知,在本发明提供的半导体器件的制造方法中,由于所述深沟槽电容23和所述器件结构213均形成于所述第一基板211中,且用于将所述深沟槽电容23与所述器件结构213实现电连接的结构(即所述第一互联结构214、所述插塞结构215和所述第二互联结构251)也形成于所述第一基板211上,而未形成于所述第二基板22中,即所述深沟槽电容23、所述器件结构213以及用于将所述深沟槽电容23与所述器件结构213实现电连接的结构均形成于同一基底中,使得与将深沟槽电容和器件结构分别形成于第一基板和第二基板(即不同基底)中相比,本发明提供的半导体器件的制造方法缩短了将所述深沟槽电容23与所述器件结构213电引出的电路路径,进而使得去耦效率得到提高。

并且,在本发明提供的半导体器件的制造方法中,由于所述深沟槽电容23、所述器件结构213分别形成于所述第一基板211正面与背面,充分利用了所述第一基板211有效面积,能够增大单位面积集成度。本发明提供的半导体器件的制造方法,包括:提供第一基板,所述第一基板包括正面以及与所述正面相背的背面,所述第一基板正面形成有器件结构;在所述第一基板正面形成第一绝缘层并在所述第一绝缘层中形成第一互联结构与插塞结构,其中,所述插塞结构从所述第一绝缘层延伸至所述第一基板内,所述插塞结构的一端通过所述第一互联结构与所述器件结构电连接;在所述第一基板背面形成深沟槽电容;在所述第一基板背面形成第二绝缘层并在所述第二绝缘层中形成第二互联结构,所述第二绝缘层覆盖所述深沟槽电容与所述插塞结构的另一端,所述插塞结构的另一端通过所述第二互联结构与所述深沟槽电容电连接。本发明的半导体器件的制造方法缩短了将深沟槽电容与器件结构电引出的电路路径,使得去耦效率得到提高;且增大了单位面积集成度。

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

- 半导体器件、半导体封装及制造半导体器件的方法

- 制造半导体器件的方法和半导体器件

- 制造半导体器件的方法和半导体器件

- 一种半导体器件的制造方法及半导体器件

- 半导体器件的制造方法及半导体器件

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置