用于半导体缺陷引导预烧及系统级测试的系统及方法

文献发布时间:2024-04-18 19:48:15

本申请案主张2021年6月7日申请的序列号为63/197,509的美国临时申请案的权利,所述美国临时申请案的全部内容以引用方式并入本文中。

技术领域

本公开大体上涉及半导体装置,且更特定来说,涉及用于半导体缺陷引导预烧及系统级测试的系统及方法。

背景技术

半导体装置的制造通常可需要数百或数千个处理步骤来形成功能装置。在这些处理步骤的过程中,可执行各种特性化测量(例如检查及/或计测量量)以识别缺陷及/或监测装置上的各种参数。可执行电测试来代替或补充各种特性化测量以验证或评估装置的功能。然而,尽管一些所检测缺陷及计量误差可非常重要以至清楚地指示装置故障,但较小变化可导致装置在暴露于工作环境之后出现早期可靠性故障。半导体装置的规避风险用户现正在寻找十亿分之几(PPB)范围内的故障率,超过当前百万分之几(PPM)级别。随着应用中对半导体装置的需求继续增加,评估半导体裸片的可靠性是满足要求的关键。

发明内容

根据本公开的一或多个实施例,公开一种系统。在一个说明性实施例中,所述系统包含通信地耦合到线内缺陷部分平均测试(I-PAT)子系统的缺陷引导安置控制器。在另一说明性实施例中,所述缺陷引导安置控制器包含一或多个处理器及存储器。在另一说明性实施例中,所述存储器经配置以存储一组程序指令。在另一说明性实施例中,所述一或多个处理器经配置以执行使所述一或多个处理器从所述I-PAT子系统接收多个线内缺陷部分平均测试(I-PAT)分数的程序指令。在另一说明性实施例中,所述多个I-PAT分数由所述I-PAT子系统基于多个半导体裸片的半导体裸片数据产生。在另一说明性实施例中,所述半导体裸片数据包含所述多个半导体裸片的特性化测量。在另一说明性实施例中,所述多个I-PAT分数中的每一I-PAT分数表示由所述I-PAT子系统基于所述多个半导体裸片中的对应半导体裸片的特性化测量所确定的缺陷率。在另一说明性实施例中,所述一或多个处理器经配置以执行使所述一或多个处理器在动态决策过程期间将一或多个规则应用于所述多个I-PAT分数的程序指令。在另一说明性实施例中,所述一或多个处理器经配置以执行使所述一或多个处理器基于所述动态决策过程为所述多个半导体裸片中的至少一个半导体裸片产生关于预烧或系统级测试(SLT)中的至少一者的一或多个缺陷引导安置的程序指令。

根据本公开的一或多个实施例,公开一种方法。在一个说明性实施例中,所述方法可包含(但不限于)经由缺陷引导安置控制器从线内缺陷部分平均测试(I-PAT)子系统接收多个线内缺陷部分平均测试(I-PAT)分数。在另一说明性实施例中,所述多个I-PAT分数由所述I-PAT子系统基于多个半导体裸片的半导体裸片数据产生。在另一说明性实施例中,所述半导体裸片数据包含所述多个半导体裸片的特性化测量。在另一说明性实施例中,所述多个I-PAT分数中的每一I-PAT分数表示由所述I-PAT子系统基于所述多个半导体裸片中的对应半导体裸片的特性化测量所确定的缺陷率。在另一说明性实施例中,所述方法可包含(但不限于)经由所述缺陷引导安置控制器在动态决策过程期间将一或多个规则应用于所述多个I-PAT分数。在另一说明性实施例中,所述方法可包含(但不限于)经由所述缺陷引导安置控制器基于所述动态决策过程为所述多个半导体裸片中的至少一个半导体裸片产生关于预烧或系统级测试(SLT)中的至少一者的一或多个缺陷引导安置。

根据本公开的一或多个实施例,公开一种系统。在一个说明性实施例中,所述系统包含线内缺陷部分平均测试(I-PAT)子系统,其中所述I-PAT子系统经配置以接收多个半导体裸片的半导体裸片数据且基于所述半导体裸片数据而产生多个线内缺陷部分平均测试(I-PAT)分数。在另一说明性实施例中,所述半导体裸片数据包含所述多个半导体裸片的特性化测量。在另一说明性实施例中,所述多个I-PAT分数中的每一I-PAT分数表示由所述I-PAT子系统基于所述多个半导体裸片中的对应半导体裸片的特性化测量所确定的缺陷率。在另一说明性实施例中,所述系统包含通信地耦合到所述I-PAT子系统的缺陷引导安置控制器。在另一说明性实施例中,所述缺陷引导安置控制器包含一或多个处理器及存储器。在另一说明性实施例中,所述存储器经配置以存储一组程序指令。在另一说明性实施例中,所述一或多个处理器经配置以执行使所述一或多个处理器从所述I-PAT子系统接收所述多个I-PAT分数的程序指令。在另一说明性实施例中,所述一或多个处理器经配置以执行使所述一或多个处理器在动态决策过程期间将一或多个规则应用于所述多个I-PAT分数的程序指令。在另一说明性实施例中,所述一或多个处理器经配置以执行使所述一或多个处理器基于所述动态决策过程为所述多个半导体裸片中的至少一个半导体裸片产生关于预烧或系统级测试(SLT)中的至少一者的一或多个缺陷引导安置的程序指令。

应理解,前述一般描述及以下详细描述两者仅是示范性及解释性,而不必限制所主张的本发明。经并入并构成说明书的部分、本发明的说明性实施例并与一般描述一起的附图用于解释本发明的原理。

附图说明

所属领域的技术人员可通过参考附图更佳理解本公开的各种优点,其中:

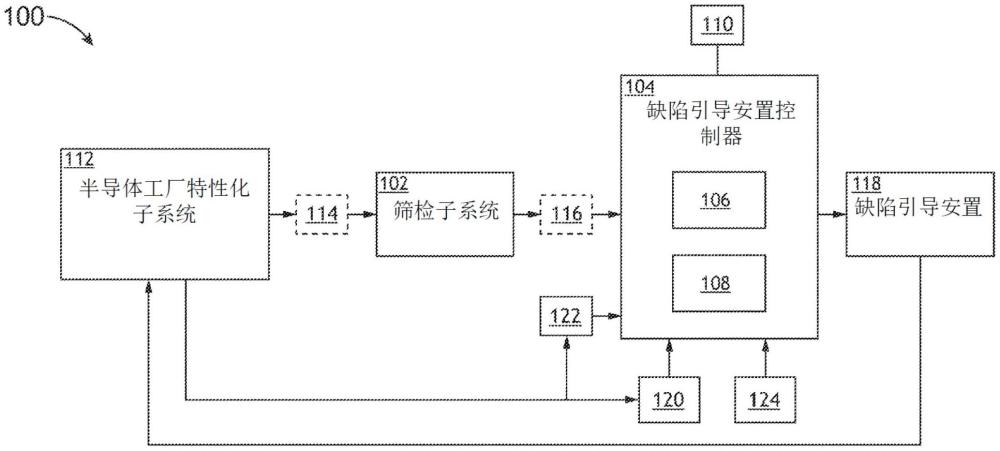

图1是根据本公开的一或多个实施例的用于半导体缺陷引导预烧及系统级测试(SLT)的系统的框图;

图2是根据本公开的一或多个实施例的用于半导体缺陷引导预烧及系统级测试(SLT)的系统的概念图;

图3是说明根据本公开的一或多个实施例的用于半导体缺陷引导预烧及系统级测试(SLT)的方法中执行的步骤的流程图;

图4A是根据本公开的一或多个实施例的用于制造、特性化及/或测试半导体装置的系统的框图;

图4B是根据本公开的一或多个实施例的用于制造、特性化及/或测试半导体装置的系统的框图;及

图5是说明根据本公开的一或多个实施例的用于制造、特性化及/或测试半导体装置的方法中执行的步骤的流程图。

具体实施方式

现将详细参考在附图中说明的所公开的目标物。本公开已针对特定实施例及其特定特征进行具体展示及描述。本文中所阐述的实施例被认为是说明性而非限制性。所属领域的一般技术人员应容易明白,在不脱离本公开的精神及范围的情况下,可在形式及细节上做出各种改变及修改。

半导体装置的制造通常可需要数百或数千个处理步骤来形成功能装置。在这些处理步骤的过程中,可执行各种特性化测量(例如检查及/或计测量量)以识别缺陷及/或监测装置上的各种参数。可执行电气测试来代替或补充各种特性化测量以验证或评估装置的功能。

然而,尽管一些所检测缺陷及计量误差可如此显著以致于清楚地指示装置故障,但较小变化可导致装置在暴露于工作环境之后的早期可靠性故障。制造过程期间出现的缺陷可对现场装置的性能具有广泛影响。例如,在设计内已知或未知位置中发生的“致命”缺陷可导致立即装置故障。例如,未知位置中的致命缺陷可特别成问题,因为其容易受测试间隙中的可靠性逃逸的影响,其中半导体装置在处理之后可在功能上失效,但由于测试限制,装置制造商无法进行此安置。举另一实例,轻微缺陷贯穿装置寿命可对装置的性能几乎没有影响或没有影响。举另一实例,称为潜在可靠性缺陷(LRD)的类缺陷可不导致制造/测试期间的故障或可不导致操作期间的立即装置故障,但可导致装置在在一工作环境中使用时的执行期间的早期故障。本文中应注意,为本公开的目的,术语“制造过程(manufacturingprocess)”及“制造过程(fabrication process)”连同术语的相应变体(例如“制造线(manufacturing line)”及“制造线(fabrication line)”及其类似者)可被认为是等同的。

半导体装置的风险规避用户(例如,在汽车、军事、航空、工业及/或医疗应用中)可需要十亿分之一(PPB)范围内的故障率,超过当前百万分之一(PPM)级别。例如,在任务或安全关键功能(例如汽车、军事、航空、工业及/或医疗应用)中的半导体装置比消费者装置将遵守更高质量及可靠性标准。随着汽车、军事、航空、工业及/或医疗应用对半导体装置的需求不断增加,评估半导体裸片的可靠性是满足要求的关键。

半导体装置供货商已尝试最大化常规自动测试设备(ATE)测试器上的可用测试覆盖率,以努力达到质量目标并识别有风险半导体裸片。然而,测试覆盖率差距、测试故障模型限制或缺陷及/或LRD可仍允许不令人满意级别的低可靠性裸片逃逸到供应链中。

为解决不令人满意的逃逸级别,可增添“预烧”步骤以通过振动、温度(例如热或冷)、湿度及/或半导体装置规范外部的范围的电气条件对封装裸片施加压力,以努力启动存在的任何潜在故障。然而,除缓慢及昂贵之外,预烧步骤还提供潜在损坏其它健康裸片的不期望风险。另外,系统级测试(SLT)可用于解决不令人满意的逃逸级别,其可与预烧个别发生、循序发生、共同发生或同时发生。SLT涉及将半导体裸片插入到仿真操作芯片的真实功能的测试器中,以验证其内部时序路径及功能接口。此模拟可公开在ATE测试器上未发现的故障。然而,一个权衡是较ATE测试器的测试时间为几秒钟,SLT测试时间通常长达几分钟,使得其非常昂贵且缓慢。本文中应注意,SLT的描述可在颇联一世(I.Polian)等人,“探索系统级测试的奥秘(Exploring the Mysteries of System-Level Test)”,2020年IEEE第29届亚洲测试研讨会(ATS),2020,第1到6页,doi:10.1109/ATS49688.2020.9301557中找到。另外,本文中应注意,SLT的描述可在何晨(H.H.Chen),“除了结构测试,对系统级测试的需求也在不断增加(Beyond structural test,the rising need for system-leveltest)”,2018VLSI设计、自动化与测试国际研讨会(VLSI-DAT),2018,第1到4页,doi:10.1109/VLSI-DAT.2018.8373238中找到。

处于质量关键角色的半导体装置可在晶片分类期间及在切割及封装之后的最终测试中再次进行广泛电气测试。此生产阶段面临通过缩短测试时间来减少质量逃逸及降低成本两者的冲突压力。

例如,已知测试技术可主要依赖于来自晶片分类的初步电气数据或电气测试趋势的统计预测及来自先前批次及相邻裸片的良率结果以形成测试策略。然而,制造过程控制信息太少而无法在一个别装置级别形成测试策略,因为采样仅涵盖1到2%的生产材料。另外,已知测试技术缺乏帮助风险预测的裸片级制造缺陷及/或计量信息。进一步言之,仅依赖电气晶片分类数据可忽视LRD在成形缺陷引导测试中的潜在存在,因为未启动LRD在电子测试中是不可见的。进一步言之,基于统计的预测算法缺乏关于正在测试的半导体裸片的出处数据,且可错过由局部制造偏差引起的个别异常值。进一步言之,基于将测试集仅削减为电气测试的历史反馈回路的预测算法可无法忽视制造过程偏差的不可预测本质及其可产生的不预期故障。这些缺点在PPB测试环境中尤其成问题,因为其可产生不可接受的风险。

在一些例子中,半导体裸片供货商传统上主要依赖于电气测试数据及/或统计采样来决定哪些半导体裸片群体应经历预烧及/或SLT。然而,先前方法缺乏适当制造裸片级缺陷或跨多个层加总的计量异常数据以在选择进行预烧及/或SLT的群体时辅助风险预测。

举另一实例,主要依赖于电气测试数据来选择用于预烧及/或SLT的裸片群体可忽视在ATE测试中没有有效体现的可靠性机制,导致由测试覆盖率间隙、测试故障模型限制或缺陷及/或LRD引起的逃逸。举另一实例,使用统计采样来选择预烧及/或SLT的群体可忽视通过测试但应包含于补充步骤中的高度缺陷裸片。举另一实例,现有方法忽关于缺陷层、类型及位置的可用细节,所述等细节可与更好地评估一裸片的最终现场可靠性有关。举另一实例,半导体裸片供货商可不确定预烧及/或SLT是否适合存在的缺陷(且可避免)。举另一实例,缺陷数据可用于分析SLT中故障的根本原因,其从已知方法丢失。举另一实例,任何当前实施的模型是昂贵且难以优化,导致选择过大的群体而导致效率低下及潜在裸片损坏,及/或导致采样错误子集的风险。本文中应注意,2003年6月26日公开的第US2003/0120457A1号美国专利公开案(其在2007年3月20日作为第US 7,194,366B2号美国专利案发布)对相同区域中的缺陷采用有限缺陷群聚以执行此任务,但所描述的在单层上使用缺陷群聚忽视裸片在三维(3D)中的总缺陷率的加总影响,且不考虑按类型、层、位置或其类似者应用的权重。

因而,需要优化哪个半导体裸片经历预烧及/或SLT的补充步骤,例如,在最保守情况下,可高达100%的半导体裸片,导致成本大幅增加。举另一实例,半导体裸片供货商可尝试依赖于在测试及/或统计模型化期间收集的信息来对半导体装置群体进行子采样(例如,仅采样部分),依赖于具有固有间隙的电气数据。举另一实例,可使用来自单个过程层的缺陷群聚信息,但在没有100%筛检及加权加总缺陷率的异常值检测的情况下,此方法是不完整的,其可产生风险及/或不良优化。

在此方面,提供用于半导体缺陷引导预烧及SLT的系统及方法将是有益的。在所提供的系统及方法中,从工厂中的线内缺陷部分平均测试(I-PAT)筛检识别高度缺陷裸片的数据可补充现有方法,允许更明智地决定哪些裸片经历预烧及/或SLT。例如,可通过消除健康的低缺陷率半导体裸片上的预烧及/或SLT来降低成本。举另一实例,可通过确保仅有风险半导体裸片通过补充预烧步骤,而健康半导体裸片避免在这些步骤处的可行损坏,来提高半导体裸片质量。举另一实例,可通过确保在预烧及/或SLT的样本中包含高度缺陷半导体裸片来减少逃逸。应注意,用于I-PAT的系统及方法在2020年9月1日颁发的第10,761,128号美国专利案中描述,所述美国专利案的全部内容并入本文中。

公开所有缺陷类型的基于ATE的结构测试的缺点可影响所述技术的装置可靠性。为解决此,可需要预烧及/或SLT来补充结构测试并缩小其一些间隙以服务输出及输入质量控制需求两者。然而,增添预烧及/或SLT可承受严重测试成本降低压力。例如,补充方法需要大量时间,且因而行业需要优化这些步骤的群体及参数的方法。主要基于电气测试数据的方法具有固有间隙,但通过将每一半导体裸片的线内缺陷检验及/或计量I-PAT异常值数据引入到决策过程中,可产生相关但分开的数据源,从其可主动选择预烧及/或SLT的适当裸片且可成形这些步骤的参数以降低成本,同时提高质量。

本公开的实施例涉及用于半导体缺陷引导预烧及SLT的系统及方法。本公开的实施例还涉及提供一种更有效方法来确定哪个半导体裸片引导到预烧及/或SLT。本公开的实施例涉及在预烧及/或SLT的优化中使用加权加总筛检数据(例如,来自I-PAT或其它筛检方法的加权加总线内缺陷及/或计量异常值数据)。本公开的实施例涉及评估个别“有风险”裸片是否应经历预烧、SLT或两者。本公开的实施例涉及将I-PAT数据与电测试数据及统计采样模型合并以确定哪些“低风险”裸片适合不执行(例如跳过)预烧及/或SLT,及哪些“高风险”裸片应在预烧及/或SLT之前剔除。本公开的实施例涉及使用来自制造工厂中的筛检检查的线内缺陷数据来修改预烧及/或系统级测试程序参数的内容及持续时间。

图1及2大体上说明根据本公开的一或多个实施例的用于半导体缺陷引导预烧及系统级测试(SLT)的系统100的框图。本文中应注意,系统100可用于确定用于在工厂过程中的插入(例如,晶片分类、封装、预烧、SLT或其类似者)的总体策略。

在一些实施例中,系统100包含筛检子系统102。例如,筛检子系统102可包含或经配置以执行线内缺陷部分平均测试(I-PAT)过程或其它筛检过程,使得筛检子系统102是I-PAT子系统102。I-PAT方法的实例使用在2020年9月1日授权的第10,761,128号美国专利案中描述,所述美国专利案的全部内容先前并入本文中。

在一些实施例中,系统100包含缺陷引导安置控制器104(或缺陷引导测试服务器)。例如,缺陷引导安置控制器104可为半导体裸片预烧及SLT优化器。缺陷引导安置控制器104可包含经配置以执行在存储器108(例如,存储器媒体、存储器装置或其类似者)上维护或存储的程序指令的一或多个处理器106。本文中应注意,缺陷引导安置控制器104的一或多个处理器106可执行贯穿本公开描述的各种过程步骤中的任何者。例如,一或多个处理器106可经配置以从半导体工厂特性化子系统接收半导体裸片数据,使用筛检子系统从半导体裸片数据产生关于半导体裸片的加权加总分数,在动态决策过程期间将经定义规则应用于至少加权加总分数,基于动态决策过程产生至少一些半导体裸片的缺陷引导安置,及/或基于来自缺陷引导安置之后执行的缺陷引导测试的输出来确定调整。

系统100可包含耦合(例如,物理耦合、电耦合、通信耦合或其类似者)到缺陷引导安置控制器104的用户接口110。例如,用户接口110可为耦合到缺陷引导安置控制器104的分开的装置。举另一实例,用户接口110及缺陷引导安置控制器104可位于共同或共享壳体内。然而,本文中应注意,缺陷引导安置控制器104可不包含、不需要或耦合到用户接口110。

在一些实施例中,系统100包含耦合(例如,物理耦合、电耦合、通信耦合或其类似者)到筛检子系统102的半导体工厂特性化子系统112(或为本公开的目的,工厂特性化子系统112)。半导体工厂特性化子系统112可传输半导体数据114,半导体数据114可由筛检子系统102接收。例如,可直接在半导体工厂特性化子系统112与筛检子系统102之间传输半导体数据114。举另一实例,可经由一或多个辅助控制器或服务器在半导体工厂特性化子系统112与筛检子系统102的间传输半导体数据114。因而,如贯穿本公开描述的系统、子系统或控制器或服务器的实例仅出于说明性目的而提供且不应被解释为限制性。

半导体数据114可作为由半导体工厂特性化子系统112及筛检子系统102共享的标准化数据格式上传到筛检子系统102。例如,标准化数据格式可经格式化用于不同操作系统,包含(但不限于)Android、Apple iOS、Microsoft Windows、Apple macOS、Linux、ChromeOS、Unix、Ubuntu或其类似者。然而,本文中应注意,制造环境可使用第一类型的文件格式,而I-PAT环境可使用不同类型的文件格式。

因而,半导体数据114可为需要转换的非标准化制造数据格式。例如,半导体工厂特性化子系统112可将非标准化制造数据格式的半导体数据114传输到筛检子系统102,且筛检子系统102可在接收之后将半导体数据114转换成标准化测试数据格式。举另一实例,半导体工厂特性化子系统112可在传输到筛检子系统102之前将半导体数据114转换成标准化测试数据格式。另外,半导体数据114可上传到筛检子系统102作为特定于制造环境及/或测试环境的专有数据格式。进一步言之,半导体数据114可使用加密数据(例如经由常驻过程(daemon))、网络或云端接口或使用裸片可追溯性的其它安全连接来共享以确保半导体数据114保持同步。

筛检子系统102可接收半导体数据114且对半导体数据114执行一或多个筛检过程200。半导体数据114可包含关于多个半导体晶片202中的半导体晶片202的信息,其中多个半导体晶片202中的每一半导体晶片202包含多个(例如,1个、2个、…N个)层,所述层在由数个制造过程执行的数个(例如,数十、数百、数千)个步骤之后制造,其中多个层中的每一层包含多个半导体裸片204,其中多个半导体裸片204中的每一半导体裸片204包含多个块。在此方面,半导体数据114可包含晶片级数据、层级数据、裸片级数据及/或框级数据。为本公开的目的,“半导体数据”应被理解为包含“半导体裸片数据”,使得“半导体数据”及“半导体裸片数据”可被认为是相同的。然而,本文中应注意,“半导体数据”并不希望限于仅包含“半导体裸片数据”。

一或多个筛检过程200可特性化多个半导体裸片204。例如,多个半导体裸片204中的每一半导体裸片204可特性化为低缺陷率或“低风险”(或“良好”)半导体裸片206、中等缺陷率或“有风险”半导体裸片208或高缺陷率或“高风险”半导体裸片210。

本文中应注意,多个半导体裸片204的特性化可针对特定半导体晶片202上的多个半导体裸片204的所有(例如100%)或子集发生。另外,本文中应注意,多个半导体裸片204的特性化可针对特定半导体晶片202上的多个半导体层的所有(例如100%)或子集发生。例如,多个半导体层的子集可包含(但不限于)经确定为完全关键及/或包含关键方面的一或多层。进一步言之,本文中应注意,多个半导体裸片204的特性化可针对多个半导体晶片202的全部(例如100%)或子集发生。

在其中筛检子系统102是I-PAT子系统102的情况下,其中I-PAT分数潜在地可用于100%的晶片及100%的裸片,关于每一裸片的相对健康或质量的重要信息是可用的且可由测试工程师用于调整预烧及/或SLT。通过增添I-PAT数据,预烧及/或SLT的调整可以低延迟动态定制测试内容以减少逃逸,同时降低测试的总成本。另外,通过增添I-PAT数据,每一半导体裸片的预烧及/或SLT的调整可不同,潜在地导致每一受测试半导体装置的经调整测试时间、不同测试内容或不同测试准则。I-PAT方法的实例使用包含2020年9月1日颁发的第10,761,128号美国专利,所述美国专利的全部内容先前并入本文中。

在一些实施例中,筛检子系统102输出加权加总分数116(或I-PAT分数116,其中筛检子系统102是I-PAT子系统102)到缺陷引导安置控制器104。加权加总分数116可表示存在于每一半导体裸片204中的缺陷的数量及风险级别,跨经筛检的层中的每一者求和,使得加权加总分数116是裸片级分数。加权加总分数116可包含发生缺陷的层,包含关于半导体裸片204内的x,y位置的信息。加权加总分数116可描述缺陷的类型(例如,短接、开路或其类似者)、缺陷的大小、簇中的包含物或晶片202上的位置(例如x,y位置)。

在经输出到缺陷引导安置控制器104之前,加权加总分数116可与一或多个预设的异常值阈值或定制用户定义的异常值阈值分格化。然而,本文中应注意,加权加总分数116可以类似于半导体裸片数据114的组织形式输出到缺陷引导安置控制器104。

加权加总分数116可直接或经由一或多个辅助服务器或控制器间接输出到缺陷引导安置控制器104。因而,如贯穿本公开描述的系统、子系统或控制器或服务器的实例仅出于说明性目的而提供且不应被解释为限制性。

加权加总分数116可作为由筛检子系统102及缺陷引导安置控制器104共享的标准化数据格式上传到缺陷引导安置控制器104。例如,标准化数据格式可经格式化用于不同操作系统,包含(但不限于)Android、Applei OS、Microsoft Windows、Apple macOS、Linux、ChromeOS、Unix、Ubuntu或其类似者。然而,本文中应注意,制造环境及/或筛检或I-PAT环境可使用第一类型的文件格式(例如缺陷数据格式及KLARF文件格式),而制造后测试环境可使用不同类型的文件格式(例如,STDF文件格式、BITdb文件格式或其类似者)。

因而,加权加总分数116可为需要转换的非标准化制造数据格式。例如,筛检子系统102可将非标准制造数据格式的加权加总分数116传输到缺陷引导安置控制器104,且缺陷引导安置控制器104可在接收之后将加权加总分数116转换成标准化测试数据格式。举另一实例,筛检子系统102可在传输到缺陷引导安置控制器104之前将加权加总分数116转换成标准化测试数据格式。另外,可将加权加总分数116上传到缺陷引导安置控制器104作为特定于制造环境及/或测试环境的专有数据格式。进一步言之,加权加总分数116可使用加密数据(例如经由常驻进程)、网络或云端接口或使用裸片可追溯性的其它安全连接来共享以确保每一半导体裸片204的加权加总分数116保持同步。

本文中应注意,关于筛检子系统102、缺陷引导安置控制器104及/或半导体工厂特性化子系统112的以“标准化数据格式”及/或“非标准化数据格式”操作的区别仅出于说明性目的而提供且不应被解释为限制性。

在一些实施例中,缺陷引导安置控制器104从加权加总分数116产生一或多个缺陷引导安置118。例如,一或多个缺陷引导安置118可确定将跳过预烧及/或SLT,经历预烧及/或SLT及/或经剔除或用墨水涂去的样本或样本群体。举另一实例,一或多个缺陷引导安置118可确定预烧及/或SLT的准则、持续时间及/或限制,以使样本或样本群体经历预烧及/或SLT。

使用一组用户定义的规则或默认规则用于加权加总分数116(及/或加权加总分数116及/或对加权加总分数116的贡献元素)的准则,缺陷引导安置控制器104可对每一半导体裸片204的加权加总分数116使用基于动态规则的决策过程。例如,可使用基于动态规则的决策过程来取决于存在的缺陷的数量、类型、位置或层做出关于内容、持续时间及/或在每一受测试装置上执行的测试准则的决策。例如,基于动态规则的决策过程可使用加权加总分数116(及/或加权加总分数116及/或对加权加总分数116的贡献元素)来做出半导体裸片是否应经历预烧及/或SLT的决策。

用户定义的规则包含(但不限于)与指示问题的I-PAT信息耦合的数个故障、一或多个故障的严重程度或其类似者的一些组合。本文中应注意,规则可由专家、人工智能(AI)或其类似者来定义。例如,可通过确定性及/或统计阈值方法或过程、空间特征分析方法或过程、高级深度学习或机器学习方法或过程或其类似者来确定规则。一般来说,机器学习技术可为所属技术领域已知的任何技术,包含(但不限于)监督学习、无监督学习或其它基于学习的过程,例如(但不限于)线性回归、神经网络或深度神经网络、基于启发式模型或其类似者。

本文中应注意,决策的“动态”本质可由于用户定义规则的接收及决策过程的随后调整、当接收加权加总分数116时的决策过程的连续操作及/或基于经定义规则的应用来不断改变缺陷引导安置118以产生一或多个缺陷引导安置118中的一或多者。

缺陷引导安置控制器104可对每一半导体裸片204的加权加总分数116单独使用基于动态规则的决策过程,或可将基于动态规则的决策过程与其它过程组合及/或贡献元素(例如其它可用测试插入或制造数据)以根据用户定义的规则来影响适当半导体裸片分格化。

例如,决策过程可从经配置以在晶片批次完全制造之后在晶片分类期间执行电气分类过程的电气测试子系统120接收裸片级电气分类数据212。例如,裸片级电气分类数据212可包含(但不限于)在过程期间或之后从电气测试子系统120接收的晶片探针数据或其它电气测试数据以在结束制造过程(例如电气晶片分类(EWS)过程或其类似者)时电评估半导体装置功能。

举另一实例,决策过程可从经配置以在晶片批次的分割及封装之后执行最终测试程序的最终测试子系统122接收裸片级最终测试数据214。例如,可在过程期间或之后从最终测试子系统122接收裸片级最终测试数据214以在结束制造过程时评估半导体装置功能。

举另一实例,决策过程可从经配置以执行统计预测过程的统计预测模型124接收统计预测反馈216。例如,统计预测反馈216可呈数据集或表格、图形、模型或其它形式的物理或图形显示的形式。

本文中应注意基于动态规则的决策、电气测试子系统120及对应电气分类过程、最终测试子系统122及对应最终测试程序及/或统计预测模型124及对应统计预测过程可组合。例如,所述组合可基于在产生一或多个缺陷引导安置118时要考虑的用户定义的优先级(例如加权因素)。

一或多个缺陷引导安置118可包含以下非限制性实例中的一或多者。例如,一或多个缺陷引导安置118可基于低缺陷率或“低风险”(或“良好”)半导体裸片206与中等缺陷率或“有风险”半导体裸片208之间的第一阈值来进行,其中低缺陷率或“低风险”(或“良好”)半导体裸片206高于第一阈值且中等缺陷率或“有风险”半导体裸片208低于第一阈值。举另一实例,一或多个缺陷引导安置118可基于中等缺陷率或“有风险”半导体裸片208与高缺陷率或“高风险”半导体裸片210之间的第二阈值来进行,其中中等缺陷率或“有风险”的半导体裸片208高于第二阈值且高缺陷率或“高风险”半导体裸片210低于第二阈值。

在一个非限制性实例中,一或多个缺陷引导安置118可包含不执行(例如跳过)预烧及/或SLT的安置218。可针对低缺陷率或“低风险”(或“良好”)半导体裸片206选择安置218。例如,基于低加权加总分数116(例如单独或除数据212、214、216之外)而经确定为低缺陷率或“低风险”(或“良好”)半导体裸片206的半导体裸片204可经指示不执行(例如跳过)预烧及/或SLT。本文中应注意,安置218可提供最高机会来避免额外测试插入到低缺陷率或“低风险”(或“良好”)半导体裸片206中。

在另一非限制性实例中,一或多个缺陷引导安置118可包含安置220以执行预烧及/或执行SLT。可针对中等缺陷率或“有风险”半导体裸片208选择安置220。例如,基于加权加总分数116(例如单独或除额外数据212、214、216之外)而经确定为中等缺陷率或“有风险”半导体裸片208的半导体裸片204可在最终安置或释放之前根据用户定义的规则经引导到预烧及/或SLT。例如,缺陷属性(例如,缺陷大小、缺陷层、缺陷位置、缺陷类型或如贯穿本公开描述的其它缺陷属性)可用于自适应地成形预烧及/或SLT以更有效地启动存在于中等缺陷率或“有风险”半导体裸片208中的潜在LRD的持续时间及内容。本文中应注意,安置220可通过决定执行预烧及/或SLT来允许中等缺陷率“有风险”半导体裸片208的验证并强调中等缺陷率“有风险”半导体裸片208以启动潜在LRD。

尽管本公开的实施例说明要跳过预烧及/或SLT的安置218,然安置220可针对执行预烧及/或SLT,本文中应注意,针对低缺陷率或“低风险”(或“良好”)半导体裸片206进行的安置218及针对中等缺陷率“有风险”半导体裸片208进行的安置220是分开且独立,缺陷引导安置控制器104考虑有区别且不同因素,如贯穿本公开所描述。

在另一非限制性实例中,一或多个缺陷引导安置118可包含用于剔除或“用墨水涂去”的安置222。可针对高缺陷率或“高风险”半导体裸片210选择安置222。例如,基于加权加总分数116(例如分开地或除额外数据212、214、216之外)而经确定为高缺陷率或“高风险”半导体裸片210的半导体裸片204可在不执行预烧或SLT的情况下剔除或“用墨水涂去”。本文中应注意,当移除高缺陷率或“高风险”半导体裸片210(例如剔除或用墨水涂去)时,安置222可导致减少进入供应链的逃逸。另外,本文中应注意,安置222可通过不使异常值经受额外(及/或不必要)预烧及/或SLT来导致成本降低。

本文中应注意,以上非限制性实例仅出于说明缺陷引导安置118类型的目的而提供。

尽管筛检子系统102及缺陷引导安置控制器104经说明为系统100的分开的组件,但本文中应注意筛检子系统102及缺陷引导安置控制器104可集成在一起。例如,筛检子系统102可集成到缺陷引导安置控制器104中(例如,经编码以在缺陷引导安置控制器104上操作的过程),使得缺陷引导安置控制器104从半导体工厂特性化子系统112接收半导体裸片数据114。举另一实例,缺陷引导安置控制器104可集成到筛检子系统102中(例如,经编码为在筛检子系统102上操作的过程),使得筛检子系统102可产生一或多个缺陷引导安置118。

图3说明根据本公开的一或多个实施例的用于半导体缺陷引导预烧及系统级测试(SLT)的方法或过程300。本文中应注意,方法或过程300的步骤可全部或部分由图1及2中所说明的系统100实施。然而,进一步识别,方法或过程300不限于图1及2中所说明的系统100,不同的处在于额外或替代系统级实施例可执行方法或过程300的全部或部分步骤。

在步骤302,从半导体工厂特性化子系统接收半导体裸片数据。在一些实施例中,半导体裸片数据114由筛检子系统102从半导体工厂特性化子系统112接收。

在步骤304,使用筛检子系统从半导体裸片数据产生关于半导体裸片的加权加总分数。在一些实施例中,筛检子系统102加权加总分数116将半导体裸片204分离或分格化。

在步骤306,在动态决策过程期间将定义的规则至少应用于加权加总分数。在一些实施例中,缺陷引导安置控制器104可基于一组用户定义的规则或用于关于加权加总分数116(及/或对加权加总分数116的贡献元素及/或对加权加总分数116)的准则的默认规则对每一半导体裸片204的加权加总分数116使用基于动态规则的决策过程。例如,可单独使用加权加总分数116。举另一实例,可组合使用加权加总分数116与其它可用测试插入或制造数据,包含(但不限于)裸片级电气分类数据212、裸片级最终测试数据214、统计预测反馈216或其类似者。定义的规则可为用户定义且由缺陷引导安置控制器104接收(例如经由用户接口110)。另外或替代地,定义的规则可默认于缺陷引导安置控制器104内。进一步言之,另外或替代地,定义的规则可基于对应加权加总分数116及/或在半导体裸片204上的经观察缺陷来分离半导体裸片204。

本文中应注意,筛检子系统102可在将半导体裸片数据114分格化成加权加总分数116期间将半导体裸片204分离为低缺陷率或“低风险”(或“良好”)半导体裸片206、中等缺陷率“有风险”半导体裸片208或高缺陷率半导体裸片210。另外,本文中应注意,缺陷引导安置控制器104可在接收加权加总分数116之后将半导体裸片204分离为低缺陷率或“低风险”(或“良好”)半导体裸片206、中等缺陷率“有风险”半导体裸片208或高缺陷率半导体裸片210。

在步骤308,基于动态决策过程产生至少一些半导体裸片的缺陷引导安置。在一些实施例中,缺陷引导安置将多个半导体裸片204中的每一半导体裸片204特性化为低缺陷率或“低风险”(或“良好”)半导体裸片206、中等缺陷率或“有风险”半导体裸片208或高缺陷率或“高风险”半导体裸片210。特性化可涉及合并或组合半导体裸片204的加权加总分数116与合适晶片级数据、裸片级电气分类数据212及/或裸片级最终测试数据214。

在一个非限制性实例中,低缺陷率“良好”半导体裸片206可经由数据的合并或组合来识别以在安置218之后建立可安全地不执行(例如跳过)预烧及/或SLT的半导体裸片群体的分格化。本文中应注意,此识别可节省时间及金钱,其中可靠性失效的风险最小。另外,本文中应注意,此识别可减少因处理造成的良品率损失及在预烧期间损坏的“行走受伤”裸片的产生,否则所述裸片将令人满意。

在另一非限制性实例中,由于缺陷率级别,中等缺陷率或具高风险的“有风险”半导体裸片208可经由数据的合并或组合来识别以在安置220之后建立将基于用户定义的准则而引导到预烧及/或SLT的分格化。在识别中等缺陷率或“有风险”半导体裸片208时,可区分缺陷的层、类型及位置以成形预烧及/或SLT的持续时间及内容,选择已知最能“启动”潜在故障源的参数。对于确实未通过SLT的装置,相关缺陷率数据将提供更窄潜在根本原因领域,其为对已知开环方法的改进。

在另一非限制性实例中,高缺陷率或“高风险”半导体裸片210或加权加总缺陷率分数与更广泛群体显著不同的异常裸片可经由数据的合并或组合来识别,以在不执行预烧或SLT的情况下在安置222之后建立将引导到剔除或“用墨水涂去”的分格化。本文中应注意,剔除或“用墨水涂去”高缺陷率或“高风险”半导体裸片210可通过避免额外不必要步骤、同时还减少低可靠性半导体裸片逃逸到供应链中来降低测试成本。

在步骤310中,基于来自在缺陷引导安置之后执行的缺陷引导测试的输出来确定调整。在一些实施例中,调整经传输到半导体工厂特性化子系统112以取决于制造过程的完整性经由前馈回路(例如以校正当前半导体装置)或反馈回路(例如以调整未来半导体装置)来调整制造过程及/或特性化过程。例如,不完整制造过程可经由前馈回路或反馈回路来校正,然在产生关于将预烧及/或SLT用于不完整制造过程的一或多个缺陷引导安置118时,缺陷引导安置控制器104可或可不考虑裸片级电气分类数据212及/或裸片级最终测试数据214。举另一实例,完整制造过程可经由反馈回路校正,且在产生关于将预烧及/或SLT用于完整制造过程的一或多个缺陷引导安置118时,缺陷引导安置控制器104可考虑裸片级电气分类数据212及/或裸片级最终测试数据214。在此方面,可改进制造过程及/或特性化过程,导致制造商成本的降低(例如,时间、金钱或其类似者),同时维持所需质量级别(例如PPB故障率)。

尽管本发明的实施例说明由缺陷引导安置控制器104执行的方法或过程300的步骤,但本文中应注意,方法或过程300的一些或所有步骤可由通信地耦合到缺陷引导安置控制器104的服务器或控制器执行。例如,服务器或控制器可包含处理器及存储器,及如贯穿本公开描述的其它通信耦合组件。

图4A及4B说明根据本公开的一或多个实施例的用于制造、特性化及/或测试半导体装置的系统400的框图。本文中应注意,系统400可经配置以执行处理步骤以制造及/或分析半导体装置及/或半导体装置上的组件(例如半导体裸片),如贯穿本公开所描述。另外,本文中应注意,系统400可包含系统100的全部或部分,如贯穿本公开所描述。

在一些实施例中,系统400包含半导体工厂特性化子系统112、电气测试子系统120、最终测试子系统122及/或经配置以产生统计预测模型124的组件。本文中应注意,半导体工厂特性化子系统112、电气测试子系统120、最终测试子系统122及/或经配置以产生统计预测模型124的组件可独立或可至少部分组合或集成在一起。另外,本文中应注意,半导体工厂特性化子系统112、电气测试子系统120、最终测试子系统122及/或经配置以产生统计预测模型124的组件可独立或可至少部分与系统400的其它组件组合或集成,如贯穿本公开所描述。

在一些实施例中,半导体工厂特性化子系统112包含经配置以在半导体裸片数据114(例如,特性化数据114)内(或作为其)输出特性化测量的一或多个特性工具。例如,特性化测量可包含(但不限于)过程控制检查(例如基于采样的检查)、关键半导体装置层的筛检检查或其类似者。为本公开的目的,“特性化测量”可指的是线内缺陷检查及/或线内计测量量。

在一个非限制性实例中,半导体工厂特性化子系统112可包含用于检测样本404(例如半导体晶片202)的一或多层中的缺陷的至少一个检查工具402(例如线内样本分析工具)。半导体工厂特性化子系统112通常可包含任何数目或类型的检查工具402。例如,检查工具402可包含光学检查工具,所述光学检查工具经配置以基于使用来自任何源的光对样本404的询问来检测缺陷,例如(但不限于)激光源、灯源、X射线源或宽带等离子体源。举另一实例,检查工具402可包含颗粒束检查工具,所述颗粒束检查工具经配置以基于用一或多个颗粒束(例如(但不限于)电子束、离子束或中性粒子束)对样本404的询问来检测缺陷。例如,检查工具402可包含透射电子显微镜(TEM)或扫描电子显微镜(SEM)。为本公开的目的,本文中应注意,至少一个检查工具402可为单个检查工具402或可表示群组的检查工具402。

本文中应注意,样本404可为多个半导体晶片的半导体晶片,其中多个半导体晶片中的每一半导体晶片包含遵循由数个半导体制造过程执行的数个(例如,数十、数百、数千)步骤制造的多个(例如,1个、2个、…N个)层,其中多个层中的每一层包含多个半导体裸片,其中多个半导体裸片中的每一半导体裸片包含多个区块。另外,本文中应注意,样本404可为由多个半导体裸片形成的半导体裸片封装,所述多个半导体裸片配置于先进裸片封装或3D裸片封装内的衬底上的裸裸片的2.5D横向组合中。

为本公开的目的,术语“缺陷”可指的是由线内检查工具发现的物理缺陷、计测量量异常值或被认为是异常的半导体装置的其它物理特性。缺陷可被认为是制造层或层中的制造图案与设计特性的任何偏差,包含(但不限于)物理、机械、化学或光学性质。另外,缺陷可被认为是制造半导体裸片封装中的组件的对准或接合的任何偏差。进一步言之,相对于半导体裸片或其上的特征,缺陷可具有任何大小。依此方式,缺陷可小于一半导体裸片(例如在一或多个图案化特征的规模上)或可大于半导体裸片(例如作为晶片级划痕或图案的部分)。例如,缺陷可包含在图案化之前或之后的样本层的厚度或组成物的偏差。举另一实例,缺陷可包含图案化特征的大小、形状、定向或位置的偏差。举另一实例,缺陷可包含与光刻及/或蚀刻步骤相关联的缺陷,例如(但不限于)相邻结构之间的桥接(或缺乏)、凹坑或孔。举另一实例,缺陷可包含样本404的损坏部分,例如(但不限于)划痕或碎屑。例如,缺陷的严重性(例如,划痕的长度、凹坑的深度、经测量的缺陷量值或极性或其类似者)可为重要的并被考虑在内。举另一实例,缺陷可包含引入到样本404的外来颗粒。举另一实例,缺陷可为样本404上的未对准及/或未接合的封装组件。据此,应理解,本公开中的缺陷的实例仅为说明性目的而提供而不应被解释为限制性。

在另一非限制性实例中,半导体工厂特性化子系统112可包含用于测量样本404或其一或多层的一或多个性质的至少一个计量工具406(例如线内样本分析工具)。例如,计量工具406可特性化性质(例如(但不限于)层厚度、层组成、临界尺寸(CD)、覆盖层或光刻处理参数(例如,光刻步骤期间的照明强度或剂量))。在此方面,计量工具406可提供关于样本404的制造、样本404的一或多层或样本404的一或多个半导体裸片的信息,所述信息可与可导致所得制造装置的可靠性问题的制造缺陷的概率相关。为本公开的目的,本文中应注意,至少一个计量工具406可为单个计量工具406或可表示群组的计量工具406。

在一些实施例中,半导体工厂特性化子系统112包含至少一个半导体制造工具或过程工具408。本文中应注意,样本404可在样本404的制造期间在一或多个检查工具402、一或多个计量工具406及一或多个过程工具408之间移动。例如,过程工具408可包含所属技术领域中已知的任何工具,包含(但不限于)蚀刻器、扫描仪、步进机、清洁器或其类似者。例如,制造过程可包含制造跨样本(例如半导体晶片或其类似者)的表面分布的多个裸片,其中每一裸片包含形成装置组件的多个图案化材料层。每一图案化层可由过程工具408经由一系列步骤形成,包含材料沉积、光刻、蚀刻以产生感兴趣图案,及/或一或多个曝光步骤(例如,由扫描仪、步进器或其类似者执行)。举另一实例,过程工具408可包含所属技术领域中已知的经配置以将半导体裸片封装及/或组合成2.5D及/或3D半导体裸片封装的任何工具。例如,制造过程可包含(但不限于)对准半导体裸片及/或半导体裸片上的电组件。另外,制造过程可包含(但不限于)经由混合键合(例如,裸片到裸片、裸片到晶片、晶片到晶片或其类似者)焊料、粘着剂、紧固件或其类似者来接合半导体裸片及/或半导体裸片上的电组件。为本公开的目的,本文中应注意,至少一个过程工具408可为单个过程工具408或可表示群组的过程工具408。本文中应注意,为本公开的目的,术语“制造过程(fabricationprocess)”及“制造过程(manufacturing process)”连同术语(例如,“制造线(fabricationline)”及“制造线(manufacturing line)”、“制造商(fabricator)”及“制造商(manufacturer)”或其类似者)的相应变体可被认为是等同的。

在一些实施例中,系统400包含用于测试制造装置的一或多个部分的功能的电气测试子系统120及/或最终测试子系统122。例如,电气测试子系统120及/或最终测试子系统122可经配置以产生裸片级电气分类数据212及/或裸片级最终测试数据214。本文中应注意,样本404可在完成样本404的制造之后从半导体工厂特性化子系统112移动到电气测试子系统120及/或最终测试子系统122。

在一个非限制性实例中,电气测试子系统120及/或最终测试子系统122可包含任何数目或类型的电气测试工具410以完成晶片级的初步探测。例如,初步探测可不经设计以试图在晶片级强制失败。

在另一非限制性实例中,电气测试子系统120及/或最终测试子系统122可包含任何数目或类型的压力测试工具412以测试、检查或依其它方式特性化在制造循环中的任何时间的制造装置的一或多个部分的性质。例如,压力测试工具412可包含(但不限于)预烧电气晶片分类及最终测试(例如电子测试)或经配置以使样本404振动、加热样本404(例如烤箱或其它热源),冷却样本404(例如冷冻机或其它冷源),在选定湿度级别下操作样本404,在不正确电压(例如电源)下操作样本404或另一异常电气条件或其类似者的预烧电气测试。应注意,样本404可分开或以一些组合经受上文非限制性测试。

在一些实施例中,缺陷使用半导体工厂特性化子系统112(例如,检查工具402、计量工具406或其类似者)、电气测试子系统120及/或最终测试子系统122(例如,包含电气测试工具410及/或压力测试工具412或其类似者)的任何组合来识别,所述子系统在由半导体裸片及/或半导体裸片封装中的感兴趣层的一或多个过程工具408执行的一或多个处理步骤(例如光刻、蚀刻、对准、接合或其类似者)之前或之后使用。在此方面,在制造过程的各个阶段处的缺陷检测可指称线内缺陷检测。

在一些实施例中,系统400包含控制器414。控制器414可与系统400的组件中的任何者通信耦合,包含(但不限于)半导体工厂特性化子系统112(例如,包含检查工具402、计量工具406及/或过程工具408)、电气测试子系统120及/或最终测试子系统122(例如,包含电气测试工具410及/或压力测试工具412)或其类似者。本文中应注意,为本公开的目的,图4A中所说明的实施例及图4B中所说明的实施例可被认为是相同系统400的部分或不同系统400的部分。另外,本文中应注意,图4A中所说明的系统400内的组件及图4B中所说明的系统400内的组件可直接通信或可通过控制器414通信。

控制器414可包含经配置以执行在存储器418(例如存储器媒体、存储器装置或其类似者)上维护的程序指令的一或多个处理器416。控制器414可经配置以执行方法或过程200及/或方法或过程500的步骤中的一者或所有(例如如贯穿本公开所描述)。在此方面,子系统112、120及/或122可存储于控制器414中及/或经配置以由控制器414执行。然而,本文中应注意,子系统112、120及/或122可与控制器414分离且经配置以与控制器414通信(例如,直接或通过通信地耦合到控制器414的服务器或控制器,其中服务器或控制器可包含处理器及存储器及其它通信耦合的组件,如贯穿本公开所描述)。

一或多个处理器416可包含所属技术领域中已知的任何处理器或处理元件。为本公开的目的,术语“处理器”或“处理元件”可广泛定义为涵盖具有一或多个处理或逻辑元件(例如,一或多个图形处理单元(GPU)、微处理单元(MPU)、系统单芯片(SoC)、一或多个专用集成电路(ASIC)装置、一或多个现场可编程门阵列(FPGA)或一或多个数字信号处理器(DSP))的任何装置。在此意义上,一或多个处理器416可包含经配置以执行算法及/或指令(例如,存储于存储器中的程序指令)的任何装置。在一个实施例中,一或多个处理器416可体现为桌面计算机、大型机计算机系统、工作站、图像计算机、并行处理器、联网计算机或经配置以执行经配置以操作系统100及/或400的组件或与其一起操作的程序的任何其它计算机系统,如贯穿本公开所描述。

存储器418可包含所属技术领域中已知的适合存储可由相关联相应一或多个处理器416执行的程序指令的任何存储媒体。例如,存储器418可包含非瞬态存储器媒体。举另一实例,存储器418可包含(但不限于)只读存储器(ROM)、随机存取存储器(RAM)、磁或光学存储器装置(例如磁盘)、磁带、固态硬盘及其类似者。进一步应注意,存储器418可与一或多个处理器416一起容纳于共同控制器壳体中。在一个实施例中,存储器418可相对于相应一或多个处理器416的物理位置远程定位。例如,相应一或多个处理器416可存取可通过网络(例如,因特网、内部网络及其类似者)存取的远程存储器(例如服务器)。

在另一实施例中,系统400包含耦合(例如,物理耦合、电耦合、通信耦合或其类似者)到控制器414的用户接口420。例如,用户接口420可为耦合到控制器414的分开的装置。举另一实例,用户接口420及控制器414可位于共同或共享壳体内。然而,本文中应注意,控制器414可不包含、不需要或耦合到用户接口420。

用户接口420可包含(但不限于)一或多个桌面计算机、膝上型计算机、平板计算机及其类似者。用户接口420可包含用于显示系统100及/或400的数据的显示器给用户。用户接口420的显示器可包含所属技术领域中已知的任何显示器。例如,显示器可包含(但不限于)液晶显示器(LCD)、基于有机发光二极管(OLED)的显示器或CRT显示器。所属领域的技术人员应识别,能够与用户接口420整合的任何显示装置适于本公开中的实施方案。在另一实施例中,用户可响应于显示的数据给用户来经由用户接口420的用户输入装置输入选择及/或指令。

图5说明根据本公开的一或多个实施例的用于制造、特性化及/或测试半导体装置的方法或过程500。本文中应注意,方法或过程500的步骤可全部或部分由图4A及4B中所说明的系统400实施。然而,进一步识别,方法或过程500不限于图4A及4B中所说明的系统400,不同的处在于额外或替代系统级实施例可执行方法或过程500的步骤的全部或部分。

在步骤502,用半导体工厂特性化子系统制造半导体装置。在一些实施例中,半导体晶片202经由多个半导体制造过程制造。例如,半导体工厂特性化子系统112可包含(但不限于)经配置以制造半导体装置的一或多个过程工具408,包含根据由数个半导体制造过程执行的一定数目(例如,数十、数百、数千)个步骤制造的1个、2个、…N个层。

在步骤504,用半导体工厂特性化子系统获取半导体裸片的特性化测量。在一些实施例中,特性化测量由半导体工厂特性化子系统112获取。例如,特性化测量可由多个特性化工具(例如,检查工具402及/或计量工具406)在经由由多个过程工具408执行的多个半导体制造过程制造一或多个半导体晶片202期间(例如步骤之前、步骤之间及/或步骤之后)执行。

在步骤506,将特性化测量传输到筛检子系统。在一些实施例中,特性化测量作为特性数据114或半导体裸片数据114经传输到筛检子系统102。筛检子系统102可基于特性化测量产生加权加总分数116。在一些实施例中,缺陷引导安置控制器104基于加权加总分数116产生一或多个缺陷引导安置118。

本文中应注意,当传输特性化测量到筛检子系统102时,一或多个半导体晶片202可循序、共同或同时传送到电气测试子系统120及/或最终测试子系统122,其中分别地,电气测试子系统120可经配置以产生裸片级电气分类数据212,且最终测试子系统122可经配置以产生裸片级最终测试数据214。

在步骤508,控制信号经产生用于基于来自对基于来自筛检子系统的加权加总分数制成的半导体裸片的至少一些执行的缺陷引导测试的输出所确定的调整。在一些实施例中,一或多个控制信号经引导到一或多个半导体晶片202的制造、特性化或测试中的至少一者。例如,一或多个控制信号可经由前馈回路(例如以校正当前半导体装置)或反馈回路(例如以调整未来半导体装置)取决于完整性或制造过程来调整半导体工厂特性化子系统112及/或一或多个制造过程或方法或由半导体工厂特性化子系统112采用的一或多个特性化过程或方法。例如,不完整制造过程可经由前馈回路或反馈回路来校正,然缺陷引导安置控制器104在产生关于将预烧及/或SLT用于不完整制造过程的一或多个缺陷引导安置118时可或可不考虑裸片级电气分类数据212及/或裸片级最终测试数据214。举另一实例,完整制造过程可经由反馈回路校正,且缺陷引导安置控制器104可在产生关于将预烧及/或SLT用于完整制造过程的一或多个缺陷引导安置118时考虑裸片级电气分类数据212及/或裸片级最终测试数据214。

尽管本公开的实施例说明由控制器414执行的方法或过程500的步骤,但本文中应注意,方法或过程500的一些或所有步骤可由通信地耦合到控制器414的服务器或控制器执行。例如,服务器或控制器可包含处理器及存储器,及如贯穿本公开所描述的其它通信耦合组件。

本文中应注意,方法或过程300及500不限于所提供的步骤及/或子步骤。方法或过程300及500可包含更多或更少步骤及/或子步骤。方法或过程300及500可同时执行步骤及/或子步骤。方法或过程300及500可顺序执行步骤及/或子步骤,包含依所提供的顺序或除所提供之外的顺序。因此,以上描述不应被解释为对本公开的范围的限制,而仅是图解说明。

在此方面,本公开的系统及方法通过确保最有缺陷半导体裸片经历额外质量验证来降低逃逸。本公开的系统及方法还通过在高于选择阈值的半导体裸片上不执行(例如跳过)预烧及/或SLT来降低测试成本。本公开的系统及方法还通过剔除低于选定阈值的半导体裸片来降低测试成本,消除不必要预烧及/或SLT。本公开的系统及方法还塑造预烧及/或SLT的持续时间及参数以提高其对存在的缺陷的功效。本公开的系统及方法还基于从上游工厂接收的数据来管理测试成本降低及质量改进的冲突业务优先级。本公开的系统及方法还将前端工厂与后端测试连接作为差异化能力来协助展示对PPB及总成本降低目标的持续改进。

在本公开的系统及方法的使用案例的一个非限制性实例中,提供任务及安全关键部件的半导体制造商的质量团队观察到低可靠性装置逃入库存的不令人满意程度。装置工程师及测试工程师已将测试设计最大化,且ATE结构测试覆盖率接近99%的晶体管。然而,复杂设计及爆炸式晶体管数量使得数百万个晶体管仍未经测试,导致涵盖空隙。与不可测试的LRD及故障模型缺陷组合的这些涵盖空隙意味着低可靠性裸片的逃逸率以不可接受速度(例如,特别是在斜坡早期,当较低良率放大这些影响时)继续。为了补偿,可利用额外预烧及/或SLT来进一步筛检潜在低可靠性部件,使其不进入供应链。

优化这些缓慢且成本高昂的步骤的增添可为困难的,因为选择100%采样会因侵蚀利润及减慢生产而增加显著测试成本,同时还潜在地产生非所需良率损失,否则导致良好裸片。另外,子采样可存在问题,因为其主要基于来自具有固有空隙的上游电气测试的数据。进一步言之,历史工厂制造数据很少从深度抽样的过程控制检查获得且缺乏对半导体裸片相对于群体或缺陷大小、缺陷层、缺陷位置、缺陷类型或其它缺陷属性的缺陷率的整体评估,如贯穿本公开所描述。

随着制造工厂中筛检的出现,相关数据可从分开但相关源输入到将发送到预烧及/或SLT的半导体裸片的安置中(例如,其可分开、循序、同时或同时发生)。

本公开的优点涉及用于半导体缺陷引导预烧及SLT的系统及方法。本公开的优点还涉及提供一种更有效方法来确定哪个半导体裸片引导到预烧及/或SLT。本公开的优点涉及在预烧及/或SLT的优化中使用加权加总筛检数据(例如,来自I-PAT或其它筛检方法的加权加总线内缺陷及/或计量异常值数据)。本公开的优点涉及评估个别“有风险”裸片是否应经历预烧、SLT或两者。本公开的优点涉及将I-PAT数据与电气测试数据及统计采样模型合并以确定哪些“低风险”裸片适合不执行(例如跳过)预烧及/或SLT,及在预烧及/或SLT之前应剔除哪些“高风险”裸片。本公开的优点涉及使用来自制造工厂中的筛检检查的线内缺陷数据来修改预烧及/或系统级测试程序参数的内容及持续时间。

本文中所描述的目标物有时说明包含于其它组件内或与其它组件连接的不同组件。应理解,此类所描述架构仅是示范性,且实际上可实施达成相同功能的许多其它架构。在概念意义上,达成相同功能性的任何组件布置是有效地“相关联”,使得达成所需功能。因此,本文中组合以达成特定功能的任何两个组件可被视为彼此“相关联”,使得达成所需功能,而与架构或中间组件无关。同样,如此相关联的任何两个组件还可被视为彼此“连接”或“耦合”以达成所需功能,且能够如此相关联的任何两个组件还可被视为彼此“可耦合”以达成所需功能。可耦合的具体实例包含(但不限于)物理可互动及/或物理互动组件及/或无线互动及/或无线互动组件及/或逻辑互动及/或逻辑互动组件。

据信本公开及其许多伴随优点将通过前面描述来理解,且显然可在不背离所公开的目标物或不牺牲其所有的物质优势的情况下对组件的形式、构造及布置进行各种改变。所描述的形式仅是解释性,且所附权利要求书希望是涵盖及包含此类变化。此外,应理解,本发明由所附权利要求书定义。