一种NAND Flash控制器接口电路及闪存系统

文献发布时间:2023-06-19 11:19:16

技术领域

本申请数据处理技术领域,尤其涉及一种NAND Flash控制器接口电路及闪存系统。

背景技术

闪存(Flash)尤其是NAND闪存是非挥发存储器的一种,被广泛的应用于手机、笔记本电脑、云存储等存储领域,随着NAND Flash技术的更新,NAND Flash控制器的设计对于NAND Flash性能提高愈发重要。

开放式NAND快闪存储器接口(Open NAND Flash Interface,ONFI)规范是一种Flash闪存接口的标准,是Intel为统一当初混乱的闪存接口所倡导的标准,目前ONFI协议的数据接口已经发展到NV-DDR3,且不同的数据接口下有不同的时间模式,在ONFI协议中NAND Flash支持的数据接口有三种情况:

①当电压VccQ=3.3V,上电初始化完成后进入SDR模式,SDR和NV-DDR之间可以切换;②当电压VccQ=1.8V,上电初始化完成后进入SDR模式,SDR和NV-DDR、SDR和NV-DDR2之间可以切换;③当电压VccQ=1.2v,上电初始化完成后进入NV-DDR3模式,数据接口不再切换。

目前业界主流的NAND Flash主要支持SDR与NV-DDR2/3数据接口。因此,本发明主要基于SDR与NV-DDR2/3数据接口研究。

现有的控制器设计中不同数据接口下时序产生电路分别由指令、地址、数据输入、数据输出四部分来实现,在涉及到模式切换的过程中,命令周期、地址周期的时序产生电路分别仅在相应数据接口下的时间内使用,例如当由SDR数据接口切换为NV-DDR2数据接口后,SDR的时序产生电路是处于空闲状态的,反之亦然。

对于控制器的时序产生电路,由于对NAND Flash的操作同一时间只对应一种数据接口,不同的数据接口实现对应不同的电路,因此在接口切换后,其他未使用到的时序产生电路会处于空闲状态,比较浪费电路资源。

发明内容

有鉴于此,本申请提供了一种NAND Flash控制器接口电路及闪存系统,能够节省电路资源。

本申请提供了一种NAND Flash控制器接口电路,包括:

命令地址时序产生电路,用于根据所述接口选择信号确定目标接口模式对应的时间参数,并根据所述目标接口模式对应的时间参数,产生所述目标接口模式对应的命令周期时序和地址周期时序;所述目标接口模式为SDR模式、NV-DDR2模式、NV-DDR3模式中的任意一种。

可选的,在上电初始化完成后,初始接口模式作为目标接口模式;其中,所述目标接口模式为SDR模式或NV-DDR3模式。

可选的,所述NAND Flash控制器接口电路还包括:

时钟切换电路,用于在第一接口模式切换为第二接口模式时,根据所述接口选择信号进行时钟切换,以使所述目标接口模式的时间参数从所述第一接口模式的时间参数切换为所述第二接口模式的时间参数。

可选的,所述第一接口模式为SDR模式,所述第二接口模式为NV-DDR2模式;或,所述第一接口模式为NV-DDR2模式,所述第二接口模式为SDR模式。

可选的,所述时钟切换电路包括:第一与门电路,第二与门电路,第三与门电路,第四与门电路,第一D触发器、第二D触发器,第三D触发器,第四D触发器,非门电路,或门电路;

所述接口选择信号输入至所述第一与门电路,且通过所述非门电路输入至所述第二与门电路;

所述第一与门电路的输出端连接所述第一D触发器的D端,第一时钟信号输入到所述第一D触发器的时钟输入端,所述第一D触发器的Q端连接所述第二D触发器的D端,所述第一时钟信号的非值输入所述第二D触发器的时钟输入端,所述第二D触发器的Q端连接所述第三与门电路的输入端,所述第一时钟信号输入到所述第三与门电路的输入端;所述第一时钟信号为与所述第一接口模式对应的时钟信号;

所述第二与门电路的输出端连接所述第三D触发器的D端,第二时钟信号输入到所述第三D触发器的时钟输入端,所述第三D触发器的Q端链接所述第四D触发器的D端,所述第二始终信号的非值输入所述第四D触发器的时钟输入端,所述第四D触发器的Q端连接所述第四与门电路的输入端,所述第二时钟信号输入到所述第四与门电路的输入端;所述第二时钟信号为所述第二接口模式对应的时钟信号;

所述第二D触发器的Q非端与所述第二与门电路的输入端连接,所述第四D触发器的Q非端与所述第一与门电路的输入端连接;

所述第三与门电路的输出端连接所述或门电路的输入端,所述第四与门电路的输出端连接所述或门电路的输入端,所述或门电路的输出端作为所述时钟切换电路的输出端。

可选的,所述目标接口模式基于ONFI协议。

可选的,还包括:

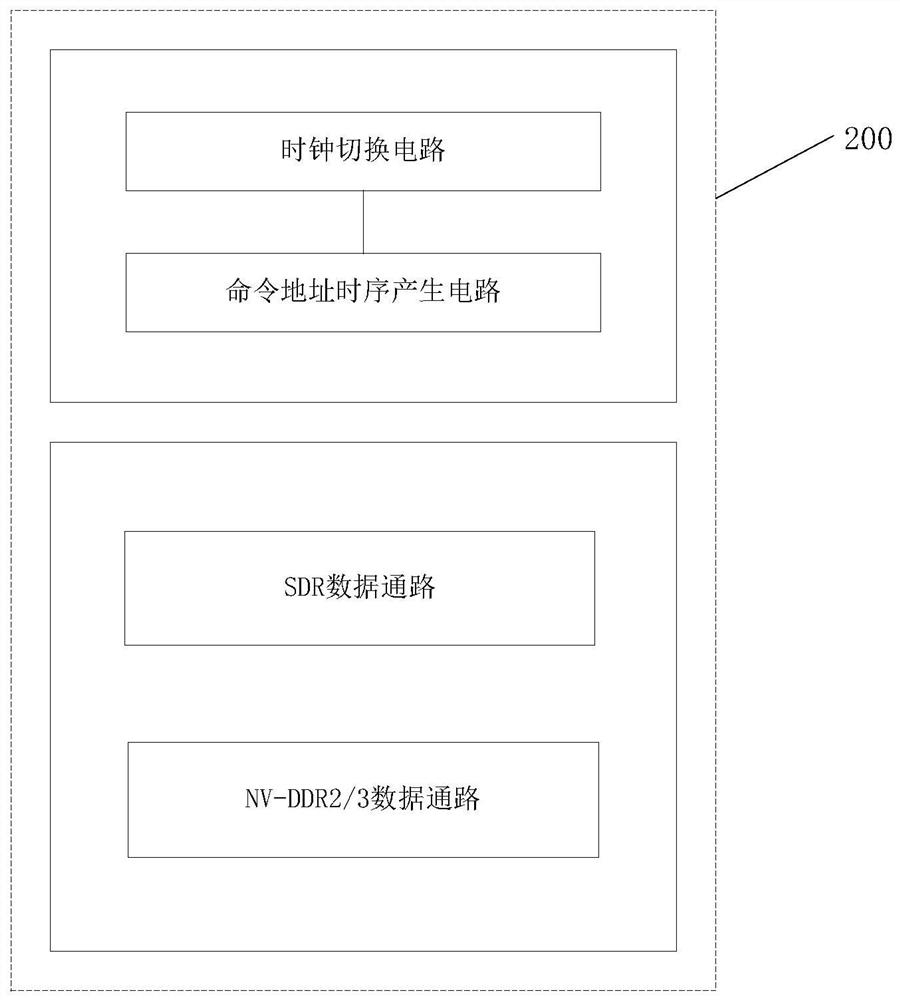

SDR数据通路,用于在SDR模式下产生SDR数据输入时序或SDR数据输出时序;

NV-DDR2/NV-DDR3数据通路,用于在NV-DDR2/NV-DDR3模式下产生NV-DDR2/NV-DDR3数据输入时序或NV-DDR2/NV-DDR3数据输出时序。

可选的,所述目标接口模式对应的命令周期时序和地址周期时序满足目标接口模式下的多个时间模式下的时间参数。

可选的,所述目标接口模式为SDR模式时,所述目标接口模式的时间模式包括6种;所述目标接口模式为NV-DDR2模式或NV-DDR3模式时,所述目标接口模式的时间模式包括13种。

本申请实施例还提供了一种闪存系统,包括NAND Flash闪存单元、控制器和所述的NAND Flash控制器接口电路;所述NAND Flash控制器接口电路连接所述NAND Flash闪存单元和所述控制器。

综上所述,本申请公开了一种NAND Flash控制器接口电路及闪存系统,NANDFlash控制器接口电路包括命令地址时序产生电路,其中命令地址时序产生电路可以根据接口选择信号确定目标接口模式对应的时间参数,并根据目标接口模式对应的时间参数,产生目标接口模式对应的命令周期时序和地址周期时序,目标接口模式可以为SDR模式、NV-DDR2模式、NV-DDR3模式中的任意一种,这样命令地址时序产生电路可以根据接口选择信号而确定对应的时间参数,根据多个时间参数而工作在多个目标接口模式之下,实现了电路模块的复用,无需对应多种目标接口模块而设置不同的电路模块,节省电路资源。

附图说明

为了更清楚地说明本申请实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1为目前一种控制器接口电路的结构示意图;

图2为本申请公开的一种NAND Flash控制器接口电路的结构示意图;

图3为SDR命令周期时序和SDR地址周期时序的示意图;

图4为NV-DDR2/3命令周期时序和NV-DDR2/3地址周期时序的示意图;

图5为SDR与NV-DDR2/3命令地址时序的示意图;

图6为SDR模式切换为NV-DDR2模式的场景下的NAND Flash控制器接口电路工作过程示意图;

图7为NV-DDR3模式的场景下的NAND Flash控制器接口电路工作过程示意图;

图8为本申请实施例提供的一种时钟切换电路的结构示意图;

图9为本申请实施例提供的一种闪存系统的结构示意图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

目前ONFI协议的数据接口已经发展到NV-DDR3,且不同的数据接口下有不同的时间模式,在ONFI协议中NAND Flash支持的数据接口有三种情况:

①当电压VccQ=3.3V,上电初始化完成后进入SDR模式,SDR和NV-DDR之间可以切换;②当电压VccQ=1.8V,上电初始化完成后进入SDR模式,SDR和NV-DDR、SDR和NV-DDR2之间可以切换;③当电压VccQ=1.2v,上电初始化完成后进入NV-DDR3模式,数据接口不再切换。

现有的控制器设计中不同数据接口下时序产生电路分别由指令、地址、数据通路三部分来实现,在涉及到模式切换的过程中,命令周期、地址周期的时序产生电路分别仅在相应数据接口下的时间内使用,由于在ONFI协议中NV-DDR2与NV-DDR3数据接口的时序完全相同,所以本发明涉及这两种数据接口的时序说明时,统称为NV-DDR2/3数据接口。

参考图1所示,为目前一种控制器接口电路的结构示意图,控制器接口电路100包括时序产生电路,时序产生电路包括SDR命令时序产生电路、SDR地址时序产生电路、SDR数据通路、NV-DDR2/3命令时序产生电路、NV-DDR2/3地址时序产生电路、NV-DDR2/3数据通路,当由SDR数据接口切换为NV-DDR2数据接口后,SDR的时序产生电路是处于空闲状态的,反之亦然。

对于控制器接口电路的时序产生电路,NAND Flash在SDR数据接口下进行操作时,需要一套命令、地址、数据通路时序产生的电路;同时,在NV-DDR2/3数据接口操作下,也需要一套命令、地址、数据通路时序产生的电路。而从ONFI协议中SDR和NV-DDR2/3接口控制时序图分析,二者功能和时序基本相同,主要区别在于工作频率的不同。但传统设计中,同时存在SDR接口控制电路和DDR2/3接口控制电路,因此即使同一时间只能使用一种数据接口的情况下,另外一种数据接口的控制电路会占用一部分电路资源,产生额外的开销。

基于以上技术问题,本申请实施例提供了一种NAND Flash控制器接口电路及闪存系统,NAND Flash控制器接口电路包括命令地址时序产生电路,其中命令地址时序产生电路可以根据接口选择信号确定目标接口模式对应的时间参数,并根据目标接口模式对应的时间参数,产生目标接口模式对应的命令周期时序和地址周期时序,目标接口模式可以为SDR模式、NV-DDR2模式、NV-DDR3模式中的任意一种,这样命令地址时序产生电路可以根据接口选择信号而确定对应的时间参数,根据多个时间参数而工作在多个目标接口模式之下,实现了电路模块的复用,无需对应多种目标接口模块而设置不同的电路模块,节省电路资源。

如图2所示,为本申请公开的一种NAND Flash控制器接口电路的结构示意图,NANDFlash控制器接口电路200可以包括:

命令地址时序产生电路,用于根据所述接口选择信号确定目标接口模式对应的时间参数,并根据所述目标接口模式对应的时间参数,产生所述目标接口模式对应的命令周期时序和地址周期时序;所述目标接口模式为SDR模式、NV-DDR2模式、NV-DDR3模式中的任意一种。亦即SDR模式、NV-DDR2模式、NV-DDR3模式下可共用一套命令、地址时序产生电路,即前述的命令地址时序产生电路。

本申请实施例中,接口模式可以基于ONFI协议,接口模式可以包括SDR模式、NV-DDR2模式、NV-DDR3模式,这些接口模式中的部分可以互相切换,实现不同的存储需求。每个接口模式下可以包括多个时间模式,每个时间模式下有不同的时间参数,一个时间模式下的时间参数通常为整数个该时间模式下的时钟周期,则每个时间模式可以对应一个时钟周期,不同接口模式下的时间模式不同,时间参数也不同,每个接口模式下产生的命令周期时序和地址周期时序均需要满足该接口模式下的多个时间模式下的时间参数。

其中,不同的时间模式下时间周期有所差别,例如SDR数据接口下时间模式共6种(mode0-mode5),表1为各个时间模式下的时钟周期(tCLK),单位为ns。

表1 SDR数据接口下各个时间模式下的时钟周期

NV-DDR2/3数据接口下的时间模式共13种(mode0-mode12),表2为各个时间模式下的时钟周期(tCLK),单位为ns。

表2 NV-DDR2/3数据接口下各个时间模式下的时钟周期

本申请实施例中,NAND Flash控制器接口电路还可以包括计数器,用于控制各个时间模式下的时间参数,具体的,计数器可以统计时钟周期的数量,这样可以利用计数器的计数结果控制各个时间模式下的时间参数为该时间模式下的时钟周期的整数倍。当然,在一些场景中也可以不使用计数器而通过其他方式控制时间参数。下面对计数器的应用进行举例说明。

以tCS时间参数为例,tCS表示的是CE_n的建立时间,如图3A中tCS所示。表3为tCS在SDR接口模式下需要满足的时间要求。可以看到在所有时间模式下,tCS都需要满足:tCS≥T

表3 tCS需满足的时间要求

现有的控制器设计中不同数据接口下时序产生电路分别由指令、地址、数据通路三部分来实现,在涉及到模式切换的过程中,命令周期、地址周期的时序产生电路分别仅在相应数据接口下的时间内使用。也就是说,对应不同数据接口的不同时序产生电路,现有技术中可以包括SDR命令周期时序、SDR地址周期时序、NV-DDR2/3命令周期时序、NV-DDR2/3地址周期时序四种时序,发明人经过研究发现,这四种时序具有高度类似性。

参考图3所示,为SDR命令周期时序和SDR地址周期时序的示意图,其中,图3A为SDR命令周期时序,图3B为SDR地址周期时序,其中,在SDR数据接口下除了CLE、ALE信号略有不同外,其他的时间参数与时序基本相同。因此,SDR数据接口下命令周期时序和地址周期时序产生的逻辑关系相同,可以将两部分合并为相同的电路模块。

参考图4所示,为NV-DDR2/3命令周期时序和NV-DDR2/3地址周期时序的示意图,其中,图4A为NV-DDR2/3命令周期时序,图4B为NV-DDR2/3地址周期时序。类似于SDR接口模式下的思路,可以使用同一电路模块完成NV-DDR2/3数据接口命令和地址时序的产生。

参考图5所示,为SDR与NV-DDR2/3命令地址时序的示意图,其中,图a为SDR命令周期时序;图b为NV-DDR2/3命令周期时序。对比两图可以看出除了时间参数的不同外,两种接口的信号逻辑关系基本相同,因此两种接口的时序实现可以使用相同的电路模块。

因此,本申请实施例中,可以将SDR命令周期时序、SDR地址周期时序、NV-DDR2/3命令周期时序、NV-DDR2/3地址周期时序这四种时序中的多种的产生电路整合为一个电路模块,例如将SDR命令周期时序、SDR地址周期时序的产生电路整合为同一个电路模块,也可以将NV-DDR2/3命令周期时序、NV-DDR2/3地址周期时序的产生电路整合为同一个电路模块,当然,也可以将这四种时序的产生电路整合为同一个电路模块。

然而,虽然SDR命令周期时序、SDR地址周期时序、NV-DDR2/3命令周期时序、NV-DDR2/3地址周期时序这四种时序高度类似,但在时间模式和具体的时间参数的设定上仍略有不同。因此,在整合的电路模块中添加了可配置的计数器来满足时间模式和时间参数的要求。

由于现有技术中的不同电路模块被整合为同一个电路模块而可以在不同接口模式下复用,因此能够简化电路设计,提高电路的利用率。整合后的电路模块称为命令地址时序产生电路,命令地址时序产生电路能够根据目标接口模式对应的时间参数,产生目标接口模式对应的命令周期时序和地址周期时序,其中目标接口模式为SDR模式、NV-DDR2模式、NV-DDR3模式中的任意一种。

也就是说,在目标接口模式为SDR模式时,命令地址时序产生电路可以产生SDR命令周期时序、SDR地址周期时序,在目标接口模式为NV-DDR2/3模式时,命令地址时序产生电路可以产生NV-DDR2/3命令周期时序、NV-DDR2/3地址周期时序,以此类推。

在NAND Flash控制器接口电路包括计数器的场景下,通过计数器和目标接口模式下的各个时间模式下的时钟周期,可以表征时间参数,时间周期为计数结果和时钟周期的乘积,目标接口模式对应的命令周期时序和地址周期时序满足目标接口模式下的多个时间模式下的时间参数。这样,命令地址时序产生电路可以通过时钟切换和计数器数值的设置而工作在多个目标接口模式的时间参数之下,从而复用在多个目标接口模式之下。

为了能够顺利复用命令地址时序产生电路,在数据接口切换的过程中,需要涉及时钟的切换,因此,本申请实施例中的NAND Flash控制器接口电路可以包括时钟切换电路,时钟切换电路可以根据接口选择信号进行时钟切换,从而使命令地址时序产生电路能够在数据接口切换后得到切换后的目标接口模式的时间参数,这样命令地址时序产生电路可以利用目标接口模式对应的时间参数产生目标接口模式对应的命令周期时序和地址周期时序,产生的目标接口模式对应的命令周期时序和地址周期时序满足目标接口下的多个时间模式下的时间参数。

本申请实施例中,NAND Flash控制器接口电路还可以包括接口选择信号产生单元,用于根据目标接口模式产生接口选择信号,这样时钟切换电路可以根据接口选择信号进行时钟切换。其中,接口选择信号可以为ONFI指令,时钟切换电路可以根据ONFI指令确定目标接口模式对应的时间参数。

目前,当电压VccQ=1.8V,上电初始化完成后进入SDR模式,SDR和NV-DDR2之间可以切换;当电压VccQ=1.2v,上电初始化完成后进入NV-DDR3模式,数据接口不再切换。

具体实施时,在第一接口模式切换为第二接口模式时,可以将第二接口模式作为目标接口模式,即目标接口模式从第一接口模式切换为第二接口模式,目标接口模式的时间参数从第一接口模式的时间参数切换为第二接口模式的时间参数。其中第一接口模式可以为SDR模式,第二接口模式可以为NV-DDR2模式,或者,第一接口模式可以为NV-DDR2模式,第二接口模式可以为SDR模式。

具体实施时,在上电初始化完成后,可以将初始接口模式作为目标接口模式,例如初始接口模式可以为SDR模式或NV-DDR3模式。

下面基于具体的示例对本申请实施例提供的NAND Flash控制器接口电路的工作过程进行介绍。

示例一:SDR模式切换为NV-DDR2模式的场景

参考图6所示,为SDR模式切换为NV-DDR2模式的场景下的NAND Flash控制器接口电路工作过程示意图,其中图6A为现有技术中的NAND Flash控制器接口电路工作过程,图6B为本申请实施例中的NAND Flash控制器接口电路工作过程。

参考图6A所示,在上电初始化后,可以进入SDR模式,现有技术中,根据ONFI指令利用SDR命令周期时序产生电路产生SDR命令周期时序,并利用SDR地址周期时序产生电路产生SDR地址周期时序,并利用SDR数据通路进入SDR数据传输周期,之后可以从SDR模式切换至NV-DDR2模式,根据ONFI指令利用NV-DDR2命令周期时序产生电路产生NV-DDR2命令周期时序,并利用NV-DDR2地址周期时序产生电路产生NV-DDR2地址周期时序,利用NV-DDR2数据通路进入NV-DDR2数据传输周期。

而本申请实施例中,可以将SDR命令周期时序产生电路、SDR地址周期时序产生电路、NV-DDR2命令周期时序产生电路、NV-DDR2地址周期时序产生电路整合成为命令地址时序产生电路,命令地址时序产生电路在SDR模式下可以产生SDR命令周期时序和SDR地址周期时序,在NV-DDR2模式下产生NV-DDR2命令周期时序和NV-DDR2地址周期时序。

具体的,参考图6B所示,在上电初始化后,进入SDR模式,根据ONFI指令利用命令地址时序产生电路产生SDR命令周期时序和SDR地址周期时序,并利用SDR数据通路进入SDR数据传输周期,之后可以从SDR模式切换至NV-DDR2模式,根据ONFI指令进行时钟切换,并复用命令地址时序产生电路产生NV-DDR2命令周期时序和NV-DDR2地址周期时序,利用NV-DDR2数据通路进入NV-DDR2数据传输周期。

示例二:(NV-DDR3)模式的场景

参考图7所示,为NV-DDR3模式的场景下的NAND Flash控制器接口电路工作过程示意图,其中图7A为现有技术中的NAND Flash控制器接口电路工作过程,图7B为本申请实施例中的NAND Flash控制器接口电路工作过程。

参考图7A所示,在上电初始化后,可以进入NV-DDR3模式,现有技术中,根据ONFI指令利用NV-DDR3命令周期时序产生电路产生NV-DDR3命令周期时序,并利用NV-DDR3地址周期时序产生电路产生NV-DDR3地址周期时序,并利用NV-DDR3数据通路进入NV-DDR3数据传输周期。

而本申请实施例中,可以将NV-DDR3命令周期时序产生电路、NV-DDR3地址周期时序产生电路整合成为命令地址时序产生电路,命令地址时序产生电路在NV-DDR3模式下产生NV-DDR3命令周期时序和NV-DDR3地址周期时序。具体的,参考图7B所示,在上电初始化后,进入NV-DDR3模式,根据ONFI指令利用命令地址时序产生电路产生NV-DDR3命令周期时序和SDR地址周期时序,并利用NV-DDR3数据通路进入NV-DDR3数据传输周期。

本申请实施例中,由于SDR,NV-DDR2/3两种数据接口下时间模式对应的时钟周期差别较大。如果复用命令地址时序产生模块,会涉及到从SDR时钟到NV-DDR2/3时钟的切换。且直接切换时钟可能会产生毛刺,出现功能错误,因此本发明引入无毛刺时钟切换电路,用以解决这一问题。一种典型的无毛刺时钟切换电路如图8所示,无论时钟源是否相关,均可以实现无毛刺时钟切换。

具体的,时钟切换电路包括:第一与门电路,第二与门电路,第三与门电路,第四与门电路,第一D触发器、第二D触发器,第三D触发器,第四D触发器,非门电路,或门电路;

所述接口选择信号(SELECT)输入至所述第一与门电路,且通过所述非门电路输入至所述第二与门电路;

所述第一与门电路的输出端连接所述第一D触发器的D端,第一时钟信号(CLK1)输入到所述第一D触发器的时钟输入端,所述第一D触发器的Q端连接所述第二D触发器的D端,所述第一时钟信号的非值输入所述第二D触发器的时钟输入端,所述第二D触发器的Q端连接所述第三与门电路的输入端,所述第一时钟信号输入到所述第三与门电路的输入端;

所述第二与门电路的输出端连接所述第三D触发器的D端,第二时钟信号(CLK2)输入到所述第三D触发器的时钟输入端,所述第三D触发器的Q端链接所述第四D触发器的D端,所述第二始终信号的非值输入所述第四D触发器的时钟输入端,所述第四D触发器的Q端连接所述第四与门电路的输入端,所述第二时钟信号输入到所述第四与门电路的输入端;

所述第二D触发器的Q非端与所述第二与门电路的输入端连接,所述第四D触发器的Q非端与所述第一与门电路的输入端连接;

所述第三与门电路的输出端连接所述或门电路的输入端,所述第四与门电路的输出端连接所述或门电路的输入端,所述或门电路的输出端(CLKOUT)作为所述时钟切换电路的输出端。

当然,以上时钟切换电路仅为示例性的举例,本申请实施例中还可以利用其它时钟切换电路,在此不做赘述。

本申请实施例中,NAND Flash控制器接口电路还可以包括:

SDR数据通路,用于在SDR模式下产生SDR数据输入时序或SDR数据输出时序;

NV-DDR2/NV-DDR3数据通路,用于在NV-DDR2/NV-DDR3模式下产生NV-DDR2/NV-DDR3数据输入时序或NV-DDR2/NV-DDR3数据输出时序。

本申请公开了一种NAND Flash控制器接口电路,NAND Flash控制器接口电路包括命令地址时序产生电路,其中命令地址时序产生电路可以根据接口选择信号确定目标接口模式对应的时间参数,并根据目标接口模式对应的时间参数,产生目标接口模式对应的命令周期时序和地址周期时序,目标接口模式可以为SDR模式、NV-DDR2模式、NV-DDR3模式中的任意一种,这样命令地址时序产生电路可以根据接口选择信号而确定对应的时间参数,根据多个时间参数而工作在多个目标接口模式之下,实现了电路模块的复用,无需对应多种目标接口模块而设置不同的电路模块,节省电路资源。

基于以上实施例提供的一种NAND Flash控制器接口电路,本申请实施例还提供了一种闪存系统,参考图9所示,闪存系统包括NAND Flash闪存单元300、控制器400和前述的NAND Flash控制器接口电路200;所述NAND Flash控制器接口电路200连接所述NAND Flash闪存单元300和所述控制器400。

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例公开的系统而言,由于其与实施例公开的控制器接口电路相对应,所以描述的比较简单,相关之处参见控制器接口电路部分说明即可。

专业人员还可以进一步意识到,结合本文中所公开的实施例描述的各示例的单元及算法步骤,能够以电子硬件、计算机软件或者二者的结合来实现,为了清楚地说明硬件和软件的可互换性,在上述说明中已经按照功能一般性地描述了各示例的组成及步骤。这些功能究竟以硬件还是软件方式来执行,取决于技术方案的特定应用和设计约束条件。专业技术人员可以对每个特定的应用来使用不同方法来实现所描述的功能,但是这种实现不应认为超出本申请的范围。

结合本文中所公开的实施例描述的方法或算法的步骤可以直接用硬件、处理器执行的软件模块,或者二者的结合来实施。软件模块可以置于随机存储器(RAM)、内存、只读存储器(ROM)、电可编程ROM、电可擦除可编程ROM、寄存器、硬盘、可移动磁盘、CD-ROM、或技术领域内所公知的任意其它形式的存储介质中。

对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本申请。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本申请的精神或范围的情况下,在其它实施例中实现。因此,本申请将不会被限制于本文所示的这些实施例,

而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

- 一种NAND Flash控制器接口电路及闪存系统

- 一种NAND闪存控制器的虚拟数据缓存管理系统与方法