一种芯片互连通道阵列的缺陷位置检测方法

文献发布时间:2023-06-19 11:35:49

技术领域

本发明面向集成电路中高速互连的研究领域,涉及集成电路中互连通道的信号完整性分析,具体涉及基于机器学习自检测互连通道阵列中缺陷通道位置。

背景技术

随着人工智能,高性能计算、5G等应用的发展,要求集成电路具备更高的带宽、更快的速率和更小的体积。三维集成以其体积小、性能强、异构集成能力强等优点被认为是最有前途的系统扩展技术。然而,三维集成技术中,垂直高速互连通道提供了最短的芯片间互连以及互连线的最小极板尺寸和间距。从而达到更高集成、更大速率以及更小体积的需求。

为了设计高速数字系统,需要获得互连线之间的寄生耦合噪声,并在合理的串扰和延迟内保证信号的完整性。然而,在三维集成电路中,包含高速互连通道的信号路径会受到较大的噪声影响,相邻的互连通道由于其所处的环境而形成一个复杂的耦合网络。这些耦合网络在相邻的互连通道之间产生了大量的耦合噪声。阵列中具有空洞缺陷通道会对周围通道造成更大的耦合噪声,检测出阵列中的缺陷通道变得十分重要。

通道中的空洞会影响通道的传输性能,导致数据信号在互连通道中传输时误码率升高,影响三维高速互连系统中的信号传输性能和传输质量。同时空洞缺陷的通道在通道阵列中会对周围通道造成很大影响。通过现有的检测技术无法判断阵列中的具有空洞缺陷的通道位置。若因阵列中难以判断空洞缺陷通道位置,从而使得整个阵列的误码率造成大幅降低,影响芯片的传输性能,同时浪费大量的资源,使得芯片的成本增加。

目前在互连通道的检测研究中,大部分的检测技术的主要是针对单通道的缺陷检测,但对于工业生产来说,通道阵列的研究显得十分重要,阵列中缺陷位置与缺陷程度的检测更贴合实际工程应用。本发明在基础上通过机器学习检测缺陷位置,为后续缺陷修复提供了依据。

发明内容

本发明的目的是提供一种针对互连通道阵列缺陷位置的检测方法案。具体涉及一种基于机器学习动态计算通道阵列中缺陷位置的方法。

本发明通过机器学习对互连通道阵列中缺陷位置与误码率、信号频率、信号传输延迟进行数据拟合获得拟合函数,进而通过拟合函数确定互连通道阵列中缺陷所在位置。

为了达到上述目标,本发明首先公开一种动态计算互连通道阵列缺陷位置的方法,包括以下步骤:

基于集成电路版图建立高速互连通道阵列的物理结构模型,在阵列中引入缺陷通道,每个阵列中缺陷通道的位置互不相同。同时保留无缺陷的通道阵列模型进行后续缺陷判断。

首先通过仿真得到不同频率下,无缺陷通道阵列的误码率与传输延迟数据作为缺陷阵列判定标准。进一步地获得不同信号频率下,不同缺陷位置的互连通道阵列的误码率与传输延迟。把所得数据分为两组,利用机器学习对其中一组数据进行训练得到互连通道阵列的误码率、传输延迟、信号频率与阵列中缺陷通道位置之间的拟合函数,再用另外一组数据校验该拟合函数,得到更为准确的拟合函数。

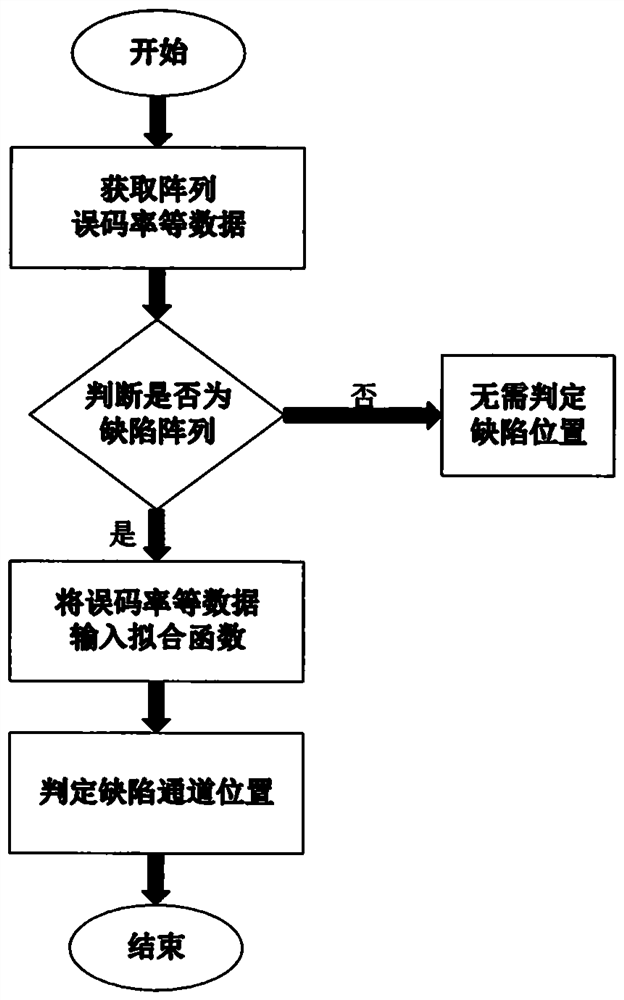

通过上述方法,利用检测出的已知通道的误码率、传输延迟和信号频率,首先对是否具有缺陷进行判定,进而根据拟合函数可以快速计算出互连通道阵列中缺陷通道的位置。

本发明可以通过动态计算分析得到互连通道阵列中缺陷通道位置,便于选择不同的修复方法。提高互连通道阵列的信号传输可靠性,提升整个芯片的性能,能够有效延长互连通道和整个芯片的使用寿命,从而延长设备的使用寿命。

附图说明

图1建立缺陷通道数据拟合函数流程图

图2互连通道阵列缺陷位置检测流程图

具体实施方式

对于阵列中互连通道位置不同会使得周围通道对其产生影响有所不同,误码率的产生主要由于阵列中具有缺陷的通道传输性能差,阵列中具有大量互连通道,因此分析缺陷通道的位置十分关键。

互连通道的缺陷分析对于通道阵列整体信号完整性评估十分重要,有缺陷的通道会对周围通道造成更大耦合影响,从而造成信号传输受损,增加误码率。因此确定缺陷通道位置以便于更好的进行误码修复。提升传输性能。

以下结合附图对本发明提供的基于机器学习的高速互连通道阵列缺陷位置检测方法案作进一步详细描述。

首先根据集成电路版图建立高速互连通道阵列的物理结构模型。传输的互连通道在阵列中位置有所不同,每个传输通道产生缺陷对整体的影响也不同,靠近中心的传输通道产生缺陷对周围通道会产生更大影响。在互连通道中,数据传输的频率也会影响传输过程中的误码率,信号频率越高,相应通道中单位比特长度减小,增加了误判概率,增加了误码率。

因此对误码率的研究需要综合考虑以上因素,假设阵列中通道位置为变量A、信号频率为变量B、通道中的延迟为变量C,则误码率的函数表达式可以表示为Y=f(A,B,C);进一步地用软件进行仿真得到改变缺陷通道位置、信号频率、分析传输延迟与误码率,得到大量关于上述变量的数据集,同时保留无缺陷阵列数据作为标准。仿真时加入一定的高斯白噪声来模拟真实的物理环境。将软件仿真得到的数据随机分为两组,一组用于已经写好的机器学习的算法进行训练学习从而生成变量A、B、C和误码率Y之间的拟合函数Y=f(A,B,C),之后再用剩余的一组仿真数据来验证拟合函数的正确性。最终得到正确的拟合函数。对于未知缺陷位置的阵列,通过无缺陷阵列的标准数据与缺陷检测拟合函数即可检测互连通道阵列中缺陷通道的位置。

上述各例仅用于说明本发明,其具体实现都是可以有所变换的,凡是在本发明技术的核心思想基础上进行的等同变化和改进,均不应排除在本发明的保护范围之外。

- 一种芯片互连通道阵列的缺陷位置检测方法

- 焦平面阵列探测器倒焊芯片内部互连情况的检测方法