一种半导体结构的制备方法、半导体结构和半导体存储器

文献发布时间:2023-06-19 18:32:25

技术领域

本申请涉及半导体工艺领域,尤其涉及一种半导体结构的制备方法、半导体结构和半导体存储器。

背景技术

随着半导体技术的不断发展,半导体的结构越来越复杂。同一个衬底往往根据需要被划分为不同功能的区域,各区域间的纵向结构存在差异,因此,各区域的半导体结构之间存在高度差,给集成电路的加工带来了困难。

在应用HKMG(High-K Metal Gate,高介电常数金属栅极)的半导体结构中,纵向结构变得更加复杂,各区域之间的高度差会更加拉大。在加工过程中,对半导体部分区域的表面结构可能造成过度消除,从而存在凹陷的风险。

发明内容

本申请实施例期望提出一种半导体结构的制备方法、半导体结构和半导体存储器,能够在集成电路加工过程中,避免表面结构的过度消除,降低凹陷风险。

本申请的技术方案是这样实现的:

本申请实施例提供一种半导体结构的制备方法,所述方法包括:

在衬底上形成初始半导体结构;

对所述初始半导体结构进行刻蚀,形成阵列区结构和外围区结构;所述阵列区结构和所述外围区结构在所述衬底上的高度不同;所述外围区结构包括:外围区栅极结构;所述阵列区结构和所述外围区结构均包括:第一介质层;

在所述外围区结构的所述衬底上,形成包围所述外围区栅极结构的隔离墙;

在包含所述隔离墙的所述外围区栅极结构上和所述阵列区结构上,沉积第二介质层;

对所述第二介质层、所述第一介质层和所述隔离墙进行刻蚀,形成表面平坦的半导体结构。

本申请实施例还提供一种半导体结构,由上述方案中的制备方法制备而成。

本申请实施例还提供一种半导体存储器,包括上述方案中的半导体结构。

由此可见,本申请实施例提供了一种半导体结构的制备方法、半导体结构和半导体存储器,能够对衬底上所形成的初始半导体结构进行刻蚀,形成高度不同的阵列区结构和外围区结构;其中,外围区结构中包括了外围区栅极结构,阵列区结构和外围区结构中均包括了第一介质层;而后,在外围区结构的衬底上,形成包围外围区栅极结构的隔离墙;在包含隔离墙的外围区栅极结构上和阵列区结构上,沉积第二介质层;最后,对第二介质层、第一介质层和隔离墙进行刻蚀,形成表面平坦的半导体结构。这样,先形成外围区栅极结构,并沉积第二介质层、第一介质层和隔离墙予以保护,从而,能够避免对半导体表面结构的过度消除,降低了凹陷风险。

附图说明

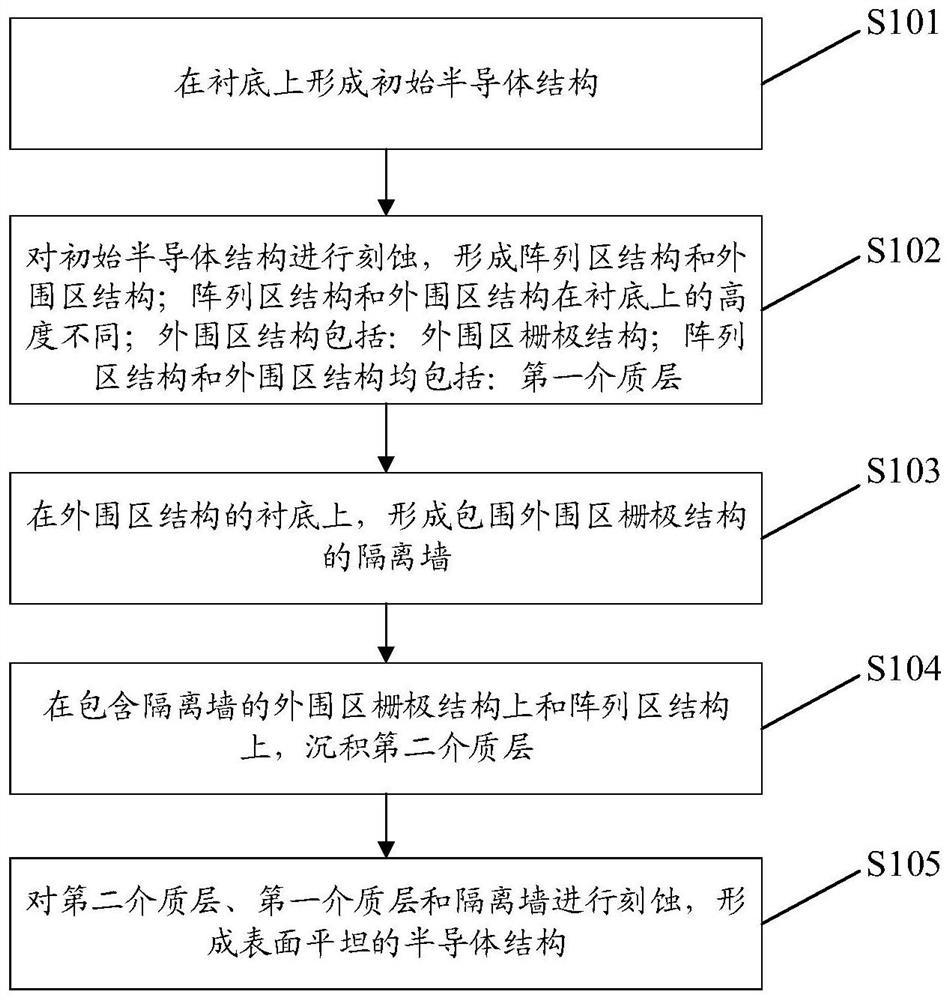

图1为本申请实施例提供的一种半导体结构制备方法的流程图一;

图2为本申请实施例提供的一种半导体结构制备方法的示意图一;

图3为本申请实施例提供的一种半导体结构制备方法的示意图二;

图4为本申请实施例提供的一种半导体结构制备方法的示意图三;

图5为本申请实施例提供的一种半导体结构制备方法的示意图四;

图6为本申请实施例提供的一种半导体结构制备方法的示意图五;

图7为本申请实施例提供的一种半导体结构制备方法的示意图六;

图8为本申请实施例提供的一种半导体结构制备方法的流程图二;

图9为本申请实施例提供的一种半导体结构制备方法的示意图七;

图10为本申请实施例提供的一种半导体结构制备方法的流程图三;

图11为本申请实施例提供的一种半导体结构的剖面示意图;

图12为本申请实施例提供的一种半导体存储器的结构示意图。

具体实施方式

为了使本申请的目的、技术方案和优点更加清楚,下面结合附图和实施例对本申请的技术方案进一步详细阐述,所描述的实施例不应视为对本申请的限制,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本申请保护的范围。

在以下的描述中,涉及到“一些实施例”,其描述了所有可能实施例的子集,但是可以理解,“一些实施例”可以是所有可能实施例的相同子集或不同子集,并且可以在不冲突的情况下相互结合。

如果申请文件中出现“第一/第二”的类似描述则增加以下的说明,在以下的描述中,所涉及的术语“第一/第二/第三”仅仅是区别类似的对象,不代表针对对象的特定排序,可以理解地,“第一/第二/第三”在允许的情况下可以互换特定的顺序或先后次序,以使这里描述的本申请实施例能够以除了在这里图示或描述的以外的顺序实施。

除非另有定义,本文所使用的所有的技术和科学术语与属于本申请的技术领域的技术人员通常理解的含义相同。本文中所使用的术语只是为了描述本申请实施例的目的,不是旨在限制本申请。

在集成电路制造过程中,同一个衬底往往根据需要被划分为不同功能的区域,各区域间的纵向结构存在差异,从而,各区域的半导体结构之间存在高度差。例如,薄型栅结构的栅氧化层厚度比厚型栅结构的栅氧化层厚度少,其厚度差可以为

图1是本申请实施例提供的半导体结构的制备方法的一个可选的流程示意图,将结合图1示出的步骤进行说明。

S101、在衬底上形成初始半导体结构。

本申请实施例中,半导体设备可以先在衬底上形成初始半导体结构。其中,衬底(substrate)是由半导体单晶材料制造而成的晶圆片,通常采用单晶硅材料。

图2是本申请实施例提供的初始半导体结构的剖面示意图,如图2所示,衬底20上形成了初始半导体结构200。衬底20根据实现功能的不同划分了阵列区21、NMOS薄型外围区22、PMOS薄型外围区23、NMOS厚型外围区24和PMOS厚型外围区25。其中,阵列区21上的初始半导体结构包括:第三介质层211、导电层212和第一介质层213;NMOS薄型外围区22上的初始半导体结构包括:栅氧化层221、高介电常数材料层222、导电层223和第一介质层224;PMOS薄型外围区23上的初始半导体结构包括:应变层231、栅氧化层232、高介电常数材料层233、功函数层234、导电层235和第一介质层236;NMOS厚型外围区24上的初始半导体结构包括:栅氧化层241、高介电常数材料层242、导电层243和第一介质层244;PMOS厚型外围区25上的初始半导体结构包括:栅氧化层251、高介电常数材料层252、功函数层253、导电层254和第一介质层255。

可以看出,不同区域上的初始半导体结构并不相同,存在高度差。例如,NMOS薄型外围区22、PMOS薄型外围区23、NMOS厚型外围区24和PMOS厚型外围区25上的初始半导体结构包含了高介电常数材料层222、233、242和252,而阵列区21上的初始半导体结构则并不包含;PMOS薄型外围区23和PMOS厚型外围区25上的初始半导体结构包含功函数层234和253,而阵列区21、NMOS薄型外围区22和NMOS厚型外围区24上的初始半导体结构则并不包含;PMOS薄型外围区23上的初始半导体结构包含应变层231,而其他区域则并不包含;NMOS厚型外围区24和PMOS厚型外围区25上的栅氧化层241和251比NMOS薄型外围区22和PMOS薄型外围区23上的栅氧化层221和232更厚。

另外,不同区域上的导电层212、223、235、243和254可以具有不同的结构或材料,从而也会给不同区域上的初始半导体结构带来高度差异。

在本申请实施例中,半导体设备在衬底20上形成初始半导体结构200可以通过以下过程完成:

首先,在完成栅氧化层221、232、241和251的沉积后,在阵列区21的第三介质层211、以及各外围区22、23、24和25的栅氧化层221、232、241和251上沉积高介电常数材料。并去除第三介质层211上的高介电常数材料,从而留下了各外围区22、23、24和25的高介电常数材料层222、233、242和252。

而后,在阵列区21的第三介质层211、以及各外围区22、23、24和25的高介电常数材料层222、233、242和252上沉积和加工导电材料,从而形成阵列区21以及各外围区22、23、24和25的导电层212、223、235、243和254。

最后,在阵列区21以及各外围区22、23、24和25的导电层212、223、235、243和254上沉积形成第一介质层213、224、236、244和255,从而形成了初始半导体结构200。

在本申请实施例中,半导体设备可以通过扩散(Diffusion)、化学气相沉积(Chemical Vapor Deposition,CVD)和物理气相沉积(Physical Vapor Depos ition,PVD)等多种工艺进行沉积,在此不做限制。

S102、对初始半导体结构进行刻蚀,形成阵列区结构和外围区结构;阵列区结构和外围区结构在衬底上的高度不同;外围区结构包括:外围区栅极结构;阵列区结构和外围区结构均包括:第一介质层。

本申请实施例中,半导体设备可以对初始半导体结构进行刻蚀(Etch),以形成阵列区结构和包括外围区栅极结构的外围区结构。其中,阵列区结构和外围区结构在衬底上的高度不同;阵列区结构和外围区结构均包括了第一介质层。

在本申请实施例中,半导体设备在对初始半导体结构进行刻蚀前,需要在初始半导体结构上形成掩膜层和图案化的光刻胶层。图3是在图2基础上形成了掩膜层和图案化的光刻胶层后的剖面示意图,以图3为例,半导体设备在各区域的第一介质层213、224、236、244和255上形成了掩膜层311、321、331、341和351,而后通过光刻(Photomasking)工艺在掩膜层311、321、331、341和351上形成图案化的光刻胶层312、322、332、342和352。其中,掩膜层311、321、331、341和351用于配合光刻胶层312、322、332、342和352的形成,如增加光刻胶的附着力,防止光刻胶向下渗透等。

需要说明的是,光刻胶层312、322、332、342和352是图案化的,包含了各区域在后续工艺中所要形成的半导体结构的全部平面图案信息,以使得后续工艺能够制造出对应的半导体结构。例如,光刻胶层312将阵列区21剖面顶部全部覆盖,而光刻胶层322、332、342和352则只将各外围区22、23、24和25剖面顶部的中间部分覆盖,因此,阵列区21和各外围区22、23、24和25在后续工艺中形成的半导体结构不同。

掩膜层的形成可以通过扩散、CVD、PVD和旋涂等工艺形成,在此不做限制。

在本申请实施例中,半导体设备在形成了掩膜层和图案化的光刻胶层之后,则可以基于图案化的光刻胶层对掩膜层进行至少一次刻蚀,以形成阵列区结构和外围区结构。图4是在图3基础上进行刻蚀后的剖面示意图,以图4为例,阵列区21以及各外围区22、23、24和25的剖面中间部分由于覆盖了光刻胶层,受到了光刻胶层的保护。光刻胶层覆盖的部分被保留下来,光刻胶层暴露的部分被刻蚀掉。因此,在后续刻蚀过程中未被光刻胶层322、332、342和352覆盖的部分第一介质层213、224、236、244和255被刻蚀掉,也就是说,各外围区22、23、24和25的剖面两侧部分因为没有光刻胶层322、332、342和352的保护,会被刻蚀掉直到衬底20的顶部。这样,如图4所示,各外围区22、23、24和25上便形成了的外围区栅极结构400。

需要说明的是,半导体设备在形成外围区栅极结构400过程中,可以根据外围区22、23、24和25上各层材料,对应采用不同的工艺方法(recipe)进行多次刻蚀。

S103、在外围区结构的衬底上,形成包围外围区栅极结构的隔离墙。

本申请实施例中,半导体设备可以在形成了外围区栅极结构后,在外围区结构的衬底上,形成包围外围区栅极结构的隔离墙。隔离墙用于对外围区栅极结构进行绝缘与保护。

在本申请实施例中,隔离墙的结构可以是N-O-N(SiN-SiO-SiN)结构,即氮化硅-氧化硅-氮化硅结构。图5是在图4基础上形成了隔离墙后的剖面示意图,以图5为例,形成包围各外围区22、23、24和25上的外围区栅极结构的N-O-N结构的隔离墙。其中,隔离墙包括第一氮化硅层521、531、541和551,氧化硅层522、532、542和552,以及第二氮化硅层523、533、543和553。半导体设备可以包围外围区栅极结构,先沉积第一氮化硅层521、531、541和551;再包围第一氮化硅层521、531、541和551,沉积氧化硅层522、532、542和552;最后,包围氧化硅层522、532、542和552,沉积第二氮化硅层523、533、543和553,这样,便形成了N-O-N结构的隔离墙。

在本申请实施例中,半导体设备可以通过扩散、CVD和PVD等多种工艺进行隔离墙的沉积,在此不做限制。

S104、在包含隔离墙的外围区栅极结构上和阵列区结构上,沉积第二介质层。

本申请实施例中,半导体设备可以在包含隔离墙的外围区栅极结构上和阵列区结构上,沉积第二介质层。

图6在图5基础上沉积了第二介质层后的剖面示意图,以图6为例,半导体设备在阵列区21的阵列区结构上,以及各外围区22、23、24和25上的隔离墙外,沉积了第二介质层611、621、631、641和651。第二介质层611、621、631、641和651可以作为消耗材料,在后续消耗工艺中,对其下方的半导体结构形成保护;以及,在各区域间形成隔离区,以将各区域绝缘。

在本申请实施例中,第二介质层的材料可以是氧化硅。半导体设备可以通过扩散、CVD和PVD等多种工艺进行第二介质层的沉积,在此不做限制。

S105、对第二介质层、第一介质层和隔离墙进行刻蚀,形成表面平坦的半导体结构。

本申请实施例中,半导体设备可以对第二介质层、第一介质层和隔离墙进行刻蚀,形成表面平坦的半导体结构,即衬底上各区域的结构高度一致,没有凹陷。

在本申请实施例中,当第一介质层的材料是氮化硅,第二介质层的材料是氧化硅,隔离墙为氮化硅-氧化硅-氮化硅结构时,半导体设备可以按照氧化硅和氮化硅的刻蚀速率比为1:1的方式,对第二介质层、第一介质层和隔离墙进行刻蚀。氧化硅和氮化硅的刻蚀速率比为1:1,意味着在刻蚀过程中,氮化硅材料和氧化硅材料被消耗的速率是相等;这样,在刻蚀过程中,第二介质层、第一介质层和隔离墙被等速率消耗,能始终保证表面的齐平,从而最终形成表面平坦的半导体结构。

在本申请实施例中,为了使氧化硅和氮化硅的刻蚀速率比达到1:1,可以采用特定的工艺方法(recipe)进行刻蚀。该特定工艺方法可以包括:将第一气体按照第一流量通入反应腔、第二气体按照第二流量通入反应腔作为刻蚀气体;在第一压强和第一温度的环境下,将刻蚀气体等离子化,形成等离子体(Plasma);使用等离子体对第二介质层、第一介质层和隔离墙进行第一时长的刻蚀。其中,第一气体可以是四氟化碳,第一流量为80-120sccm(标准毫升/分钟);第二气体可以是氮气,第二流量为180-220sccm;第一压强为3-7torr(托);第一温度为20-50摄氏度,第一温度在第一时长内呈下降趋势;第一时长为20-40秒。

在本申请实施例中,由于衬底上各区域的结构存在高度差,因此,半导体设备可以将各区域结构在衬底上的最低高度作为刻蚀终点,或者,半导体设备可以将阵列区结构中的第一介质层的表面作为刻蚀终点,从而形成表面平坦的半导体结构。图7是在图6基础上进行刻蚀后的剖面示意图,以图7为例,半导体设备以阵列区21上的第一介质层213的表面作为刻蚀终点,各外围区22、23、24和25上的半导体结构均被刻蚀到与刻蚀终点齐平。

可以理解的是,半导体设备先形成外围区栅极结构,并沉积第二介质层、第一介质层和隔离墙予以保护,从而,能够避免对半导体表面结构的过度消除,降低了凹陷风险;同时,按照特定刻蚀速率比对第二介质层、第一介质层和隔离墙,保证了所形成半导体结构的表面平坦。

在本申请的一些实施例中,在图1示出的S104和S105之间还包括图8示出的S801,将结合各步骤进行说明。

S801、对第二介质层进行减薄处理,减少第二介质层的厚度。

本申请实施例,在对第二介质层、第一介质层和隔离墙进行刻蚀之前,半导体设备还可以对第二介质层进行减薄处理,减少第二介质层的厚度。其中,减薄处理可以通过CMP(Chemical Mechanical Polishing,化学机械研磨)工艺来完成,CMP工艺也可以使第二介质层表面更加平坦。图9是在图6基础上进行减薄处理后的剖面示意图,以图9为例,图9对比图6,第二介质层611、621、631、641和651厚度得到了减少。

可以理解的是,在刻蚀前对第二介质层进行减薄处理,可以为后续的刻蚀节约时间和成本。

在本申请的一些实施例中,可以通过图10示出的S1001至S1003来实现图1示出的S102,将结合各步骤进行说明。

S1001、在初始半导体结构上形成掩膜层。

本申请实施例中,半导体设备可以先在初始半导体结构上形成掩膜层。其中,掩膜层用于配合光刻胶层的形成,如增加光刻胶的附着力,防止光刻胶向下渗透等。

在本申请实施例中,掩膜层的形成可以通过扩散、CVD、PVD和旋涂等工艺形成,在此不做限制。

S1002、在掩膜层上形成图案化的光刻胶层。

本申请实施例中,半导体设备可以通过光刻工艺,在掩膜层上形成图案化的光刻胶层。其中,光刻胶层是图案化的,包含了后续工艺中所要形成的半导体结构的全部平面图案信息,以使得后续工艺能够制造出所需的半导体结构。

S1003、基于图案化的光刻胶层对掩膜层进行刻蚀,形成阵列区结构和外围区结构。

本申请实施例中,半导体设备在形成了掩膜层和图案化的光刻胶层之后,则可以基于图案化的光刻胶层对掩膜层进行至少一次刻蚀,以形成阵列区结构和外围区结构。

在本申请的一些实施例中,第一介质层的材料包括氮化硅;第二介质层的材料包括氧化硅;隔离墙包括氮化硅-氧化硅-氮化硅结构。这样,在按照氧化硅和氮化硅的刻蚀速率比为1:1进行刻蚀时,第一介质层、第二介质层和隔离墙被等速率消耗,能始终保证表面的齐平。

在本申请的一些实施例中,外围区栅极结构至少包括第一NMOS结构,第一PMOS结构,第二NMOS结构和第二PMOS结构;阵列区结构、第一NMOS结构,第一PMOS结构,第二NMOS结构和第二PMOS结构在衬底上的高度均可以不同。以图4为例,第一NMOS结构421在NMOS薄型外围区22上,第一PMOS结构431在PMOS薄型外围区23上,第二NMOS结构441在NMOS厚型外围区24上,第二PMOS结构451在PMOS厚型外围区25上,阵列区结构411则在阵列区21上;阵列区结构411、第一NMOS结构421,第一PMOS结构431,第二NMOS结构441和第二PMOS结构451在衬底上的高度均可以不同。

在本申请的一些实施例中,可以通过S1051来实现图1示出的S105,将结合各步骤进行说明。

S1051、以阵列区结构、包含隔离墙的第一NMOS结构,包含隔离墙的第一PMOS结构,包含隔离墙的第二NMOS结构和包含隔离墙的第二PMOS结构在衬底上的最低高度为刻蚀终点,形成表面平坦的半导体结构。

本申请实施例中,半导体设备可以将阵列区结构、包含隔离墙的第一NMOS结构,包含隔离墙的第一PMOS结构,包含隔离墙的第二NMOS结构和包含隔离墙的第二PMOS结构在衬底上的最低高度作为刻蚀终点,来形成表面平坦的半导体结构。

在本申请的一些实施例中,可以通过S1052来实现图1示出的S105,将结合各步骤进行说明。

S1052、以阵列区结构中的第一介质层的表面为刻蚀终点,形成表面平坦的半导体结构。

本申请实施例中,半导体设备可以将阵列区结构中的第一介质层的表面作为刻蚀终点,来形成表面平坦的半导体结构。

在本申请的一些实施例中,可以通过S1053来实现图1示出的S105,将结合各步骤进行说明。

S3053、按照氧化硅和氮化硅刻蚀的速率比,对第二介质层、第一介质层和隔离墙进行刻蚀。

本申请实施例中,半导体设备可以按照氧化硅和氮化硅刻蚀的速率比,对第二介质层、第一介质层和隔离墙进行刻蚀,以使得半导体结构表面保持平坦。

在本申请的一些实施例中,可以通过S1054来实现图1示出的S105,将结合各步骤进行说明。

S1054、使用包含第一气体和第二气体的刻蚀气体,在第一压强和第一温度的环境下,对第二介质层、第一介质层和隔离墙进行第一时长的刻蚀;其中,第一气体按照第一流量通入反应腔,第二气体按照第二流量通入反应腔。

本申请实施例中,半导体设备可以将第一气体按照第一流量通入反应腔、第二气体按照第二流量通入反应腔作为刻蚀气体;在第一压强和第一温度的环境下,将刻蚀气体等离子化,形成等离子体;使用等离子体对第二介质层、第一介质层和隔离墙进行第一时长的刻蚀。

在本申请的一些实施例中,氧化硅和氮化硅刻蚀的速率比为1:1。这样,半导体设备在对氮化硅材料的第一介质层、氧化硅材料的第二介质层和氮化硅-氧化硅-氮化硅结构的隔离墙进行刻蚀时,能够使得半导体结构表面保持平坦。

在本申请的一些实施例中,第一气体包括四氟化碳,第一流量为80-120标准毫升/分钟;第二气体包括氮气,第二流量为180-220标准毫升/分钟;第一压强为3-7托;第一温度为20-50摄氏度,第一温度在第一时长内呈下降趋势;第一时长为20-40秒。

在本申请的一些实施例中,阵列区结构还包括:第三介质层;外围区结构还包括:高介电常数层和栅氧化层;阵列区结构和外围区结构还均包括:导电层。以图4为例,阵列区结构411包括了第三介质层211;各外围区22、23、24和25上的外围区结构包括了高介电常数层222、233、242和252,以及栅氧化层221、232、241和251;阵列区结构411和外围区结构还包括了各种导电材料形成的导电层212、223、235、243和254。

在本申请的一些实施例中,第一PMOS结构还包括功函数层和应变层,第二PMOS结构还包括功函数层。以图4为例,PMOS薄型外围区23上形成第一PMOS结构431,第一PMOS结构431中还包括了功函数层234、以及应变层231。PMOS厚型外围区25上形成第二PMOS结构451,第二PMOS结构451中还包括了功函数层253。

在本申请的一些实施例中,导电层的材料包括钨、氮化钛、多晶硅或氧化镧中的一种或多种;第三介质层的材料包括氮化硅;栅氧化层的材料包括氧化硅;功函数层的材料包括氧化铝;应变层的材料包括锗化硅。

需要说明的是,不同区域上的导电层可以具有不同的结构或材料,从而也会给不同区域上的初始半导体结构带来高度差异。

在本申请的一些实施例中,第一介质层采用热处理法进行沉积;第二介质层为旋涂介质层。

本申请实施例还提供了一种半导体结构110,如图11所示。半导体结构110由前述实施例提供的制备方法制备而成,从而,能够避免对半导体表面结构的过度消除,降低了凹陷风险;同时,按照特定刻蚀速率比进行刻蚀,保证了所形成半导体结构110的表面平坦。

本申请实施例还提供了一种半导体存储器120,如图12所示,半导体存储器120至少包括图11示出的半导体结构110。

在本申请的一些实施例中,图12示出的半导体存储器120至少包括动态随机存取存储器DRAM。

需要说明的是,在本申请中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括该要素的过程、方法、物品或者装置中还存在另外的相同要素。

上述本申请实施例序号仅仅为了描述,不代表实施例的优劣。本申请所提供的几个方法实施例中所揭露的方法,在不冲突的情况下可以任意组合,得到新的方法实施例。本申请所提供的几个产品实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的产品实施例。本申请所提供的几个方法或设备实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的方法实施例或设备实施例。

以上所述,仅为本申请的具体实施方式,但本申请的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本申请揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本申请的保护范围之内。因此,本申请的保护范围应以所述权利要求的保护范围为准。

- 一种半导体存储器的器件结构及其制造方法

- 一种半导体量子点-液晶复合结构器件的制备方法

- 一种对半导体表面过饱和掺杂且保持其晶格结构的制备方法

- 一种含醌式结构的聚合物半导体及其制备和应用

- 一种半导体结构、半导体结构的制备方法和半导体存储器

- 一种半导体结构、半导体结构的制备方法和半导体存储器