像素和显示装置

文献发布时间:2023-06-19 19:14:59

技术领域

实施例涉及一种像素和一种包括像素的显示装置。具体地,实施例涉及一种支持可变频率驱动的像素和一种包括像素的显示装置。

背景技术

通常,显示装置可以包括显示面板和显示面板驱动器。显示面板可以包括栅极线、数据线、发射线和像素。显示面板驱动器可以包括配置为将栅极信号提供到栅极线的栅极驱动器、配置为将数据电压提供到数据线的数据驱动器、配置为将发射信号提供到发射线的发射驱动器以及配置为控制栅极驱动器、数据驱动器和发射驱动器的驱动控制器。

支持可变频率驱动的显示装置可以包括包含多晶硅薄膜晶体管和氧化物薄膜晶体管的像素。当包括在像素中的晶体管之中的氧化物薄膜晶体管的比例高时,像素内部的电容器的电容可能降低,并且显示面板的极限每英寸像素(ppi)可能降低,使得显示面板的分辨率可能降低。

发明内容

实施例提供一种像素,所述像素用于通过使包括在像素中的氧化物薄膜晶体管的数量最小化(或减少)来增加显示面板的分辨率。

实施例提供一种包括像素的显示装置,所述像素用于通过使包括在像素中的氧化物薄膜晶体管的数量最小化来增加显示面板的分辨率。

根据实施例的像素可以包括:发光元件;数据写入晶体管,写入数据电压;驱动晶体管,基于所述数据电压将驱动电流施加到所述发光元件;保持电容器,包括:第一电源电压施加到的第一电极;和电连接到第一节点的第二电极;存储电容器,包括:电连接到所述第一节点的第一电极;和电连接到所述驱动晶体管的控制电极的第二电极;至少一个多晶硅薄膜晶体管;以及至少一个氧化物薄膜晶体管。所述至少一个氧化物薄膜晶体管可以设置在所述至少一个多晶硅薄膜晶体管与所述保持电容器之间或者设置在所述至少一个多晶硅薄膜晶体管与所述存储电容器之间。

在实施例中,所述至少一个氧化物薄膜晶体管可以包括:第一氧化物薄膜晶体管,包括:第一补偿栅极信号施加到的控制电极;电连接到所述驱动晶体管的所述控制电极的第一电极;和电连接到所述至少一个多晶硅薄膜晶体管的第二电极;以及第二氧化物薄膜晶体管,包括:所述第一补偿栅极信号施加到的控制电极;电连接到所述第一节点的第一电极;和电连接到所述至少一个多晶硅薄膜晶体管的第二电极。

在实施例中,所述第一氧化物薄膜晶体管的所述控制电极和所述第二氧化物薄膜晶体管的所述控制电极可以电连接到第一补偿栅极线,所述第一补偿栅极信号传输到所述第一补偿栅极线。

在实施例中,所述像素还可以包括:升压电容器,包括:电连接到所述第一节点的第一电极;和升压信号施加到的第二电极。

在实施例中,所述驱动晶体管可以包括第一晶体管,所述第一晶体管包括:电连接到第二节点的控制电极;所述第一电源电压施加到的第一电极;和电连接到第三节点的第二电极。所述数据写入晶体管可以包括第二晶体管,所述第二晶体管包括:数据写入栅极信号施加到的控制电极;所述数据电压施加到的第一电极;和电连接到第四节点的第二电极。

在实施例中,所述至少一个多晶硅薄膜晶体管可以包括:第三晶体管,包括:第二补偿栅极信号施加到的控制电极;电连接到第五节点的第一电极;和电连接到所述第三节点的第二电极;第四晶体管,包括:数据初始化栅极信号施加到的控制电极;数据初始化电压施加到的第一电极;和电连接到所述第五节点的第二电极;第五晶体管,包括:所述第二补偿栅极信号施加到的控制电极;参考电压施加到的第一电极;和电连接到所述第四节点的第二电极;第六晶体管,包括:发射信号施加到的控制电极;电连接到所述第三节点的第一电极;和电连接到所述发光元件的阳极电极的第二电极;以及第七晶体管,包括:发光元件初始化栅极信号施加到的控制电极;发光元件初始化电压施加到的第一电极;和电连接到所述发光元件的所述阳极电极的第二电极。

在实施例中,所述第一氧化物薄膜晶体管可以包括第八晶体管,所述第八晶体管包括:所述第一补偿栅极信号施加到的控制电极;电连接到所述第四节点的第一电极;和电连接到所述第一节点的第二电极。所述第二氧化物薄膜晶体管可以包括第九晶体管,所述第九晶体管包括:所述第一补偿栅极信号施加到的控制电极;电连接到所述第二节点的第一电极;和电连接到所述第五节点的第二电极。

在实施例中,第N帧可以包括:数据写入时段,在所述数据写入时段中,写入所述数据电压;和自扫描时段,在所述自扫描时段中,不写入所述数据电压。在所述数据写入时段中,所述第一补偿栅极信号可以具有激活时段,其中,N为正整数。

在实施例中,在所述激活时段中,所述第一补偿栅极信号可以具有激活电平。在所述第一补偿栅极信号的所述激活时段中,所述数据写入栅极信号可以具有至少一个有效脉冲,所述第二补偿栅极信号可以具有至少一个有效脉冲,并且所述数据初始化栅极信号可以具有至少一个有效脉冲。

在实施例中,所述数据写入时段和所述自扫描时段可以包括偏置时段。在所述偏置时段中,所述数据写入栅极信号可以具有禁用电平,所述第一补偿栅极信号可以具有禁用电平,所述数据初始化栅极信号可以具有禁用电平,并且所述升压信号可以具有激活电平。

在实施例中,在所述自扫描时段中,所述数据初始化栅极信号可以具有至少一个有效脉冲。

在实施例中,所述像素还可以包括:升压电容器,包括:电连接到所述驱动晶体管的所述控制电极的第一电极;和升压信号施加到的第二电极。

根据实施例的像素可以包括:发光元件;保持电容器,包括:第一电源电压施加到的第一电极;和电连接到第一节点的第二电极;存储电容器,包括:电连接到所述第一节点的第一电极;和电连接到第二节点的第二电极;第一晶体管,包括:电连接到所述第二节点的控制电极;所述第一电源电压施加到的第一电极;和电连接到第三节点的第二电极;第二晶体管,包括:数据写入栅极信号施加到的控制电极;数据电压施加到的第一电极;和电连接到第四节点的第二电极;第三晶体管,包括:第二补偿栅极信号施加到的控制电极;电连接到第五节点的第一电极;和电连接到所述第三节点的第二电极;第四晶体管,包括:数据初始化栅极信号施加到的控制电极;数据初始化电压施加到的第一电极;和电连接到所述第五节点的第二电极;第五晶体管,包括:所述第二补偿栅极信号施加到的控制电极;参考电压施加到的第一电极;和电连接到所述第四节点的第二电极;第六晶体管,包括:发射信号施加到的控制电极;电连接到所述第三节点的第一电极;和电连接到所述发光元件的阳极电极的第二电极;第七晶体管,包括:发光元件初始化栅极信号施加到的控制电极;发光元件初始化电压施加到的第一电极;和电连接到所述发光元件的所述阳极电极的第二电极;第八晶体管,包括:第一补偿栅极信号施加到的控制电极;电连接到所述第四节点的第一电极;和电连接到所述第一节点的第二电极;以及第九晶体管,包括:所述第一补偿栅极信号施加到的控制电极;电连接到所述第二节点的第一电极;和电连接到所述第五节点的第二电极。所述第一晶体管至所述第七晶体管可以为多晶硅薄膜晶体管,并且所述第八晶体管和所述第九晶体管可以为氧化物薄膜晶体管。

在实施例中,所述像素还可以包括:升压电容器,包括:电连接到所述第一节点的第一电极;和升压信号施加到的第二电极。

在实施例中,所述像素还可以包括:升压电容器,包括:电连接到所述第二节点的第一电极;和升压信号施加到的第二电极。

根据实施例的显示装置可以包括:显示面板,包括像素;栅极驱动器,将栅极信号提供到所述像素;数据驱动器,将数据电压提供到所述像素;以及发射驱动器,将发射信号提供到所述像素。所述像素可以包括:发光元件;数据写入晶体管,写入所述数据电压;驱动晶体管,基于所述数据电压将驱动电流施加到所述发光元件;保持电容器,包括:第一电源电压施加到的第一电极;和电连接到第一节点的第二电极;存储电容器,包括:电连接到所述第一节点的第一电极;和电连接到所述驱动晶体管的控制电极的第二电极;至少一个多晶硅薄膜晶体管;以及至少一个氧化物薄膜晶体管,并且所述至少一个氧化物薄膜晶体管设置在所述至少一个多晶硅薄膜晶体管与所述保持电容器之间或者设置在所述至少一个多晶硅薄膜晶体管与所述存储电容器之间。

在实施例中,所述至少一个氧化物薄膜晶体管可以包括:第一氧化物薄膜晶体管,包括:第一补偿栅极信号施加到的控制电极;电连接到所述驱动晶体管的所述控制电极的第一电极;和电连接到所述至少一个多晶硅薄膜晶体管的第二电极;以及第二氧化物薄膜晶体管,包括:所述第一补偿栅极信号施加到的控制电极;电连接到所述第一节点的第一电极;和电连接到所述至少一个多晶硅薄膜晶体管的第二电极。

在实施例中,所述第一氧化物薄膜晶体管的所述控制电极和所述第二氧化物薄膜晶体管的所述控制电极可以电连接到第一补偿栅极线,所述第一补偿栅极信号传输到所述第一补偿栅极线。

在实施例中,所述像素还可以包括:升压电容器,包括:电连接到所述第一节点的第一电极;和升压信号施加到的第二电极。所述驱动晶体管可以包括第一晶体管,所述第一晶体管包括:电连接到第二节点的控制电极;所述第一电源电压施加到的第一电极;和电连接到第三节点的第二电极。所述数据写入晶体管可以包括第二晶体管,所述第二晶体管包括:数据写入栅极信号施加到的控制电极;所述数据电压施加到的第一电极;和电连接到第四节点的第二电极。

在实施例中,所述至少一个多晶硅薄膜晶体管可以包括:第三晶体管,包括:第二补偿栅极信号施加到的控制电极;电连接到第五节点的第一电极;和电连接到所述第三节点的第二电极;第四晶体管,包括:数据初始化栅极信号施加到的控制电极;数据初始化电压施加到的第一电极;和电连接到所述第五节点的第二电极;第五晶体管,包括:所述第二补偿栅极信号施加到的控制电极;参考电压施加到的第一电极;和电连接到所述第四节点的第二电极;第六晶体管,包括:所述发射信号施加到的控制电极;电连接到所述第三节点的第一电极;和电连接到所述发光元件的阳极电极的第二电极;以及第七晶体管,包括:发光元件初始化栅极信号施加到的控制电极;发光元件初始化电压施加到的第一电极;和电连接到所述发光元件的所述阳极电极的第二电极。所述第一氧化物薄膜晶体管可以包括第八晶体管,所述第八晶体管包括:所述第一补偿栅极信号施加到的控制电极;电连接到所述第四节点的第一电极;和电连接到所述第一节点的第二电极。所述第二氧化物薄膜晶体管可以包括第九晶体管,所述第九晶体管包括:所述第一补偿栅极信号施加到的控制电极;电连接到所述第二节点的第一电极;和电连接到所述第五节点的第二电极。

根据上述像素和显示装置,在支持可变频率驱动的显示装置中,可以使包括在像素中的氧化物薄膜晶体管的数量最小化(或减少)。因此,包括在像素中的晶体管之中的氧化物薄膜晶体管的比例可以降低,使得像素中的电容器的电容可以增加,并且显示面板的极限ppi可以增加。结果,在支持可变频率驱动的显示装置中,可以提高显示面板的分辨率。

附图说明

通过以下结合附图进行的描述,本公开的特定实施例的以上和其它方面、特征和优点将更加明显,在附图中:

图1是示出根据本公开的实施例的显示装置的示意性框图;

图2是示出图1的显示面板的驱动频率的示意性概念图;

图3是示出包括在图1的显示面板中的像素的驱动信号的示意性时序图;

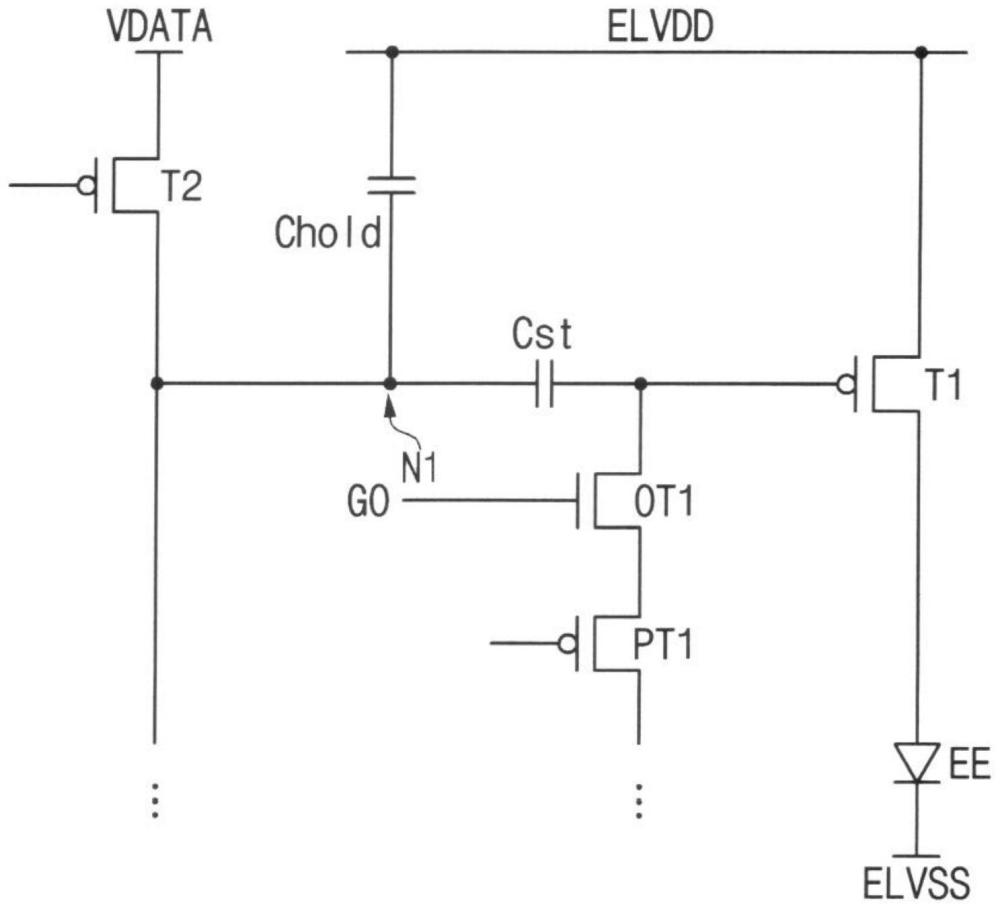

图4是示出包括在图1的显示面板中的像素的一部分的等效电路的示意图;

图5是示出图4的像素的一部分的等效电路的示意图;

图6是示出图4的像素的示例的等效电路的示意图;

图7是示出在数据写入时段中施加到图4的像素的输入信号和节点电压的示意性时序图;

图8是示出在自扫描时段中施加到图4的像素的输入信号和节点电压的示例的示意性时序图;

图9是示出在自扫描时段中施加到图4的像素的输入信号和节点电压的另一示例的示意性时序图;

图10是示出图4的像素的示例的等效电路的示意图;

图11是示出根据本公开的实施例的像素的等效电路的示意图;

图12是示出根据本公开的实施例的像素的等效电路的示意图;

图13是示出图12的像素的示意性布局图;

图14是示出根据本公开的实施例的像素的等效电路的示意图;

图15是示出根据本公开的实施例的电子装置的示意性框图;以及

图16是示出图15的电子装置被实现为智能电话的示例的示意图。

具体实施例

当元件或层被称为“在”另一元件或层“上”、“连接到”或“耦接到”另一元件或层时,所述元件或层可以直接在所述另一元件或层上、直接连接到或直接耦接到所述另一元件或层,或者可以存在居间元件或居间层。然而,当元件或层被称为“直接在”另一元件或层“上”、“直接连接到”或“直接耦接到”另一元件或层时,不存在居间元件或居间层。为此,术语“连接”可以指代具有或不具有居间元件的物理连接、电连接和/或流体连接。

考虑到讨论中的测量和与特定量的测量相关的误差(即,测量系统的局限性),如本文中所使用的术语“大约”或“近似”包括所陈述的值,并且指在如由本领域普通技术人员所确定的特定值的可接受的偏差范围之内。例如,“大约”可以指在一个或多个标准偏差内,或者在所陈述的值的±30%、±20%、±10%或±5%之内。

出于其含义和解释的目的,短语“……中的至少一个”旨在包括“选自……的组中的至少一个”的含义。例如,“A和B中的至少一个”可以被理解为表示“A、B、或者A和B”。

除非在本文中另有定义或暗示,否则本文中所使用的所有术语(包括技术术语和科学术语)具有与本公开所属领域中的技术人员所通常理解的相同的含义。将进一步理解的是,除非在本文中明确地如此定义,否则术语(诸如在通用词典中限定的术语)应当被解释为具有与它们在相关领域的背景和本公开中的含义相一致的含义,并且不应当以理想化的或过于形式化的含义来解释所述术语。

图1是示出根据本公开的实施例的显示装置的示意性框图。

参考图1,显示装置可以包括显示面板100和显示面板驱动器。显示面板驱动器可以包括驱动控制器200、栅极驱动器300、伽马参考电压发生器400、数据驱动器500和发射驱动器600。

显示面板100可以包括用于显示图像的显示部分以及邻近于显示部分的外围部分。

显示面板100可以包括栅极线GWL、GOL、GCL、GIL和EBL、数据线DL、发射线EML以及电连接到栅极线GWL、GOL、GCL、GIL和EBL、数据线DL和发射线EML的像素。栅极线GWL、GOL、GCL、GIL和EBL可以在第一方向D1上延伸,数据线DL可以在与第一方向D1相交的第二方向D2上延伸,并且发射线EML可以在第一方向D1上延伸。

驱动控制器200可以从外部装置接收输入图像数据IMG和输入控制信号CONT。例如,输入图像数据IMG可以包括红色图像数据、绿色图像数据和蓝色图像数据。输入图像数据IMG可以包括白色图像数据。例如,输入图像数据IMG可以包括品红色图像数据、黄色图像数据和青色图像数据。输入控制信号CONT可以包括主时钟信号和数据使能信号。输入控制信号CONT还可以包括垂直同步信号和水平同步信号。

驱动控制器200可以基于输入图像数据IMG和输入控制信号CONT生成第一控制信号CONT1、第二控制信号CONT2、第三控制信号CONT3、第四控制信号CONT4和数据信号DATA。

驱动控制器200可以基于输入控制信号CONT生成用于控制栅极驱动器300的操作的第一控制信号CONT1,并且将生成的第一控制信号CONT1输出到栅极驱动器300。第一控制信号CONT1可以包括垂直起始信号和栅极时钟信号。

驱动控制器200可以基于输入控制信号CONT生成用于控制数据驱动器500的操作的第二控制信号CONT2,并且将生成的第二控制信号CONT2输出到数据驱动器500。第二控制信号CONT2可以包括水平起始信号和负载信号。

驱动控制器200可以基于输入图像数据IMG生成数据信号DATA。驱动控制器200可以将数据信号DATA输出到数据驱动器500。

驱动控制器200可以基于输入控制信号CONT生成用于控制伽马参考电压发生器400的操作的第三控制信号CONT3,并且将生成的第三控制信号CONT3输出到伽马参考电压发生器400。

驱动控制器200可以基于输入控制信号CONT生成用于控制发射驱动器600的操作的第四控制信号CONT4,并且将生成的第四控制信号CONT4输出到发射驱动器600。

栅极驱动器300可以响应于从驱动控制器200接收的第一控制信号CONT1生成用于驱动栅极线GWL、GOL、GCL、GIL和EBL的栅极信号。栅极驱动器300可以将栅极信号输出到栅极线GWL、GOL、GCL、GIL和EBL。

伽马参考电压发生器400可以响应于从驱动控制器200接收的第三控制信号CONT3生成伽马参考电压VGREF。伽马参考电压发生器400可以将伽马参考电压VGREF提供到数据驱动器500。伽马参考电压VGREF可以具有对应于每个数据信号DATA的值。

例如,伽马参考电压发生器400可以设置在驱动控制器200或数据驱动器500中。

数据驱动器500可以从驱动控制器200接收第二控制信号CONT2和数据信号DATA,并且从伽马参考电压发生器400接收伽马参考电压VGREF。数据驱动器500可以通过使用伽马参考电压VGREF将数据信号DATA转换成模拟数据电压。数据驱动器500可以将数据电压输出到数据线DL。

发射驱动器600可以响应于从驱动控制器200接收的第四控制信号CONT4生成用于驱动发射线EML的发射信号。发射驱动器600可以将发射信号输出到发射线EML。

尽管为了便于描述,图1示出了栅极驱动器300设置在显示面板100的第一侧,并且发射驱动器600设置在显示面板100的第二侧,但是本公开不限于此。例如,栅极驱动器300和发射驱动器600两者可以设置在显示面板100的第一侧。例如,栅极驱动器300和发射驱动器600可以彼此一体(或者可以彼此一体地形成)。

图2是示出图1的显示面板100的驱动频率的示意性概念图,并且图3是示出包括在图1的显示面板100中的像素的驱动信号的示意性时序图。

参考图1至图3,可以以可变频率驱动显示面板100。例如,可以以大约240Hz驱动显示面板100。例如,可以以大约120Hz驱动显示面板100。具有第一频率的第一帧FR1可以包括第一有效时段AC1和第一消隐时段BL1。具有与第一频率不同的第二频率的第二帧FR2可以包括第二有效时段AC2和第二消隐时段BL2。具有与第一频率和第二频率中的每一者不同的第三频率的第三帧FR3可以包括第三有效时段AC3和第三消隐时段BL3。

第一有效时段AC1和第二有效时段AC2可以具有相同的长度,并且第一消隐时段BL1和第二消隐时段BL2可以具有不同的长度。第二有效时段AC2和第三有效时段AC3可以具有相同的长度,并且第二消隐时段BL2和第三消隐时段BL3可以具有不同的长度。

在以大约240Hz驱动显示面板100的情况下,数据写入栅极信号GW可以在第一时段P1、第三时段P3、第五时段P5和第七时段P7中具有有效脉冲以执行数据写入操作。在以大约120Hz驱动显示面板100的情况下,数据写入栅极信号GW可以在第一时段P1、第五时段P5和第七时段P7中具有有效脉冲以执行数据写入操作。

例如,在以大约240Hz驱动显示面板100的情况下,可以以大约480Hz执行包括在像素中的发光元件的发射操作EM。在以大约240Hz驱动显示面板100的情况下,可以以大约480Hz执行包括在像素中的驱动晶体管的偏置操作BIAS。在以大约240Hz驱动显示面板100的情况下,可以以大约480Hz执行包括在像素中的发光元件的初始化操作BCB。如上所述,在以大约240Hz驱动显示面板100并且以大约480Hz执行发射操作EM的情况下,显示面板100可以以两个周期(例如,相对于驱动周期)操作(例如,发光)。

例如,在以大约120Hz驱动显示面板100的情况下,可以以大约480Hz执行包括在像素中的发光元件的发射操作EM。在以大约120Hz驱动显示面板100的情况下,可以以大约480Hz执行驱动晶体管的偏置操作BIAS。在以大约120Hz驱动显示面板100的情况下,可以以大约480Hz执行包括在像素中的发光元件的初始化操作BCB。如上所述,在以大约120Hz驱动显示面板100并且以大约480Hz执行发射操作EM的情况下,显示面板100可以以四个周期(例如,相对于驱动周期)操作(例如,发光)。

尽管上面参照图3仅描述了显示面板100的驱动频率是大约240Hz和大约120Hz,但是根据本公开的显示面板100的驱动频率不限于此。例如,显示面板100的驱动频率可以是大约160Hz、大约96Hz、大约80Hz、大约68Hz或大约60Hz等。

支持可变频率的显示装置的操作时段可以包括数据电压被写入像素中的数据写入时段和数据电压不被写入像素中的自扫描时段。例如,在自扫描时段中,可以在没有数据写入操作的情况下执行驱动晶体管的偏置操作BIAS。数据写入时段可以布置在有效时段(例如,第一有效时段AC1、第二有效时段AC2和第三有效时段AC3)中。自扫描时段可以布置在消隐时段(例如,第一消隐时段BL1、第二消隐时段BL2和第三消隐时段BL3)中。

支持可变频率驱动的传统显示装置可以使用包括多晶硅薄膜晶体管和氧化物薄膜晶体管的像素,以便使像素内部的漏电流最小化。然而,在包括在像素中的晶体管之中的氧化物薄膜晶体管的比例高的情况下,像素内部的电容器的电容可能降低,并且显示面板的极限每英寸像素(ppi)可能减少,使得显示面板的分辨率可能降低。为了解决这样的问题,根据实施例的支持可变频率的显示装置,可以在多晶硅薄膜晶体管与保持电容器之间或在多晶硅薄膜晶体管与存储电容器之间设置至少一个氧化物薄膜晶体管,使得可以使包括在像素中的氧化物薄膜晶体管的数量最小化。因此,包括在像素中的晶体管之中的氧化物薄膜晶体管的比例可以降低,使得像素内部的电容器的电容可以增加,并且显示面板的极限ppi可以增加。结果,根据支持可变频率的显示装置,显示面板的分辨率可以提高。

图4是示出包括在图1的显示面板100中的像素的一部分的等效电路的示意图,图5是示出图4的像素的一部分的等效电路的示意图,图6是示出图4的像素的示例的等效电路的示意图,图7是示出在数据写入时段中施加到图4的像素的输入信号和节点电压的示意性时序图,图8是示出在自扫描时段中施加到图4的像素的输入信号和节点电压的示例的示意性时序图,并且图9是示出在自扫描时段中施加到图4的像素的输入信号和节点电压的另一示例的示意性时序图。

参考图4,像素可以包括发光元件EE、数据写入晶体管(例如,T2)、驱动晶体管(例如,T1)、保持电容器Chold、存储电容器Cst和第一氧化物薄膜晶体管OT1。发光元件EE可以包括阴极电极和阳极电极。数据写入晶体管(例如,T2)可以在数据写入时段中写入数据电压VDATA。驱动晶体管(例如,T1)可以基于数据电压VDATA将驱动电流施加到发光元件EE。保持电容器Chold可以包括第一电源电压ELVDD所施加到的第一电极和电连接到第一节点N1的第二电极。存储电容器Cst可以包括电连接到第一节点N1的第一电极和电连接到驱动晶体管的控制电极的第二电极。第一氧化物薄膜晶体管OT1可以包括第一补偿栅极信号GO所施加到的控制电极、电连接到驱动晶体管的控制电极的第一电极以及电连接到至少一个多晶硅薄膜晶体管(例如,PT1)的第二电极。例如,第一氧化物薄膜晶体管OT1可以是氧化物薄膜晶体管,并且驱动晶体管和数据写入晶体管可以是多晶硅薄膜晶体管。

参考图5,像素还可以包括第二氧化物薄膜晶体管OT2。第二氧化物薄膜晶体管OT2可以包括第一补偿栅极信号GO所施加到的控制电极、电连接到第一节点N1的第一电极以及电连接到至少一个多晶硅薄膜晶体管的第二电极。例如,第一氧化物薄膜晶体管OT1和第二氧化物薄膜晶体管OT2可以是氧化物薄膜晶体管,并且驱动晶体管和数据写入晶体管可以是多晶硅薄膜晶体管。

第一氧化物薄膜晶体管OT1的控制电极可以电连接到第一补偿栅极线GOL(参见图1)。第二氧化物薄膜晶体管OT2的控制电极可以电连接到第一补偿栅极线GOL。第一氧化物薄膜晶体管OT1的控制电极和第二氧化物薄膜晶体管OT2的控制电极可以接收来自相同的第一补偿栅极线GOL的第一补偿栅极信号GO。换句话说,像素可以通过使用水平线将第一补偿栅极信号GO传输到第一氧化物薄膜晶体管OT1和第二氧化物薄膜晶体管OT2。

参考图6,根据实施例,像素还可以包括升压电容器CB,升压电容器CB包括电连接到第一节点N1的第一电极和升压信号EB所施加到的第二电极。

像素可以包括第一晶体管T1,第一晶体管T1包括电连接到第二节点N2的控制电极、第一电源电压ELVDD所施加到的第一电极以及电连接到第三节点N3的第二电极。例如,驱动晶体管可以是第一晶体管T1,因此,在本文中,第一晶体管T1也可以根据需要被称为驱动晶体管T1。

像素可以包括第二晶体管T2,第二晶体管T2包括数据写入栅极信号GW所施加到的控制电极、数据电压VDATA所施加到的第一电极以及电连接到第四节点N4的第二电极。例如,数据写入晶体管可以是第二晶体管T2。

根据本公开,像素可以包括第三晶体管T3,第三晶体管T3包括第二补偿栅极信号GC所施加到的控制电极、电连接到第五节点N5的第一电极以及电连接到第三节点N3的第二电极。

像素可以包括第四晶体管T4,第四晶体管T4包括数据初始化栅极信号GI所施加到的控制电极、数据初始化电压VINT所施加到的第一电极以及电连接到第五节点N5的第二电极。

像素可以包括第五晶体管T5,第五晶体管T5包括第二补偿栅极信号GC所施加到的控制电极、参考电压VREF所施加到的第一电极以及电连接到第四节点N4的第二电极。

像素可以包括第六晶体管T6,第六晶体管T6包括发射信号EM所施加到的控制电极、电连接到第三节点N3的第一电极以及电连接到发光元件EE的阳极电极的第二电极。

像素可以包括第七晶体管T7,第七晶体管T7包括发光元件初始化栅极信号GI(N+1)所施加到的控制电极、发光元件初始化电压VAINT所施加到的第一电极以及电连接到发光元件EE的阳极电极的第二电极。例如,发光元件初始化电压VAINT可以与数据初始化电压VINT相同。例如,发光元件初始化栅极信号GI(N+1)可以是下一帧的数据初始化栅极信号。例如,发光元件初始化栅极信号GI(N+1)可以与升压信号EB相同。

像素可以包括第八晶体管T8,第八晶体管T8包括第一补偿栅极信号GO所施加到的控制电极、电连接到第四节点N4的第一电极以及电连接到第一节点N1的第二电极。例如,第二氧化物薄膜晶体管OT2(参见图5)可以是第八晶体管T8。

像素可以包括第九晶体管T9,第九晶体管T9包括第一补偿栅极信号GO所施加到的控制电极、电连接到第二节点N2的第一电极以及电连接到第五节点N5的第二电极。例如,第一氧化物薄膜晶体管OT1(参见图4或图5)可以是第九晶体管T9。

在一些实施例中,第一电源电压ELVDD可以施加到保持电容器Chold的第一电极和第一晶体管T1的第一电极。第二电源电压ELVSS可以施加到发光元件EE的阴极电极。第一电源电压ELVDD可以是高电源电压,并且第二电源电压ELVSS可以是低电源电压。

由于像素包括第一氧化物薄膜晶体管OT1和第二氧化物薄膜晶体管OT2,因此可以使包括在像素中的氧化物薄膜晶体管的数量最小化。例如,第一晶体管T1至第七晶体管T7可以是多晶硅薄膜晶体管,并且第八晶体管T8和第九晶体管T9可以是氧化物薄膜晶体管。

参考图6至图9,支持可变频率的显示装置的操作时段可以包括数据电压VDATA被写入像素中的数据写入时段和数据电压VDATA不被写入像素中的自扫描时段。在自扫描时段中,可以在没有数据写入操作的情况下执行驱动晶体管的偏置操作。例如,第N帧(其中,N是正整数)可以包括数据电压VDATA被写入的数据写入时段和数据电压VDATA不被写入的自扫描时段。

图7至图9示出了数据写入时段和自扫描时段中的发射信号EM、第一补偿栅极信号GO、第二补偿栅极信号GC、数据写入栅极信号GW、数据初始化栅极信号GI、升压信号EB、第一晶体管T1的控制电极的电压VT1G、第一晶体管T1的第二电极的电压VT1D、第一节点N1的电压VN1和发光元件EE的阳极电极的电压VA的变化。

如图7中所示,在数据写入时段中,数据电压VDATA可以被写入像素中,并且可以执行像素的发射操作。在数据写入时段中,第一补偿栅极信号GO可以具有激活时段。在激活时段中,第一补偿栅极信号GO可以具有激活电平。在第一补偿栅极信号GO具有激活电平的情况下,第八晶体管T8和第九晶体管T9可以导通。在第一补偿栅极信号GO具有禁用(inactivation)电平的情况下,第八晶体管T8和第九晶体管T9可以截止。

在第一补偿栅极信号GO的激活时段中,数据写入栅极信号GW可以具有至少一个有效脉冲。在第一补偿栅极信号GO的激活时段中,第二补偿栅极信号GC可以具有至少一个有效脉冲。在第一补偿栅极信号GO的激活时段中,数据初始化栅极信号GI可以具有至少一个有效脉冲。如上所述,在像素包括根据第一补偿栅极信号GO控制的第八晶体管T8和第九晶体管T9的情况下,可以使包括在像素中的氧化物薄膜晶体管的数量最小化。因此,像素内部的电容器的电容可以增加,并且显示面板100(参见图1)的极限ppi可以增加。

如图8和图9中所示,在自扫描时段中,数据电压VDATA(参见图6)可以不被写入像素中,并且可以仅执行像素的发射操作。在自扫描时段中,第一补偿栅极信号GO可以具有禁用电平。在自扫描时段中,数据写入栅极信号GW可以具有禁用电平。在自扫描时段中,第二补偿栅极信号GC可以具有禁用电平。如图8中所示,在自扫描时段中,数据初始化栅极信号GI可以具有禁用电平。作为另一示例,如图9中所示,在自扫描时段中,数据初始化栅极信号GI可以具有至少一个有效脉冲。

数据写入时段和自扫描时段中的每一者可以包括偏置时段TBIAS。在偏置时段TBIAS中,数据写入栅极信号GW可以具有禁用电平。在偏置时段TBIAS中,第一补偿栅极信号GO可以具有禁用电平。在偏置时段TBIAS中,数据初始化栅极信号GI可以具有禁用电平。在偏置时段TBIAS中,升压信号EB可以具有激活电平。在偏置时段TBIAS中,发光元件EE的阳极电极的电压VA可以降低。

还参照图6,根据实施例,驱动晶体管T1可以响应于升压信号EB执行偏置操作。升压信号EB可以与发光元件初始化栅极信号GI(N+1)相同。

在升压信号EB下降到作为激活电平的低电平的情况下,升压信号EB所施加到的升压电容器CB的第二电极的电压可以降低。随着升压电容器的第二电极的电压降低,升压电容器CB的第一电极的电压也可以降低。

由于升压电容器CB的第一电极电连接到第一节点N1,因此第一节点N1的电压VN1可以降低。在第一节点N1的电压VN1降低的情况下,第一晶体管T1的控制电极的电压VT1G也可以通过电连接在第一节点N1与第一晶体管T1的控制电极(第二节点N2)之间的存储电容器Cst而降低。在图7中示出了第一晶体管T1的第二电极的电压VT1D的示例。

在驱动晶体管T1的第一电极的电压保持在第一电源电压ELVDD的值的同时,驱动晶体管T1的控制电极的电压VT1G可以降低,使得可以施加驱动晶体管T1的栅极-源极电压,并且可以通过驱动晶体管T1的栅极-源极电压执行驱动晶体管T1的偏置操作。

如上所述,根据本公开的实施例的支持可变频率的显示装置,可以使包括在像素中的氧化物薄膜晶体管的数量减少或最小化。因此,包括在像素中的晶体管之中的氧化物薄膜晶体管的比例可以降低,使得像素内部的电容器的电容可以增加,并且显示面板100的极限ppi可以增加。结果,支持可变频率的显示装置可以提高显示面板100的分辨率。

图10是示出图4的像素的示例的等效电路的示意图。

根据实施例,像素还可以包括升压电容器CB,升压电容器CB包括电连接到驱动晶体管的控制电极的第一电极和升压信号EB所施加到的第二电极。参考图10,像素可以包括第一晶体管T1,第一晶体管T1包括电连接到第二节点N2的控制电极、第一电源电压ELVDD所施加到的第一电极以及电连接到第三节点N3的第二电极。例如,驱动晶体管可以是第一晶体管T1。像素可以包括第二晶体管T2,第二晶体管T2包括数据写入栅极信号GW所施加到的控制电极、数据电压VDATA所施加到的第一电极以及电连接到第四节点N4的第二电极。例如,数据写入晶体管可以是第二晶体管T2。

根据本公开,像素可以包括第三晶体管T3,第三晶体管T3包括第二补偿栅极信号GC所施加到的控制电极、电连接到第五节点N5的第一电极以及电连接到第三节点N3的第二电极。像素可以包括第四晶体管T4,第四晶体管T4包括数据初始化栅极信号GI所施加到的控制电极、数据初始化电压VINT所施加到的第一电极以及电连接到第五节点N5的第二电极。像素可以包括第五晶体管T5,第五晶体管T5包括第二补偿栅极信号GC所施加到的控制电极、参考电压VREF所施加到的第一电极以及电连接到第四节点N4的第二电极。像素可以包括第六晶体管T6,第六晶体管T6包括发射信号EM所施加到的控制电极、电连接到第三节点N3的第一电极以及电连接到发光元件EE的阳极电极的第二电极。像素可以包括第七晶体管T7,第七晶体管T7包括发光元件初始化栅极信号GI(N+1)所施加到的控制电极、发光元件初始化电压VAINT所施加到的第一电极以及电连接到发光元件EE的阳极电极的第二电极。像素可以包括第八晶体管T8,第八晶体管T8包括第一补偿栅极信号GO所施加到的控制电极、电连接到第四节点N4的第一电极以及电连接到第一节点N1的第二电极。例如,第二氧化物薄膜晶体管OT2(参见图5)可以是第八晶体管T8。像素可以包括第九晶体管T9,第九晶体管T9包括第一补偿栅极信号GO所施加到的控制电极、电连接到第二节点N2的第一电极以及电连接到第五节点N5的第二电极。例如,第一氧化物薄膜晶体管OT1(参见图4或图5)可以是第九晶体管T9。

支持可变频率的显示装置的操作时段可以包括数据电压VDATA被写入像素中的数据写入时段和数据电压VDATA不被写入像素中的自扫描时段。在自扫描时段中,可以在没有数据写入操作的情况下执行驱动晶体管的偏置操作。例如,第N帧(其中,N是正整数)可以包括数据电压VDATA被写入的数据写入时段和数据电压VDATA不被写入的自扫描时段。

数据写入时段和自扫描时段中的每一者可以包括偏置时段TBIAS(参见图7至图9)。在偏置时段TBIAS中,数据写入栅极信号GW可以具有禁用电平。在偏置时段TBIAS中,第一补偿栅极信号GO可以具有禁用电平。在偏置时段TBIAS中,数据初始化栅极信号GI可以具有禁用电平。在偏置时段TBIAS中,升压信号EB可以具有激活电平。在偏置时段TBIAS中,发光元件EE的阳极电极的电压VA可以降低。

根据实施例,驱动晶体管T1可以响应于升压信号EB执行偏置操作。升压信号EB可以与发光元件初始化栅极信号GI(N+1)相同。在升压信号EB下降到作为激活电平的低电平的情况下,升压信号EB所施加到的升压电容器CB的第二电极的电压可以降低。随着升压电容器CB的第二电极的电压降低,第一晶体管T1的控制电极的电压VT1G(参见图7至图9)也可以降低。在驱动晶体管T1的第一电极的电压保持在第一电源电压ELVDD的值的同时,驱动晶体管T1的控制电极的电压VT1G可以降低,使得可以施加驱动晶体管T1的栅极-源极电压,并且可以通过驱动晶体管T1的栅极-源极电压执行驱动晶体管T1的偏置操作。

图11是示出根据本公开的实施例的像素的等效电路的示意图。

参考图11,根据本公开的实施例,像素可以包括发光元件EE、保持电容器Chold和存储电容器Cst,保持电容器Chold包括第一电源电压ELVDD所施加到的第一电极和电连接到第一节点N1的第二电极,存储电容器Cst包括电连接到第一节点N1的第一电极和电连接到第二节点N2的第二电极。

像素可以包括第一晶体管T1,第一晶体管T1包括电连接到第二节点N2的控制电极、电连接到第三节点N3的第一电极以及电连接到第四节点N4的第二电极。像素可以包括第二晶体管T2,第二晶体管T2包括数据写入栅极信号GW所施加到的控制电极、数据电压VDATA所施加到的第一电极以及电连接到第一节点N1的第二电极。像素可以包括第三晶体管T3,第三晶体管T3包括第二补偿栅极信号GC所施加到的控制电极、电连接到第二节点N2的第一电极以及电连接到第四节点N4的第二电极。像素可以包括第四晶体管T4,第四晶体管T4包括第二补偿栅极信号GC所施加到的控制电极、第一电源电压ELVDD所施加到的第一电极以及电连接到第一节点N1的第二电极。像素可以包括第五晶体管T5,第五晶体管T5包括第一发射信号EM1所施加到的控制电极、第一电源电压ELVDD所施加到的第一电极以及电连接到第三节点N3的第二电极。像素可以包括第六晶体管T6,第六晶体管T6包括第二发射信号EM2所施加到的控制电极、电连接到第四节点N4的第一电极以及电连接到发光元件EE的阳极电极的第二电极。像素可以包括第七晶体管T7,第七晶体管T7包括发光元件初始化栅极信号GI(N+1)所施加到的控制电极、发光元件初始化电压VAINT所施加到的第一电极以及电连接到发光元件EE的阳极电极的第二电极。

根据实施例,第一晶体管T1、第五晶体管T5、第六晶体管T6和第七晶体管T7可以是多晶硅薄膜晶体管,并且第二晶体管T2、第三晶体管T3和第四晶体管T4可以是氧化物薄膜晶体管。

图12是示出根据本公开的实施例的像素的等效电路的示意图。

参考图12,根据本公开的实施例,像素可以包括:发光元件EE;保持电容器Chold,包括第一电源电压ELVDD所施加到的第一电极和电连接到第一节点N1的第二电极;以及存储电容器Cst,包括电连接到第一节点N1的第一电极和电连接到第二节点N2的第二电极。

像素可以包括第一晶体管T1,第一晶体管T1包括电连接到第二节点N2的控制电极、电连接到第三节点N3的第一电极以及电连接到第四节点N4的第二电极。像素可以包括第二晶体管T2,第二晶体管T2包括数据写入栅极信号GW所施加到的控制电极、数据电压VDATA所施加到的第一电极以及电连接到第一节点N1的第二电极。像素可以包括第三晶体管T3,第三晶体管T3包括第二补偿栅极信号GC所施加到的控制电极、电连接到第二节点N2的第一电极以及电连接到第四节点N4的第二电极。像素可以包括第四晶体管T4,第四晶体管T4包括第二补偿栅极信号GC所施加到的控制电极、第一电源电压ELVDD所施加到的第一电极以及电连接到第一节点N1的第二电极。像素可以包括第五晶体管T5,第五晶体管T5包括第一发射信号EM1所施加到的控制电极、第一电源电压ELVDD所施加到的第一电极以及电连接到第三节点N3的第二电极。像素可以包括第六晶体管T6,第六晶体管T6包括第二发射信号EM2所施加到的控制电极、电连接到第四节点N4的第一电极以及电连接到发光元件EE的阳极电极的第二电极。像素可以包括第七晶体管T7,第七晶体管T7包括发光元件初始化栅极信号GI(N+1)所施加到的控制电极、发光元件初始化电压VAINT所施加到的第一电极以及电连接到发光元件EE的阳极电极的第二电极。像素可以包括第八晶体管T8,第八晶体管T8包括发光元件初始化栅极信号GI(N+1)所施加到的控制电极、偏置电压Vbias所施加到的第一电极以及电连接到第三节点N3的第二电极。

根据实施例,第一晶体管T1、第五晶体管T5、第六晶体管T6、第七晶体管T7和第八晶体管T8可以是多晶硅薄膜晶体管,并且第二晶体管T2、第三晶体管T3和第四晶体管T4可以是氧化物薄膜晶体管。

图13是示出图12的像素的示意性布局图。

参考图12和图13,根据本公开的实施例,像素可以包括第一有源层(或第一有源图案)PACT、第一导电层110、第二导电层120、第二有源层(或第二有源图案)OACT、第三导电层130、第四导电层140以及第五导电层150。

第一有源层PACT可以包括多晶硅。第一晶体管T1、第五晶体管T5、第六晶体管T6、第七晶体管T7和第八晶体管T8可以沿着第一有源层PACT形成。

第一导电层110可以设置在第一有源层PACT上。第一导电层110可以包括诸如铜(Cu)、钼(Mo)、铝(Al)和/或钛(Ti)的金属。第一导电层110可以包括第一栅极图案111、第一发射线112、第二发射线113、第一发光元件初始化栅极线114和第八栅极图案115。

第一栅极图案111可以包括第一晶体管T1的控制电极和存储电容器Cst的第二电极。第一发射线112可以传输第一发射信号EM1。第二发射线113可以传输第二发射信号EM2。第一发光元件初始化栅极线114可以传输发光元件初始化栅极信号GI(N+1)。第八栅极图案115可以包括第八晶体管T8的控制电极。

第二导电层120可以设置在第一导电层110上。第二导电层120可以包括诸如铜(Cu)、钼(Mo)、铝(Al)和/或钛(Ti)的金属。第二导电层120可以包括存储电容器Cst的第一电极和保持电容器Chold的第二电极。

第二有源层OACT可以设置在第二导电层120上。第二有源层OACT可以包括氧化物半导体。第二晶体管T2、第三晶体管T3和第四晶体管T4可以沿着第二有源层OACT形成。

第三导电层130可以设置在第二有源层OACT上。第三导电层130可以包括诸如铜(Cu)、钼(Mo)、铝(Al)和/或钛(Ti)的金属。第三导电层130可以包括电容器图案131、第二栅极图案132和补偿栅极线133。

电容器图案131可以包括保持电容器Chold的第一电极。第二栅极图案132可以包括第二晶体管T2的控制电极。补偿栅极线133可以传输第二补偿栅极信号GC。

第四导电层140可以设置在第三导电层130上。第四导电层140可以包括诸如铜(Cu)、钼(Mo)、铝(Al)和/或钛(Ti)的金属。第四导电层140可以包括数据写入栅极线141、数据连接图案142、第一有源连接图案143、第二有源连接图案144、第三有源连接图案145、第四有源连接图案146、第一电源电压连接图案147、第二电源电压连接图案148、第一发光元件连接图案149、发光元件初始化电压线140a、第一发光元件初始化栅极线140b、第二发射连接线140c和第三电源电压连接图案140d。

数据写入栅极线141可以传输数据写入栅极信号GW。数据连接图案142可以将第二有源图案OACT电连接到数据线151。第一有源连接图案143可以将第一有源图案PACT电连接到第二有源图案OACT。第二有源连接图案144可以将第二有源图案OACT的彼此间隔开的部分彼此电连接。第三有源连接图案145可以将第一栅极图案111电连接到第二有源图案OACT。第四有源连接图案146可以将第二导电层120电连接到第二有源图案OACT。第一电源电压连接图案147可以将第二有源图案OACT电连接到电源电压线152。第二电源电压连接图案148可以将第一有源图案PACT电连接到电容器图案131。第一发光元件连接图案149可以将第一有源图案PACT电连接到第二发光元件连接图案153。发光元件初始化电压线140a可以传输发光元件初始化电压VAINT。第一发光元件初始化栅极线140b可以传输发光元件初始化栅极信号GI(N+1)。第二发射连接线140c可以将第一有源图案PACT电连接到第二发射线113。例如,偏置电压Vbias可以是第二发射信号EM2的高电压。第三电源电压连接图案140d可以将电容器图案131电连接到电源电压线152。

第五导电层150可以设置在第四导电层140上。第五导电层150可以包括诸如铜(Cu)、钼(Mo)、铝(Al)和/或钛(Ti)的金属。第五导电层150可以包括数据线151、电源电压线152和第二发光元件连接图案153。

数据线151可以传输数据电压VDATA。电源电压线152可以传输第一电源电压ELVDD。第二发光元件连接图案153可以将第一发光元件连接图案149电连接到发光元件EE的阳极电极。

图14是示出根据本公开的实施例的像素的等效电路的示意图。

参考图14,根据本公开的实施例,像素可以包括发光元件EE、保持电容器Chold和存储电容器Cst,保持电容器Chold包括第一电源电压ELVDD所施加到的第一电极和电连接到第一节点N1的第二电极,存储电容器Cst包括电连接到第一节点N1的第一电极和电连接到第二节点N2的第二电极。

像素可以包括第一晶体管T1,第一晶体管T1包括电连接到第二节点N2的控制电极、电连接到第三节点N3的第一电极以及电连接到第五节点N5的第二电极。像素可以包括第二晶体管T2,第二晶体管T2包括数据写入栅极信号GW所施加到的控制电极、数据电压VDATA所施加到的第一电极以及电连接到第四节点N4的第二电极。像素可以包括第三晶体管T3,第三晶体管T3包括第二补偿栅极信号GC所施加到的控制电极、电连接到第二节点N2的第一电极以及电连接到第五节点N5的第二电极。像素可以包括第四晶体管T4,第四晶体管T4包括第二补偿栅极信号GC所施加到的控制电极、第一电源电压ELVDD所施加到的第一电极以及电连接到第四节点N4的第二电极。像素可以包括第五晶体管T5,第五晶体管T5包括第一发射信号EM1所施加到的控制电极、第一电源电压ELVDD所施加到的第一电极以及电连接到第三节点N3的第二电极。像素可以包括第六晶体管T6,第六晶体管T6包括第二发射信号EM2所施加到的控制电极、电连接到第五节点N5的第一电极以及电连接到发光元件EE的阳极电极的第二电极。像素可以包括第七晶体管T7,第七晶体管T7包括发光元件初始化栅极信号GI(N+1)所施加到的控制电极、发光元件初始化电压VAINT所施加到的第一电极以及电连接到发光元件EE的阳极电极的第二电极。像素可以包括第八晶体管T8,第八晶体管T8包括第一补偿栅极信号GO所施加到的控制电极、电连接到第一节点N1的第一电极以及电连接到第四节点N4的第二电极。

根据实施例,第一晶体管T1、第二晶体管T2、第四晶体管T4、第五晶体管T5、第六晶体管T6和第七晶体管T7可以是多晶硅薄膜晶体管,并且第三晶体管T3和第八晶体管T8可以是氧化物薄膜晶体管。

图15是示出根据本公开的实施例的电子装置1000的示意性框图,并且图16是示出图15的电子装置1000被实现为智能电话的示例的示意图。

参考图15和图16,电子装置1000可以包括处理器1010、存储器装置1020、存储装置1030、输入/输出(I/O)装置1040、电源1050和显示装置1060。在这种情况下,显示装置1060可以是图1的显示装置。此外,电子装置1000还可以包括能够与视频卡、声卡、存储卡或通用串行总线(USB)装置等进行通信或与其它系统进行通信的各种端口。根据实施例,如图16中所示,电子装置1000可以被实现为智能电话。然而,已经出于说明性的目的提供了实施方式,并且电子装置1000不限于此。例如,电子装置1000可以被实现为移动电话、视频电话、智能平板、智能手表、平板个人计算机(PC)、(车辆)导航系统、计算机监视器、膝上型计算机或头戴式显示装置等。

处理器1010可以执行特定的计算或任务。根据实施例,处理器1010可以是微处理器、中央处理单元(CPU)或应用处理器等。处理器1010可以通过地址总线、控制总线和数据总线等电连接到其它组件。根据实施例,处理器1010还可以电连接到诸如外围组件互连(PCI)总线的扩展总线。存储器装置1020可以存储电子装置1000的操作所需的数据。存储器装置1020的示例可以包括诸如可擦除可编程只读存储器(EPROM)装置、电可擦除可编程只读存储器(EEPROM)装置、闪存装置、相变随机存取存储器(PRAM)装置、电阻随机存取存储器(RRAM)装置、纳米浮栅存储器(NFGM)装置、聚合物随机存取存储器(PoRAM)装置、磁随机存取存储器(MRAM)装置和铁电随机存取存储器(FRAM)装置的非易失性存储器装置以及/或者诸如动态随机存取存储器(DRAM)装置、静态随机存取存储器(SRAM)装置和移动DRAM装置的易失性存储器装置。存储装置1030的示例可以包括固态驱动器(SSD)、硬盘驱动器(HDD)和光盘只读存储器(CD-ROM)等。I/O装置1040可以包括诸如键盘、小键盘、触摸板、触摸屏和鼠标的输入装置以及诸如扬声器和打印机的输出装置。在一些实施例中,显示装置1060可以被包括在I/O装置1040中。电源1050可以供应电子装置1000的操作所需的电力。显示装置1060可以通过总线或其它通信链路电连接到其它组件。

显示装置1060可以显示对应于电子装置1000的视觉信息的图像。在这种情况下,显示装置1060可以包括:显示面板,包括像素;栅极驱动器,配置为将栅极信号提供到像素;数据驱动器,配置为将数据电压提供到像素;以及发射驱动器,配置为将发射信号提供到像素。像素可以包括:发光元件;数据写入晶体管,配置为写入数据电压;驱动晶体管,配置为基于数据电压将驱动电流施加到发光元件;保持电容器,包括第一电源电压所施加到的第一电极和电连接到第一节点的第二电极;存储电容器,包括电连接到第一节点的第一电极和电连接到驱动晶体管的控制电极的第二电极;至少一个多晶硅薄膜晶体管;以及至少一个氧化物薄膜晶体管。至少一个氧化物薄膜晶体管可以设置在至少一个多晶硅薄膜晶体管与保持电容器之间或者设置在至少一个多晶硅薄膜晶体管与存储电容器之间。因此,根据本公开的支持可变频率的显示装置,可以使包括在像素中的氧化物薄膜晶体管的数量减少或最小化。因此,包括在像素中的晶体管之中的氧化物薄膜晶体管的比例可以降低,使得像素内部的电容器的电容可以增加,并且显示面板的极限ppi可以增加。结果,根据支持可变频率的显示装置,可以提高显示面板的分辨率。然而,由于上面已经描述了配置,因此将省略对其的重复描述。

本公开可以应用于显示装置和包括显示装置的电子设备。例如,本公开可以应用于移动电话、智能电话、视频电话、智能平板、智能手表、平板PC、汽车导航系统、电视机、计算机监视器、笔记本计算机、数字相机或头戴式显示器等。

以上描述是本公开的技术特征的示例,并且本公开所属领域的中的技术人员将能够进行各种修改和改变。因此,上述本公开的实施例可以单独实现或者可以彼此组合实现。

因此,本公开中公开的实施例不旨在限制本公开的技术精神,而是旨在描述本公开的技术精神,并且本公开的技术精神的范围不受这些实施例的限制。本公开的保护范围应当由所附权利要求来解释,并且应当理解的是,等同范围内的所有技术精神包括在本公开的范围内。

- 显示装置、制造该显示装置的方法和像素

- 一种像素驱动电路、显示装置及像素驱动电路的驱动方法

- 像素电路、像素驱动方法和显示装置

- 像素电路、显示面板、显示装置和像素驱动方法

- 像素结构、阵列基板及显示装置

- 像素、具有该像素的显示装置及该显示装置的制造方法

- 像素、包括像素的显示装置及制造显示装置的方法