功率半导体装置

文献发布时间:2023-06-19 09:24:30

技术领域

本发明涉及一种半导体装置,特别是涉及一种功率半导体装置。

背景技术

半导体与半导体相关产业已经发展成一个精练成熟、高度富有发明性且高效率产出的产业,许多前端的制程与设备加上光学微影的搭配,已经成功地被用来制造电子元件与集成电路。然而,热却成了不可避免的议题,它会通过欧姆热的生成,以造成电性的损伤,诸如在元件或追寻低成本通讯集成电路(IC)在速率上的要求,或是功率元件,都可以见到此种现象。一般热基本上是由于碰撞所造成的磨擦所产生,故随处可见。不幸地,它是能源消耗的主要元凶,却又受制于低于40%左右可回收的效率。与其将所产出的热导出,还不如致力于降低产生热的几率。电热的产生是由导电的电流载体与导电材质内部晶格的碰撞而产生的摩擦所造成。

图1为现有技术的功率半导体装置的结构俯视图,图2为图1沿A-A’线的结构剖视图,请参阅图1与图2。在现有技术中,功率半导体装置1包含一N型基板10、一P型井区12、一N型重掺杂区14、一绝缘层16与一闸极层18。P型井区12设于N型基板10中,并围绕N型基板10的一N型区域19,N型重掺杂区14设于P型井区12中,并同样围绕N型区域19。绝缘层16设于P型井区12、N型重掺杂区14与N型区域19上,且闸极层18设于绝缘层16上。当N型基板10施加正电压,且N型重掺杂区14接地时,电流从N型基板10依序经过N型区域19与P型井区12往N型重掺杂区14流动。假设P型井区12的外围呈边长为14微米的正方形,闸极层18呈边长为10微米的正方形,N型区域19呈边长为2微米的正方形。由于闸极层18的外周长与N型区域19的截面积两者与热产生机率呈正相关,假设功率半导体装置1的截面积视为14微米×14微米,闸极层18的外周长为10×4微米,N型区域19的截面积为2

因此,本发明针对上述的困扰,提出一种功率半导体装置,以解决上述所产生的技术问题。

发明内容

本发明提供一种功率半导体装置,可以降低热能产生的机率。

本发明提供一种功率半导体装置,其包含N型半导体层、P型井区、N型重掺杂区、绝缘层与闸极层。P型井区设于N型半导体层中,其中P型井区围绕N型半导体层的C字形N型区域。N型重掺杂区设于P型井区中,N型重掺杂区围绕C字形N型区域。绝缘层设于N型半导体层上,并覆盖部分的P型井区、部分的N型重掺杂区与全部C字形N型区域。闸极层设于绝缘层上,闸极层的形状与C字形N型区域相同。

可选地,N型半导体层为N型轻掺杂基板。

可选地,功率半导体装置还包含重掺杂半导体层,设于N型半导体层的底部。

可选地,P型井区的外侧壁与N型重掺杂区的外侧壁相隔。

可选地,闸极层与C字形N型区域的每一者具有互相连通的第一凹入部与第二凹入部,第一凹入部的宽度不同于第二凹入部的宽度。

可选地,第一凹入部具有固定宽度,第二凹入部具有渐变宽度。

可选地,闸极层的外周长包含至少两条直线,所有直线为等长。

可选地,每一条直线为30微米。

可选地,闸极层具有凹入部,凹入部具有固定宽度或渐变宽度。

可选地,绝缘层的形状与闸极层的形状相同。

可选地,P型井区的外周长为136微米。

可选地,功率半导体装置更包含P型重掺杂区与P型重掺杂半导体层。P型重掺杂区设于P型井区中,并围绕N型重掺杂区,P型重掺杂半导体层设于N型半导体层的底部。

可选地,N型半导体层为N型基板。

可选地,N型半导体层更包含半导体基板与N型磊晶层,N型磊晶层设于半导体基板上,N型磊晶层具有C字形N型区域,P型井区设于N型磊晶层中,绝缘层设于N型磊晶层上。

基于上述,功率半导体装置通过增加电流通过的截面积与闸极层的周长,以降低热能产生机率。

为使贵审查委员对本发明的结构特征及所达成的功效更有进一步的了解与认识,谨佐以较佳的实施例图及配合详细的说明,说明如后:

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

图1为现有技术的功率半导体装置的结构俯视图;

图2为图1沿A-A’线的结构剖视图;

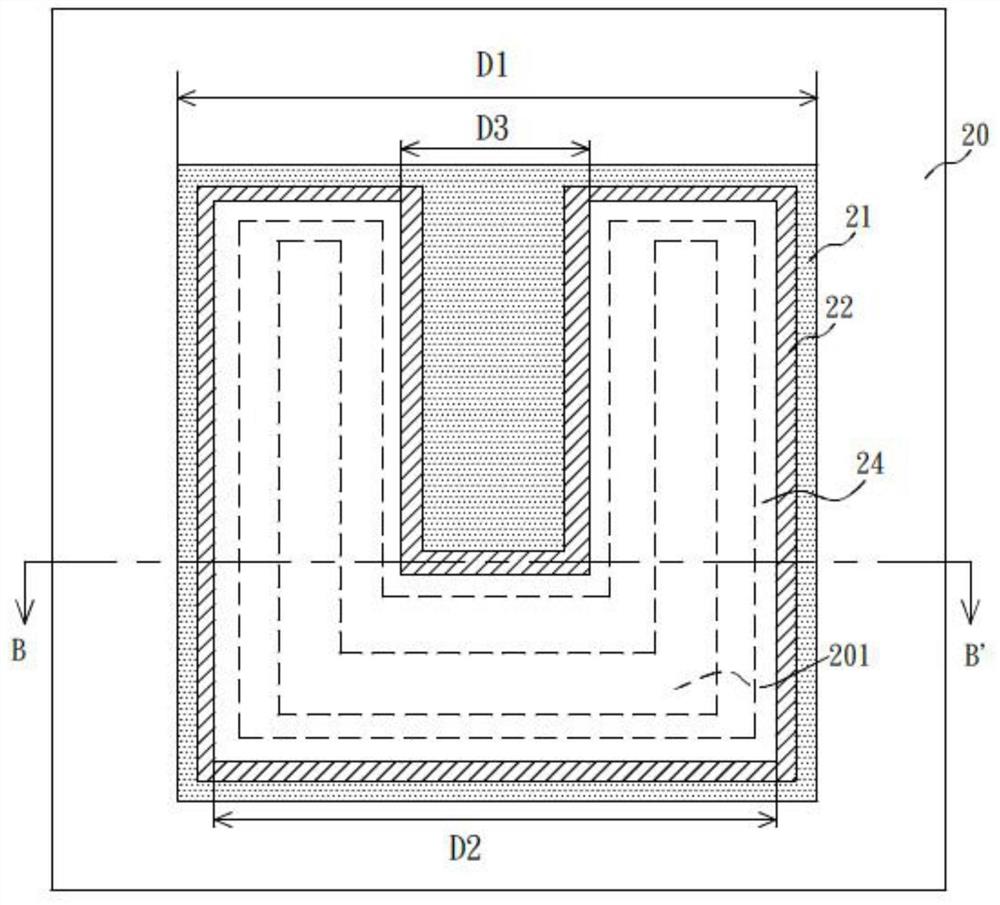

图3为本发明的功率半导体装置的第一实施例的结构俯视图;

图4为图3沿B-B’线的一结构剖视图;

图5为图3沿B-B’线的另一结构剖视图;

图6为本发明的功率半导体装置的第二实施例的结构剖视图;

图7为图6沿C-C’线的一结构剖视图;

图8为图6沿C-C’线的另一结构剖视图;

图9为本发明的功率半导体装置的第三实施例的结构剖视图;

图10为图9沿D-D’线的一结构剖视图;

图11为图9沿D-D’线的另一结构剖视图;

图12为本发明的功率半导体装置的第四实施例的结构俯视图;

图13为图12沿E-E’线的一结构剖视图;

图14为图12沿E-E’线的另一结构剖视图;

图15为本发明的功率半导体装置的第五实施例的结构剖视图;

图16为图15沿F-F’线的一结构剖视图;

图17为图15沿F-F’线的另一结构剖视图;

图18为本发明的功率半导体装置的第六实施例的结构剖视图;

图19为图18沿G-G’线的一结构剖视图;

图20为图18沿G-G’线的另一结构剖视图。

符号说明

1…功率半导体装置,10…N型基板,12…P型井区,14…N型重掺杂区,16…绝缘层,18…闸极层,19…N型区域,

2…功率半导体装置,20…N型半导体层,201…C字形N型区域,202…半导体基板,203..N型磊晶层,21…P型井区,22…N型重掺杂区,23…绝缘层,24…闸极层,25…重掺杂半导体层,26…P型重掺杂区,27…P型重掺杂半导体层,

D1…边长,D2…边长,D3…宽度,D4…宽度,D5…宽度,D6…宽度。

具体实施方式

本发明的实施例将由下文配合相关附图进一步加以解说。尽可能的,在附图与说明书中,相同标号是代表相同或相似构件。在附图中,基于简化与方便标示,形状与厚度可能经过夸大表示。可以理解的是,未特别显示在附图中或描述在说明书中的元件,为所属技术领域中具有通常技术者所知的形态。本领域的通常技术者可依据本发明的内容而进行多种改变与修改。

除非另有说明,否则某些条件句子或单词,例如“可以”,“可能”,“可能”或“可能”,通常试图表示本发明中的实施例具有的含义,但也可以解释为可能不需要的功能,元素或步骤。在其他实施例中,可能不需要这些特征,元素或步骤。

在下文中关于“一个实施例”或“一实施例”的描述是指关于至少一实施例内所相关连的一特定元件、结构或特征。因此,在下文中多处所出现的“一个实施例”或“一实施例”的多个描述并非针对同一实施例。再者,于一或多个实施例中的特定构件、结构与特征可依照一适当方式而结合。

在整个说明书和申请专利范围中使用某些术语来指代特定部件。本领域的技术人员意识到,组件可以被称为不同的名称。本公开内容不旨在区分名称不同但功能相同的组件。在说明书和申请专利范围中,术语“包括”以开放式方式使用,因此应解释为表示“包括但不限于”。短语“被耦合到”、“耦合到”和“正耦合到”旨在包括任何间接或直接连接。因此,如果本揭露提到第一设备与第二设备耦合,则意味着第一设备可以通过电连接、无线通信、光通信或其他信号连接在有/无直接或间接地利用其他中间设备或连接方式连接到第二设备。

为加大传导电流或减少电阻以增进元件或集成电路(IC)的电性,增加电流载体(carrier)行经路程的截面积也是重要一环,因此若能在制作功率元件,特别是垂直式晶体管,例如双扩散金属氧化物半导体场效晶体管(VMOSFET),其是将电流载体从晶体管底部垂直往上至晶体管顶部时,有效地增加单位硅芯片面积内截面积的总数,就可同时降低电阻而减少欧姆热产生,即可使得所设计或制造的元件或IC免于热光子或热声子的干扰,甚至能维持元件好的电性。

图3为本发明的功率半导体装置的第一实施例的结构俯视图,图4为图3沿B-B’线的一结构剖视图。请参阅图3与图4,并介绍本发明的功率半导体装置的第一实施例。功率半导体装置2包含N型半导体层20、P型井区21、N型重掺杂区22、绝缘层23与闸极层24,其中N型半导体层20可为N型轻掺杂基板或一般N型基板。P型井区21设于N型半导体层20中,P型井区21围绕N型半导体层20的C字形N型区域201。N型重掺杂区22设于P型井区21中,N型重掺杂区22围绕C字形N型区域201。P型井区21的外侧壁不但可与N型重掺杂区22的外侧壁相隔,也可与N型重掺杂区22的外侧壁接触。绝缘层23设于N型半导体层20上,并覆盖部分P型井区21、部分N型重掺杂区22与全部C字形N型区域201。闸极层24设于绝缘层23上,使闸极层24也覆盖部分的P型井区21、部分的N型重掺杂区22与全部的C字形N型区域201,使绝缘层23的形状与闸极层24的形状相同,闸极层24的外周长与N型重掺杂区22重叠,因此,闸极层24的形状与C字形N型区域201的形状相同,即闸极层24为C字形。举例来说,闸极层24的外周长包含至少两条直线,此至少两条直线为等长,如都为30微米,但本发明不限于此。此外,闸极层24具有凹入部,此凹入部具有固定宽度或渐变宽度,但本发明不限于此。为了形成欧姆接触,功率半导体装置2还包含N型或P型的重掺杂半导体层25,设于N型半导体层20的底部。

当重掺杂半导体层25施加正电压,且N型重掺杂区22接地时,电流从重掺杂半导体层25依序经过N型半导体层20、C字形N型区域201与P型井区21流往N型重掺杂区22。假设P型井区21的外围呈边长D1为34微米的正方形,其周长为136微米。闸极层24具有三个互相垂直的等长边长D2,其为30微米。闸极层24的凹入部的固定宽度D3为10微米。C字形N型区域201的侧壁与闸极层24的侧壁相距的最近水平距离为8微米。为了增加电流通过的截面积,故闸极层24的外周长与C字形N型区域201的截面积两者与热产生机率呈正相关,假设功率半导体装置2的截面积视为34微米×34微米,闸极层24的外周长为(10×5+30×3+20)微米,C字形N型区域201的截面积为(2

图5为图3沿B-B’线的另一结构剖视图。图5与图4差别在于N型半导体层20包含半导体基板202与N型磊晶层203,半导体基板202可为N型半导体基板或P型半导体基板,N型磊晶层203设于半导体基板202上,N型磊晶层203具有C字形N型区域201,P型井区21设于N型磊晶层203中,绝缘层23设于N型磊晶层203上,重掺杂半导体层25设于半导体基板202的底部。

图6为本发明的功率半导体装置的第二实施例的结构剖视图,图7为图6沿C-C’线的一结构剖视图。请参阅图6与图7,并介绍本发明的功率半导体装置的第二实施例。相较第一实施例,第二实施例的功率半导体装置2的闸极层24、绝缘层23与每一C字形N型区域201都具有互相连通的第一凹入部与第二凹入部,第一凹入部的宽度不同于第二凹入部的宽度,以此增加电流通过的截面积。

当重掺杂半导体层25施加正电压,且N型重掺杂区22接地时,电流从重掺杂半导体层25依序经过N型半导体层20、C字形N型区域201与P型井区21流往N型重掺杂区22。假设P型井区21的外围呈边长D1为34微米的正方形,其周长为136微米。闸极层24具有三个互相垂直的等长边长D2,D2为30微米。闸极层24的第一凹入部具有的固定宽度D3为10微米,第二凹入部具有的固定宽度D4远小于宽度D3。将C字形N型区域201位于闸极层24的中央位置,且C字形N型区域201为2微米。假设功率半导体装置2的截面积视为34微米×34微米,闸极层24的外周长为(10×4+30×4)微米,C字形N型区域201的截面积为(2

图8为图6沿C-C’线的另一结构剖视图。图8与图7差别在于N型半导体层20包含半导体基板202与N型磊晶层203,半导体基板202可为N型半导体基板或P型半导体基板,N型磊晶层203设于半导体基板202上,N型磊晶层203具有C字形N型区域201,P型井区21设于N型磊晶层203中,绝缘层23设于N型磊晶层203上,重掺杂半导体层25设于半导体基板202的底部。

图9为本发明的功率半导体装置的第三实施例的结构剖视图,图10为图9沿D-D’线的一结构剖视图。请参阅图9与图10,并介绍本发明的功率半导体装置的第三实施例。相较第一实施例,第三实施例的功率半导体装置2的闸极层24、绝缘层23与C字形N型区域201的每一者具有互相连通的第一凹入部与第二凹入部,第一凹入部的宽度不同于第二凹入部的宽度,以此来增加电流通过的截面积。在第三实施例中,闸极层24的第一凹入部具有固定宽度D5,闸极层24的第二凹入部具有渐变宽度D6。由于闸极层24的外周长与C字形N型区域201的截面积相较图1也增加了,所以也能降低热能产生机率。

图11为图9沿D-D’线的另一结构剖视图。图11与图10差别在于N型半导体层20包含半导体基板202与N型磊晶层203,半导体基板202可为N型半导体基板或P型半导体基板,N型磊晶层203设于半导体基板202上,N型磊晶层203具有C字形N型区域201,P型井区21设于N型磊晶层203中,绝缘层23设于N型磊晶层203上,重掺杂半导体层25设于半导体基板202的底部。

图12为本发明的功率半导体装置的第四实施例的结构俯视图。图13为图12沿E-E’线的一结构剖视图。请参阅图4、图12与图13,并介绍本发明的功率半导体装置的第四实施例。相较第一实施例,第四实施例的功率半导体装置2更包含P型重掺杂区26,且以P型重掺杂半导体层27取代第一实施例的重掺杂半导体层25。P型重掺杂区26设于P型井区21中,并围绕N型重掺杂区26。P型井区21的外侧壁不但可与P型重掺杂区26的外侧壁相隔,也可与P型重掺杂区26的外侧壁接触。P型重掺杂半导体层27设于N型半导体层20的底部。P型重掺杂区26、P型井区21、N型半导体层20与P型重掺杂半导体层27形成PNP双极性接面晶体管。当P型重掺杂半导体层27施加正电压,且P型重掺杂区26与N型重掺杂区22接地时,电流从重掺杂半导体层25依序经过N型半导体层20、C字形N型区域201与P型井区21流往N型重掺杂区22,同时电流也从P型重掺杂半导体层27依序通过N型半导体层20与P型井区21流向P型重掺杂区26,以增加功率半导体装置2的电流驱动能力。

图14为图12沿E-E’线的另一结构剖视图。图14与图13差别在于N型半导体层20包含半导体基板202与N型磊晶层203,半导体基板202可为N型半导体基板或P型半导体基板,N型磊晶层203设于半导体基板202上,N型磊晶层203具有C字形N型区域201,P型井区21设于N型磊晶层203中,绝缘层23设于N型磊晶层203上,重掺杂半导体层25设于半导体基板202的底部。

图15为本发明的功率半导体装置的第五实施例的结构剖视图。图16为图15沿F-F’线的一结构剖视图。请参阅图7、图15与图16,并介绍本发明的功率半导体装置的第五实施例。相较第二实施例,第五实施例的功率半导体装置2更包含P型重掺杂区26,且以P型重掺杂半导体层27取代第二实施例的重掺杂半导体层25。P型重掺杂区26设于P型井区21中,并围绕N型重掺杂区26。P型井区21的外侧壁不但可与P型重掺杂区26的外侧壁相隔,也可与P型重掺杂区26的外侧壁接触。P型重掺杂半导体层27设于N型半导体层20的底部。P型重掺杂区26、P型井区21、N型半导体层20与P型重掺杂半导体层27形成PNP双极性接面晶体管。当P型重掺杂半导体层27施加正电压,且P型重掺杂区26与N型重掺杂区22接地时,电流从重掺杂半导体层25依序经过N型半导体层20、C字形N型区域201与P型井区21流往N型重掺杂区22,同时电流也从P型重掺杂半导体层27依序通过N型半导体层20与P型井区21流向P型重掺杂区26,以增加功率半导体装置2的电流驱动能力。

图17为图15沿F-F’线的另一结构剖视图。图17与图16差别在于N型半导体层20包含半导体基板202与N型磊晶层203,半导体基板202可为N型半导体基板或P型半导体基板,N型磊晶层203设于半导体基板202上,N型磊晶层203具有C字形N型区域201,P型井区21设于N型磊晶层203中,绝缘层23设于N型磊晶层203上,重掺杂半导体层25设于半导体基板202的底部。

图18为本发明的功率半导体装置的第六实施例的结构剖视图。图19为图18沿G-G’线的结构剖视图。请参阅图10、图18与图19,并介绍本发明的功率半导体装置的第六实施例。相较第三实施例,第六实施例的功率半导体装置2更包含P型重掺杂区26,且以P型重掺杂半导体层27取代第三实施例的重掺杂半导体层25。P型重掺杂区26设于P型井区21中,并围绕N型重掺杂区26。P型井区21的外侧壁不但可与P型重掺杂区26的外侧壁相隔,也可与P型重掺杂区26的外侧壁接触。P型重掺杂半导体层27设于N型半导体层20的底部。P型重掺杂区26、P型井区21、N型半导体层20与P型重掺杂半导体层27形成PNP双极性接面晶体管。当P型重掺杂半导体层27施加正电压,且P型重掺杂区26与N型重掺杂区22接地时,电流从重掺杂半导体层25依序经过N型半导体层20、C字形N型区域201与P型井区21流往N型重掺杂区22,同时电流也从P型重掺杂半导体层27依序通过N型半导体层20与P型井区21流向P型重掺杂区26,以增加功率半导体装置2的电流驱动能力。

图20为图18沿G-G’线的另一结构剖视图。图20与图19差别在于N型半导体层20包含半导体基板202与N型磊晶层203,半导体基板202可为N型半导体基板或P型半导体基板,N型磊晶层203设于半导体基板202上,N型磊晶层203具有C字形N型区域201,P型井区21设于N型磊晶层203中,绝缘层23设于N型磊晶层203上,重掺杂半导体层25设于半导体基板202的底部。

根据上述实施例,功率半导体装置通过增加电流通过的截面积与闸极层的周长,以降低热能产生机率。

以上所述,仅为本发明一较佳实施例而已,并非用来限定本发明实施的范围,故举凡依本发明申请专利范围所述的形状、构造、特征及精神所为的均等变化与修饰,均应包括于本发明的申请专利范围内。

- 用于具有壳体的功率半导体装置的连接装置及功率半导体装置

- 功率半导体装置、功率半导体装置的制造方法以及马达驱动装置