一种硅控整流器及其制造方法

文献发布时间:2023-06-19 10:14:56

技术领域

本发明涉及集成电路生产制造领域,特别是涉及一种无回滞效应硅控整流器。本发明还涉及一种无回滞效应硅控整流器的制造方法。

背景技术

高压电路的防静电保护设计一直是一个技术难题,这是因为构成高压电路的核心:高压器件(例如LDMOS)本身不像普通的低压器件适用于防静电保护设计,因为高压器件的回滞效应曲线所表现出来的特性很差。如图1所示,从常规高压器件回滞效应曲线可以得出以下缺陷:

1)维持电压(Vh)过低,往往大大低于高压电路的工作电压,高压电路正常工作时容易导致闩锁效应;

2)二次击穿电流(热击穿电流,It2)过低,这是因为LDMOS在泄放ESD电流时因为器件结构特性发生局部电流拥堵(Localized Current Crowding)所致。

因而工业界在解决高压电路防静电保护设计的时候,往往采用两种思路来实现:

1)对用于防静电保护模块的高压器件结构进行调整,优化其回滞效应曲线,使之适用于防静电保护设计,但往往因为高压器件本身的结构特性的原因实践起来比较困难;

2)用一定数量的低压防静电保护器件串联起来构成能承受高压的防静电保护电路。因为低压防静电保护器件的特性相对容易调整和控制,所以工业界特别是集成电路设计公司往往比较喜欢用一定数量的低压防静电保护器件串联的方法。

因为高压电路防静电保护设计窗口的需要,这就对低压防静电保护器件的回滞效应特性有一定的要求,往往要求其回滞效应窗口越小越好,最好没有回滞效应,也就是回滞效应的维持电压和触发电压基本保持一致。低压PMOS器件是一种常见的无回滞效应静电防护器件,因为其发生回滞效应时的寄生PNP三极管电流增益比较小,但低压PMOS器件的不足之处是其回滞效应的二次击穿电流(It2)比较小,所以工业界纷纷研究开发一种既没有回滞效应又具有较高的二次击穿电流的防静电保护器件。

工业界于2015年提出新型的无回滞效应硅控整流器(No-Snapback SCR),如图2所示,该新型无回滞效应硅控整流器的实验数据表明,当N+(28)和P+(22)的尺寸(D2)达到一定程度(4um)时,该新型硅控整流器表现出无回滞效应的特性,如图3所示,非常适合低压器件多级串联用于高压电路防静电保护设计的需要。但该新型无回滞效应硅控整流器的缺点是器件尺寸比较大,特别是在需要多级串联的时候,版图面积比较大。

中国专利号:CN108183101B公开了一种新型硅控整流器,如图4所示,其将原先浮接的N+28与阳极直接相连,这使得N+28降低空穴从P+20注入到N阱(N_Well60)并达到N阱/P阱界面的几率进一步降低,也就是N+28其作为保护环的效率进一步提升,所以N+28的宽度可以设计更小,节省版图面积;另外N+28兼具N阱(N_Well60)接出点(Pickup)的作用,所以可以进一步将如图2中的已存在的无回滞效应硅控整流器中的N阱接出点(N+30)去除,进一步节省版图面积。虽然该方案进一步节省了版图面积,但随着器件小型化的趋势,提出了更高的版图面积要求硅控整流器的版图面积有进一步缩小的技术需求。

发明内容

在发明内容部分中引入了一系列简化形式的概念,该简化形式的概念均为本领域现有技术简化,这将在具体实施方式部分中进一步详细说明。本发明的发明内容部分并不意味着要试图限定出所要求保护的技术方案的关键特征和必要技术特征,更不意味着试图确定所要求保护的技术方案的保护范围。

本发明要解决的技术问题是提供一种相对现有技术能减小整体器件尺寸,缩减版图面积且无回滞效应的硅控整流器。

本发明要解决的另一技术问题是提供一种相对现有技术能减小整体器件尺寸,缩减版图面积且无回滞效应的硅控整流器制造方法。

为解决上述技术问题,本发明提供一种硅控整流器,包括:

P型半导体衬底80;

N阱60和P阱70,形成于P型半导体衬底80上部;

第一高浓度P型掺杂区20和第一高浓度N型掺杂区28,形成于N阱60上部;

第二高浓度N型掺杂区24和第二高浓度P型掺杂区26,形成于P阱70上部;

第三高浓度P型掺杂区22,形成于N阱60和P阱70分界处上方,且与第二高浓度N型掺杂区24邻接;第三高浓度P型掺杂区22上表面形成非金属硅化层;

其中,第一高浓度P型掺杂区20、N阱60和P阱70构成寄生PNP三极管结构,N阱60、P型半导体衬底80或P阱70与第二高浓度N型掺杂区24构成寄生NPN三极管结构;

第一高浓度P型掺杂区20和第一高浓度N型掺杂区28之间形成有第一宽度S的N阱60,第一高浓度N型掺杂区28和第三高浓度P型掺杂区22之间形成有第二宽度D1的N阱60,第一高浓度N型掺杂区28宽度为第三宽度D2,第三高浓度P型掺杂区22宽度为第四宽度D3。

可选择的,进一步改进所述的硅控整流器,第一浅沟槽隔离10,与第一高浓度P型掺杂区20邻接,形成在第一高浓度P型掺杂区20左侧N阱60中;

第二浅沟槽隔离14,与第二高浓度N型掺杂区24和第二高浓度P型掺杂区26邻接,形成在第二高浓度N型掺杂区24和第二高浓度P型掺杂区26之间P阱70中;

第三浅沟槽隔离16,与第二高浓度P型掺杂区26邻接,形成在第二高浓度P型掺杂区26右侧P阱70中。

可选择的,进一步改进所述的硅控整流器,第一宽度S范围是0.2um~10um,第二宽度D1范围是0.2~2um,第三宽度D2范围是0.2um~5u um,第四宽度D3范围是0.2um~10um。

可选择的,进一步改进所述的硅控整流器,其能通过调节第一宽度S、第三宽度D2和第四宽度D3来调节维持电压实现无回滞效应特性。

可选择的,进一步改进所述的硅控整流器,其能通过调节第四宽度D3降低寄生NPN三极管的电流增益。

可选择的,进一步改进所述的硅控整流器,其能通过调节第二宽度D1调节其回滞效应时的触发电压。

可选择的,进一步改进所述的硅控整流器,其用于ESD保护时,通过金属将第一高浓度P型掺杂区20和第一高浓度N型掺杂区28连接作为ESD保护结构的阳极,通过金属将第二高浓度N型掺杂区24和第二高浓度P型掺杂区26连接作为ESD保护结构的阴极。

为解决上述技术问题,本发明提供一种硅控整流器制造方法,包括以下步骤:

S1,在P型半导体衬底80中形成N阱60与P阱70;

S2,在N阱60中形成第一高浓度P型掺杂区20和第一高浓度N型掺杂区28,在P阱60中形成第二高浓度N型掺杂区24和第二高浓度P型掺杂区26,并在N阱60和P阱70分界处形成第三高浓度P型掺杂区22,第三高浓度P型掺杂区22与第二高浓度N型掺杂区24邻接;第三高浓度P型掺杂区22上表面形成非金属硅化层;

其中,第一高浓度P型掺杂区20、N阱60和P阱70构成寄生PNP三极管结构,N阱60、P型半导体衬底80或P阱70与第二高浓度N型掺杂区24构成寄生NPN三极管结构;

第一高浓度P型掺杂区20和第一高浓度N型掺杂区28之间形成有第一宽度S的N阱60,第一高浓度N型掺杂区28和第三高浓度P型掺杂区22之间形成有第二宽度D1的N阱60,第一高浓度N型掺杂区28宽度为第三宽度D2,第三高浓度P型掺杂区22宽度为第四宽度D3。

可选择的,进一步改进所述的硅控整流器制造方法,在步骤S1和S2之间增加制作浅沟槽隔离的步骤;

第一浅沟槽隔离10形成在第一高浓度P型掺杂区20左侧N阱60中,并与第一高浓度P型掺杂区20邻接;

第二浅沟槽隔离14形成在第二高浓度N型掺杂区24和第二高浓度P型掺杂区26之间P阱70中,并与第二高浓度N型掺杂区24和第二高浓度P型掺杂区26邻接;

第三浅沟槽隔离16形成在第二高浓度P型掺杂区26右侧P阱70中,并与第二高浓度P型掺杂区26邻接。

可选择的,进一步改进所述的硅控整流器制造方法,第一宽度S范围是0.2um~10um,第二宽度D1范围是0.2~2um,第三宽度D2范围是0.2um~5u m,第四宽度D3范围是0.2um~10um。

可选择的,进一步改进所述的硅控整流器制造方法,步骤S2中,通过调节第一宽度S、第三宽度D2和第四宽度D3来调节维持电压实现无回滞效应特性。

可选择的,进一步改进所述的硅控整流器制造方法,步骤S2中,通过调节第四宽度D3降低寄生NPN三极管的电流增益。

可选择的,进一步改进所述的硅控整流器制造方法,步骤S2中,通过调节第二宽度D1调节其回滞效应时的触发电压。

可选择的,进一步改进所述的硅控整流器制造方法,其用于ESD保护时,通过金属将第一高浓度P型掺杂区20和第一高浓度N型掺杂区28连接用于ESD保护时的阳极,通过金属将第二高浓度N型掺杂区24和第二高浓度P型掺杂区26连接用于ESD保护时的阴极。

本发明将现有技术图4所示无回滞效应硅控整流器中的浅沟槽隔离STI 12去除,再将第三高浓度P型掺杂区22向阴极方向延伸与第二高浓度N型掺杂区24邻接,降低电子从寄生NPN(第二高浓度N型掺杂区24/P阱70/N阱60)三极管的发射极第二高浓度N型掺杂区24注入并迁移到达N阱60与P阱70界面的几率,也就是降低了寄生NPN三极管的电流增益(β),进而能减小实现无回滞效应所需的保护环(第一高浓度N型掺杂区28)的宽度D2,因此能节省版图面积。

附图说明

本发明附图旨在示出根据本发明的特定示例性实施例中所使用的方法、结构和/或材料的一般特性,对说明书中的描述进行补充。然而,本发明附图是未按比例绘制的示意图,因而可能未能够准确反映任何所给出的实施例的精确结构或性能特点,本发明附图不应当被解释为限定或限制由根据本发明的示例性实施例所涵盖的数值或属性的范围。下面结合附图与具体实施方式对本发明作进一步详细的说明:

图1是常规高压器件LDMOS回滞效应曲线示意图。

图2是第一种现有无回滞效应硅控整流器结构示意图。

图3是图2所示无回滞效应硅控整流器回滞效应曲线D2关系示意图。

图4是第二种现有无回滞效应硅控整流器结构示意图。

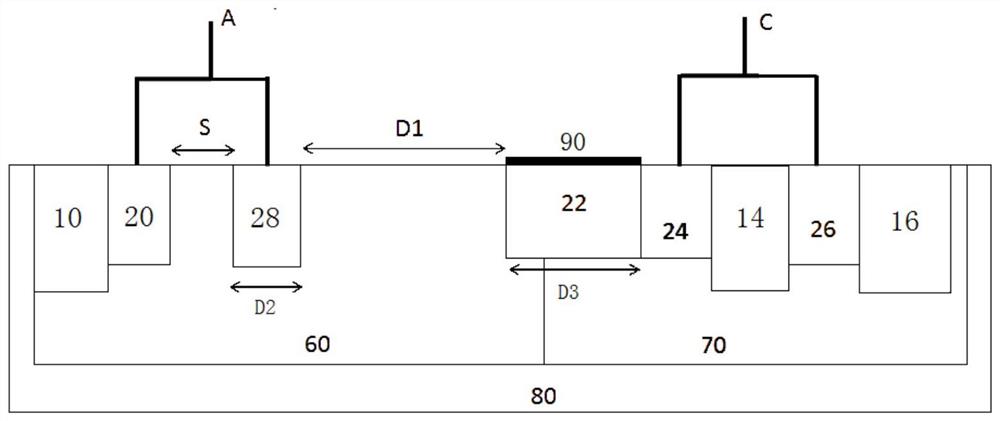

图5是本发明结构示意图。

图6是本发明具体应用示意图。

附图标记说明

20、22、26 表示不同的高浓度P型掺杂区

24、28、30 表示不同的高浓度N型掺杂区

10、12、14、16 表示不同的浅沟槽隔离

60 表示N阱

70 表示P阱

80 表示P型半导体衬底

90 表示非金属硅化层

A 表示阳极

C 表示阴极

S 表示第一高浓度P型掺杂区20和第一高浓度N型掺杂区28之间宽度

D1 表示第一高浓度N型掺杂区28和第三高浓度P型掺杂区22之间宽度

D2 表示第一高浓度N型掺杂区28和现有技术结构中第三高浓度P型掺杂区22的宽度;

D3 表示本发明结构中第三高浓度P型掺杂区22的宽度。

具体实施方式

以下通过特定的具体实施例说明本发明的实施方式,本领域技术人员可由本说明书所公开的内容充分地了解本发明的其他优点与技术效果。本发明还可以通过不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点加以应用,在没有背离发明总的设计思路下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。本发明下述示例性实施例可以多种不同的形式来实施,并且不应当被解释为只限于这里所阐述的具体实施例。应当理解的是,提供这些实施例是为了使得本发明的公开彻底且完整,并且将这些示例性具体实施例的技术方案充分传达给本领域技术人员。

此外,还应当理解的是,尽管在这里可以使用术语“第一”、“第二”等来描述不同的元件、参数、组件、区域、层和/或部分,但是这些元件、参数、组件、区域、层和/或部分不应当受这些术语的限制。这些术语仅是用来将一个元件、参数、组件、区域、层或部分与另一个元件、参数、组件、区域、层或部分区分开来。因此,在不脱离根据本发明的示例性实施例的教导的情况下,以下所讨论的第一元件、参数、组件、区域、层或部分也可以被称作第二元件、参数、组件、区域、层或部分。

第一实施例;

参考图5所示,本发明提供一种硅控整流器,包括:

P型半导体衬底80;

N阱60和P阱70,形成于P型半导体衬底80上部;

第一高浓度P型掺杂区20和第一高浓度N型掺杂区28,形成于N阱60上部;

第二高浓度N型掺杂区24和第二高浓度P型掺杂区26,形成于P阱70上部;

第三高浓度P型掺杂区22,形成于N阱60和P阱70分界处上方,且与第二高浓度N型掺杂区24邻接;第三高浓度P型掺杂区22上表面形成非金属硅化层90;

第一高浓度P型掺杂区20左侧形成有第一浅沟槽隔离10,第二高浓度N型掺杂区24和第二高浓度P型掺杂区26之间形成有第二浅沟槽隔离14,第二高浓度P型掺杂区26右侧形成有第三浅沟槽隔离16;

第一高浓度P型掺杂区20、N阱60和P阱70构成寄生PNP三极管结构,N阱60、P型半导体衬底80或P阱70与第二高浓度N型掺杂区24构成寄生NPN三极管结构,第一高浓度P型掺杂区20和第一高浓度N型掺杂区28之间形成有第一宽度S的N阱60,第一高浓度N型掺杂区28和第三高浓度P型掺杂区22之间形成有第二宽度D1的N阱60,第一高浓度N型掺杂区28宽度为第三宽度D2,第三高浓度P型掺杂区22宽度为第四宽度D3。

相应的,根据图4所示现有技术结构比较,可以发现理论上图5中的第三高浓度P型掺杂区22的宽度D3应大于图4中的第三高浓度P型掺杂区22的宽度D3。

本发明提供硅控整流器是在现有的无回滞效应硅控整流器,如图4所示结构的基础上进一步改进形成。将该无回滞效应硅控整流器中的浅沟槽隔离STI 12去除,再将第三高浓度P型掺杂区22向阴极方向延伸与第二高浓度N型掺杂区24邻接,降低电子从寄生NPN(第二高浓度N型掺杂区24/P阱70/N阱60)三极管的发射极第二高浓度N型掺杂区24注入并迁移到达N阱60与P阱70界面的几率,也就是降低了寄生NPN三极管的电流增益(β),进而能减小实现无回滞效应所需的保护环(第一高浓度N型掺杂区28)的宽度D2,因此能节省版图面积。

第二实施例;

继续参考图5所示,本发明提供一种硅控整流器,包括:

P型半导体衬底80;

N阱60和P阱70,形成于P型半导体衬底80上部;

第一高浓度P型掺杂区20和第一高浓度N型掺杂区28,形成于N阱60上部;

第二高浓度N型掺杂区24和第二高浓度P型掺杂区26,形成于P阱70上部;

第三高浓度P型掺杂区22,形成于N阱60和P阱70分界处上方,且与第二高浓度N型掺杂区24邻接;第三高浓度P型掺杂区22上表面形成非金属硅化层90;

第一浅沟槽隔离10,与第一高浓度P型掺杂区20邻接,形成在第一高浓度P型掺杂区20左侧N阱60中;

第二浅沟槽隔离14,与第二高浓度N型掺杂区24和第二高浓度P型掺杂区26邻接,形成在第二高浓度N型掺杂区24和第二高浓度P型掺杂区26之间P阱70中;

第三浅沟槽隔离16,与第二高浓度P型掺杂区26邻接,形成在第二高浓度P型掺杂区26右侧P阱70中;

第一高浓度P型掺杂区20、N阱60和P阱70构成寄生PNP三极管结构,N阱60、P型半导体衬底80或P阱70与第二高浓度N型掺杂区24构成寄生NPN三极管结构;

第一高浓度P型掺杂区20和第一高浓度N型掺杂区28之间形成有第一宽度S的N阱60,第一高浓度N型掺杂区28和第三高浓度P型掺杂区22之间形成有第二宽度D1的N阱60,第一高浓度N型掺杂区28宽度为第三宽度D2,第三高浓度P型掺杂区22宽度为第四宽度D3;

其中,第一宽度S范围是0.2um~10um,第二宽度D1范围是0.2~2um,第三宽度D2范围是0.2um~5um,第四宽度D3范围是0.2um~10um。

需要进一步说明的是,无论上述第一实施例或第二实施例,均能通过调节第一宽度S、第三宽度D2和第四宽度D3来调节维持电压实现无回滞效应特性。

无论上述第一实施例或第二实施例,均能通过调节第四宽度D3降低寄生NPN三极管的电流增益。

无论上述第一实施例或第二实施例,均能通过调节第二宽度D1调节其回滞效应时的触发电压。

相应的,无论上述第一实施例或第二实施例用于ESD保护时,通过金属将第一高浓度P型掺杂区20和第一高浓度N型掺杂区28连接作为ESD保护结构的阳极,通过金属将第二高浓度N型掺杂区24和第二高浓度P型掺杂区26连接作为ESD保护结构的阴极,具体应用结构如图6所示。

在此,参照作为示例性实施例的优选实施例(和中间结构)的示意性剖面图来描述根据本发明的示例性实施例。这样,预计会出现例如由制造技术和/或容差引起的示出的形状的变化。因此,示例性实施例不应当被解释为仅限于在此示出的区域的具体形状,而是还可以包含例如由制造所导致的形状偏差。例如,示出为矩形的注入区域在其边缘可以具有倒圆或弯曲的特征和/或注入浓度的梯度变化,而不仅是从注入区域到非注入区域的二元变化。同样,通过注入形成的掩埋区会导致在该掩埋区与注入通过的表面之间的区域中也会存在一些注入。因此,图所示出的区域实质上是示意性的,它们的形状并非意图示出器件中的各区域的实际形状,而且也并非意图限制根据本发明的示例性实施例的范围。

第三实施例;

本发明提供一种硅控整流器制造方法,包括以下步骤:

S1,在P型P型半导体衬底80中形成N阱60与P阱70;

S2,在N阱60中形成第一高浓度P型掺杂区20和第一高浓度N型掺杂区28,在P阱60中形成第二高浓度N型掺杂区24和第二高浓度P型掺杂区26,并在N阱60和P阱70分界处形成第三高浓度P型掺杂区22,第三高浓度P型掺杂区22与第二高浓度N型掺杂区24邻接;第三高浓度P型掺杂区22上表面形成非金属硅化层90;

其中,第一高浓度P型掺杂区20、N阱60和P阱70构成寄生PNP三极管结构,N阱60、P型半导体衬底80或P阱70与第二高浓度N型掺杂区24构成寄生NPN三极管结构;

第一高浓度P型掺杂区20和第一高浓度N型掺杂区28之间形成有第一宽度S的N阱60,第一高浓度N型掺杂区28和第三高浓度P型掺杂区22之间形成有第二宽度D1的N阱60,第一高浓度N型掺杂区28宽度为第三宽度D2,第三高浓度P型掺杂区22宽度为第四宽度D3。

第四实施例;

本发明提供一种硅控整流器制造方法,包括以下步骤:

S1,在P型P型半导体衬底80中形成N阱60与P阱70;

然后,制作浅沟槽隔离;

第一浅沟槽隔离10形成在第一高浓度P型掺杂区20左侧N阱60中,并与第一高浓度P型掺杂区20邻接;

第二浅沟槽隔离14形成在第二高浓度N型掺杂区24和第二高浓度P型掺杂区26之间P阱70中,并与第二高浓度N型掺杂区24和第二高浓度P型掺杂区26邻接;

第三浅沟槽隔离16形成在第二高浓度P型掺杂区26右侧P阱70中,并与第二高浓度P型掺杂区26邻接。

S2,在N阱60中形成第一高浓度P型掺杂区20和第一高浓度N型掺杂区28,在P阱60中形成第二高浓度N型掺杂区24和第二高浓度P型掺杂区26,并在N阱60和P阱70分界处形成第三高浓度P型掺杂区22,第三高浓度P型掺杂区22与第二高浓度N型掺杂区24邻接;第三高浓度P型掺杂区22上表面形成非金属硅化层90;

第一高浓度P型掺杂区20、N阱60和P阱70构成寄生PNP三极管结构,N阱60、P型半导体衬底80或P阱70与第二高浓度N型掺杂区24构成寄生NPN三极管结构;

第一高浓度P型掺杂区20和第一高浓度N型掺杂区28之间形成有第一宽度S的N阱60,第一高浓度N型掺杂区28和第三高浓度P型掺杂区22之间形成有第二宽度D1的N阱60,第一高浓度N型掺杂区28宽度为第三宽度D2,第三高浓度P型掺杂区22宽度为第四宽度D3。

其中,第一宽度S范围是0.2um~10um,第二宽度D1范围是0.2~2um,第三宽度D2范围是0.2um~5um,第四宽度D3范围是0.2um~10um。

需要进一步说明的是,无论上述第三实施例或第四实施例,均能通过调节第一宽度S、第三宽度D2和第四宽度D3来调节维持电压实现无回滞效应特性。

无论上述第三实施例或第四实施例,均能通过调节第四宽度D3降低寄生NPN三极管的电流增益。

无论上述第三实施例或第四实施例,均能通过调节第二宽度D1调节其回滞效应时的触发电压。

相应的,无论上述第三实施例或第四实施例用于ESD保护时,通过金属将第一高浓度P型掺杂区20和第一高浓度N型掺杂区28连接作为ESD保护结构的阳极,通过金属将第二高浓度N型掺杂区24和第二高浓度P型掺杂区26连接作为ESD保护结构的阴极。

除非另有定义,否则这里所使用的全部术语(包括技术术语和科学术语)都具有与本发明所属领域的普通技术人员通常理解的意思相同的意思。还将理解的是,除非这里明确定义,否则诸如在通用字典中定义的术语这类术语应当被解释为具有与它们在相关领域语境中的意思相一致的意思,而不以理想的或过于正式的含义加以解释。

以上通过具体实施方式和实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

- 一种硅控整流器及其制造方法

- 一种硅控整流器及其制造方法