记忆卡的读写控制系统及其方法

文献发布时间:2023-06-19 10:51:07

技术领域

本发明系关于一种电子装置及其方法,特别是关于一种记忆卡的读写控制系统及其方法。

背景技术

随着信息技术的快速发展,电子产品的应用日益普及,例如笔记本电脑、手机、平板计算机等手持式电子装置处处可见。由于这些电子装置的特点是可随身携带、随时随地使用,并且为了使各种电子装置之间可以互相联机以进行较大量的数据传输,故通常是以记忆卡插接于卡片阅读机使上述的电子产品可擦写该记忆卡的数据,以扩充该电子产品的内存储存容量。

然而随着记忆卡的数据访问速度越来越快,无法以较旧版本规格的控制方式来存取较新版本规格的记忆卡,致使较新规格的记忆卡无法在较旧版本规格的卡片阅读机中使用,造成记忆卡与卡片阅读机控制芯片之间兼容性的问题,并且降低记忆卡的使用弹性。当同样以较新版本规格的控制方式来存取较新版本规格的记忆卡,其该控制方式的传输带宽远大于较旧版本规格的传输带宽,使记忆卡与卡片阅读机控制芯片之间的通信设计较为复杂,造成控制芯片的成本提高。有鉴于此,目前仍需要发展一种新式的电子装置及其方法,以改善上述问题。

发明内容

本发明之一目的在于提供一种记忆卡的读写控制系统及其方法,藉由控制装置的控制模块以及第一选择器,使主机系统只需透过一个接口,即可以不同的通讯协议读写记忆卡的数据,解决记忆卡与读写控制系统之间兼容性的问题,并且提高记忆卡的使用弹性,同时降低读写控制系统的生产成本。

为达成上述目的,本发明之一实施例中的读写控制系统,用以控制一记忆卡的数据之读写,该读写控制系统包括:一记忆卡接口,用以连接该记忆卡;一主机系统接口,电性连接该记忆卡接口,且该主机系统连接该主机系统接口;以及一控制装置,包括一控制模块以及一第一选择器,该控制模块电性连接该记忆卡接口、该主机系统接口以及该第一选择器,该第一选择器电性连接该记忆卡接口以及该主机系统接口,该控制模块包括:一桥接装置,电性连接该主机系统接口、该记忆卡接口以及该第一选择器;以及一第二选择器,电性连接该主机系统接口、该记忆卡接口以及该桥接装置;其中,当该记忆卡以一第一通讯协议运作时,该记忆卡接口经该第二选择器、该桥接装置以及该第一选择器来与该主机系统接口电性连接;其中,当该记忆卡以一第二通讯协议运作时,该记忆卡接口经该第二选择器来与该主机系统接口电性连接,该记忆卡接口亦经该第一选择器来与该主机系统接口电性连接。

在一实施例中,该控制装置侦测该记忆卡电性连接该记忆卡接口,并默认以该第一通讯协议与该记忆卡连接,以该第一通讯协议启动该记忆卡。

在一实施例中,该桥接装置包括:一第一接口,电性连接该主机系统接口以及该第一选择器;以及一第二接口,电性连接该记忆卡接口、该第一接口以及该第二选择器;其中,当该记忆卡以该第一通讯协议运作时,该记忆卡接口经由该第二选择器、该第二接口以及该第一接口,并且经由该控制装置的该第一选择器,以与该主机系统接口电性连接,其中该记忆卡接口、该第二接口、该第一接口以及该主机系统接口间的传输路径定义为一第一传输路径,该记忆卡接口、该第二选择器、该第二接口、该第一接口、该第一选择器以及该主机系统接口间的传输路径定义为一第二传输路径,使该主机系统透过该第一传输路径以与该记忆卡接口通讯并且透过该第二传输路径以该第一通讯协议读写该记忆卡的该数据;其中,当该记忆卡以该第二通讯协议运作时,该记忆卡接口经由该第二选择器以及该第一接口,以与该主机系统接口电性连接,并且该记忆卡接口经由该控制装置的该第一选择器,以与该主机系统接口电性连接,其中该记忆卡接口、该第二选择器以及该主机系统接口间的传输路径定义为一第三传输路径,该记忆卡接口、该第一选择器以及该主机系统接口间的传输路径定义为一第四传输路径,使该主机系统透过该第三传输路径以与该记忆卡接口通讯并且透过该第四传输路径以该第二通讯协议读写该记忆卡的该数据。

在一实施例中,该主机系统接口包括一第一子接口以及一第二子接口,该第一选择器包括一第一传收端以及一第二传收端,当该记忆卡以该第一通讯协议运作时,该主机系统透过该主机系统接口以一第一触发信号触发该第一选择器的该第一传收端,以让该记忆卡接口透过该桥接装置以及该第一传收端电性连接该主机系统接口的该第二子接口,该记忆卡接口亦透过该第二选择器以及该桥接装置电性连接该主机系统接口的该第一子接口。

在一实施例中,当该记忆卡以该第二通讯协议运作时,该第二接口以一第二触发信号触发该第二选择器,以让该记忆卡接口透过该第二选择器电性连接该主机系统接口的该第一子接口,且该主机系统透过该主机系统接口以该第一触发信号触发该第一选择器的该第二传收端,以让该记忆卡接口透该第二传收端电性连接该主机系统接口的该第二子接口。

在一实施例中,当该记忆卡以该第二通讯协议运作时,该主机系统接口断开该第一选择器的该第一传收端。

在一实施例中,该主机系统透过该主机系统接口、该第一选择器的该第二传收端以及该第二选择器与该记忆卡通讯,以判断该记忆卡是否支持该主机系统的协议版本,该协议版本包括PCIe1.0、PCIe2.0以及PCIe3.0协议版本。

在一实施例中,当该主机系统经该主机系统接口确认该记忆卡的该第一通讯协议支持该主机系统的PCIe1.0协议版本或是PCIe2.0协议版本,该主机系统透过该主机系统接口与该第一选择器的该第一传收端读写该记忆卡的该数据,当该主机系统经该主机系统接口确认该记忆卡的该第二通讯协议支持该主机系统的PCIe3.0协议版本,该主机系统透过该主机系统接口与该第一选择器的该第二传收端读写该记忆卡的该数据。

在一实施例中,该桥接装置更包括一非挥发性内存快捷协议控制器,透过该第一接口电性连接该第一选择器,并与该主机系统接口的该第二子接口电性连接,当该记忆卡不支持该第二通讯协议的运作时,该主机系统透过该主机系统接口与该非挥发性内存快捷协议控制器存取该记忆卡的数据,当该记忆卡支持该第二通讯协议的运作时,该主机系统的一非挥发性内存快捷(NVMe)协议驱动程序透过该主机系统接口以及该第一选择器的该第二传收端存取该记忆卡的数据。

在一实施例中,该记忆卡的该第一通讯协议定义为安全数字(SD)模式,该记忆卡的该第二通讯协议定义为快捷安全数字(SD Express)模式。

在一实施例中,该记忆卡的该第一通讯协议的数据传输率小于该第二通讯协议的数据传输率。

本发明之另一实施例中的读写控制系统,用以控制一记忆卡的数据之读写,该读写控制系统包括:一第一传输路径,连接于一记忆卡接口、一桥接装置以及一主机系统接口之间,其中该记忆卡接口用以连接该记忆卡;一第二传输路径,连接于该记忆卡接口、一第二选择器、该桥接装置、一第一选择器以及该主机系统接口之间;一第三传输路径,连接于该记忆卡接口、该第二选择器以及该主机系统接口之间;以及一第四传输路径,连接于该记忆卡接口、该第一选择器以及该主机系统接口之间;其中,当该记忆卡以该第一通讯协议运作时,该主机系统经该主机系统接口透过该第一传输路径以与该记忆卡接口通讯并且透过该第二传输路径以该第一通讯协议读写该记忆卡的该数据;其中,当该记忆卡以该第二通讯协议运作时,该主机系统经该主机系统接口透过该第三传输路径以与该记忆卡接口通讯并且透过该第四传输路径以该第二通讯协议读写该记忆卡的该数据。

在一实施例中,该主机系统接口包括一第一子接口以及一第二子接口,该桥接装置包括一第一接口以及一第二接口,该第一选择器包括一第一传收端以及一第二传收端,当该记忆卡以该第一通讯协议运作时,该主机系统经该主机系统接口以一第一触发信号触发该第一选择器的该第一传收端,以让该记忆卡接口透过该桥接装置以及该第一传收端电性连接该主机系统接口的该第二子接口,该记忆卡接口亦透过该第二选择器以及该桥接装置电性连接该主机系统接口的该第一子接口。

在一实施例中,当该记忆卡以该第二通讯协议运作时,该第二接口以一第二触发信号触发该第二选择器,以让该记忆卡接口透过该第二选择器电性连接该主机系统接口的该第一子接口,且该主机系统接口以该第一触发信号触发该第一选择器的该第二传收端,以让该记忆卡接口透该第二传收端电性连接该主机系统接口的该第二子接口。

在一实施例中,当该记忆卡以该第二通讯协议运作时,该主机系统接口断开该第一选择器的该第一传收端。

本发明之又一实施例中的读写控制方法,以供一主机系统透过该读写控制系统读写一记忆卡,用于读写控制系统,该读写控制系统包括一记忆卡接口、一主机系统接口以及一控制装置,该控制装置包括一控制模块以及一第一选择器,该控制模块包括一桥接装置以及第二选择器,该桥接装置包括该一第一接口以及一第二接口,该主机系统接口包括一第一子接口以及一第二子接口,该第一选择器包括一第一传收端以及一第二传收端,该读写控制方法包括下列步骤:

该主机系统经该主机系统接口以一第一触发信号触发该第一选择器的该第一传收端,该主机系统经由该主机系统接口、该第一选择器的该第一传收端以及该控制模块电性连接该记忆卡接口;

侦测该记忆卡连接于该记忆卡接口,并以一第一通讯协议与该记忆卡进行连接;

判断该记忆卡是否支持一第二通讯协议的运作;

当判断该记忆卡不支持该第二通讯协议的运作时,该记忆卡接口经该第二选择器、该桥接装置以及该第一选择器来与该主机系统接口电性连接,使该主机系统透过该主机系统接口以该第一通讯协议读写该记忆卡的该数据;

当判断该记忆卡支持该第二通讯协议运作时,该记忆卡接口经该第二选择器来与该主机系统接口电性连接,该记忆卡接口亦经该第一选择器来与该主机系统接口电性连接,并且该主机系统透过该主机系统接口与该控制装置的该第一选择器的该第二传收端,以该第二通讯协议读写该记忆卡的该数据。

在一实施例中,该主机系统接口侦测出该记忆卡连接于该记忆卡接口的步骤之后,还包括该第二接口产生一第二触发信号以触发该第二选择器。

在一实施例中,侦测该记忆卡连接于该记忆卡接口的步骤之后,该主机系统透过该主机系统接口与该桥接装置的该第一接口以及该第二接口,以该第一通讯协议启动该记忆卡,当判断该记忆卡支持该第二通讯协议运作之后,以该第二通讯协议启动该记忆卡。

在一实施例中,当该记忆卡以该第二通讯协议运作时,该第二接口以一第二触发信号触发该第二选择器,以让该记忆卡接口透过该第二选择器电性连接该主机系统接口的该第一子接口。

在一实施例中,当该记忆卡以该第二通讯协议运作时,该主机系统透过该主机系统接口以一第一触发信号触发该第一选择器的该第二传收端,以让该记忆卡接口透该第二传收端电性连接该主机系统接口的该第二子接口。

在一实施例中,当该记忆卡以该第二通讯协议运作时,该主机系统接口断开该第一选择器的该第一传收端。

在一实施例中,该主机系统透过该主机系统接口、该第一选择器的该第二传收端以及该第二选择器与该记忆卡通讯,以判断该记忆卡是否支持该主机系统的协议版本,该协议版本包括PCIe1.0、PCIe2.0以及PCIe3.0协议版本。

在一实施例中,当确认该记忆卡的该第一通讯协议支持该主机系统接口的PCIe1.0协议版本或是PCIe2.0协议版本,该主机系统透过该主机系统接口与该第一选择器的该第一传收端读写该记忆卡的该数据,当确认该记忆卡的该第二通讯协议支持该主机系统的PCIe3.0协议版本,该主机系统透过该主机系统接口与该第一选择器的该第二传收端读写该记忆卡的该数据。

在一实施例中,该记忆卡的该第一通讯协议定义为安全数字(SD)模式,该记忆卡的该第二通讯协议定义为快捷安全数字(SD Express)模式。

在一实施例中,该记忆卡的该第一通讯协议的数据传输率小于该第二通讯协议的数据传输率。

在一实施例中,该桥接装置更包括一非挥发性内存快捷协议控制器,透过该第一接口电性连接该第一选择器,并与该主机系统接口的该第一子接口电性连接,当该记忆卡不支持该第二通讯协议的运作时,该主机系统透过该主机系统接口与该非挥发性内存快捷协议控制器存取该记忆卡的数据,当该记忆卡支持该第二通讯协议的运作时,该主机系统的一非挥发性内存快捷(NVMe)协议驱动程序透过该主机系统接口以及该第一选择器的该第二传收端存取该记忆卡的数据。

本发明之读写控制系统及其方法,藉由控制装置的控制模块以及第一选择器,使主机系统只需透过一个接口,即可以不同的通讯协议读写记忆卡的数据,解决记忆卡与读写控制系统之间兼容性的问题,并且提高记忆卡的使用弹性,同时降低读写控制系统的生产成本。

附图说明

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本发明所属技术领域中具有通常知识者来讲,还可以根据这些附图获得其他的附图。

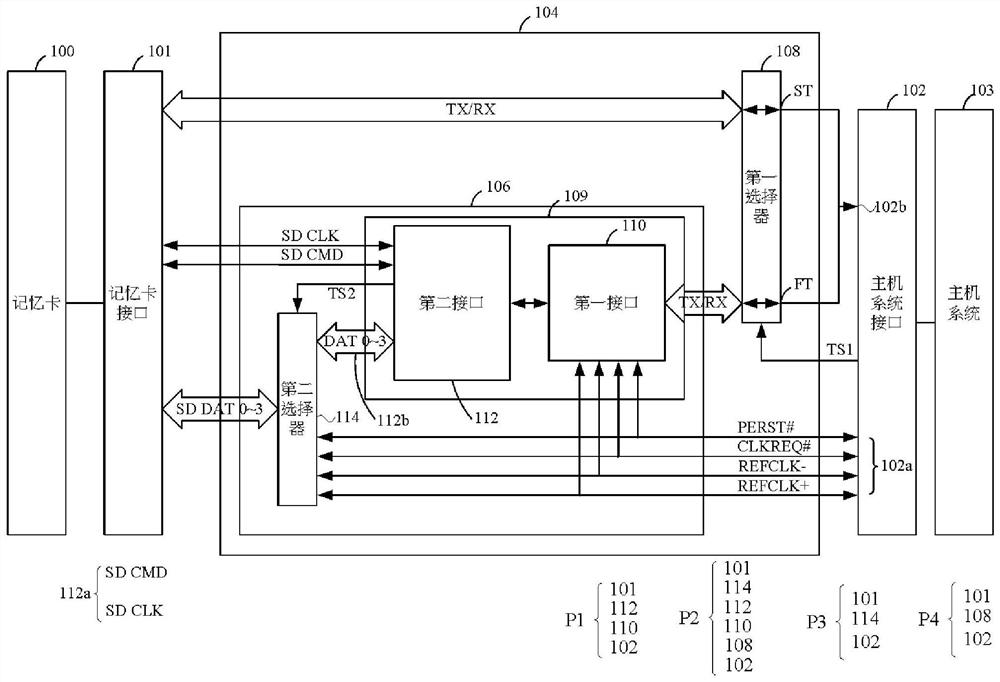

图1为绘示依据本发明第一实施例中读写控制系统之方块图;

图2为绘示依据本发明第二实施例中读写控制系统之方块图;

图3为绘示依据本发明第一实施例中读写控制方法之流程图;及

图4-5为绘示依据本发明第二实施例中读写控制方法之流程图。

具体实施方式

请参照图式,其中相同的组件符号代表相同的组件或是相似的组件,本发明的原理是以实施在适当的运算环境中来举例说明。以下的说明是基于所例示的本发明具体实施例,其不应被视为限制本发明未在此详述的其它具体实施例。

参考第1图,其系绘示依据本发明第一实施例中读写控制系统之方块图。该读写控制系统用以供一主机系统103读写一记忆卡100的数据。该读写控制系统包括记忆卡接口101、主机系统接口102以及控制装置104。

如第1图所示,该记忆卡接口101用以连接该记忆卡100。该主机系统接口102电性连接该记忆卡接口101,且该主机系统103连接该主机系统接口102。该控制装置104连接于记忆卡接口101与主机系统接口102之间。该控制装置 104包括控制模块106以及第一选择器108,该控制模块106电性连接该记忆卡接口101、该主机系统接口102以及该第一选择器108,该第一选择器108电性连接该记忆卡接口101以及该主机系统接口102。该控制模块106包括桥接装置109以及第二选择器114,该桥接装置109电性连接该主机系统接口102、该记忆卡接口101以及该第一选择器108,该第二选择器114电性连接该主机系统接口102、该记忆卡接口101以及该桥接装置109。其中,当该记忆卡100 以第一通讯协议运作时,该记忆卡接口101经该第二选择器114、该桥接装置 109以及该第一选择器108来与该主机系统接口102电性连接。当该记忆卡100 以第二通讯协议运作时,该记忆卡接口101经该第二选择器114来与该主机系统接口102电性连接,该记忆卡接口101亦经该第一选择器101来与该主机系统接口102电性连接。

如第1图所示,在一实施例中,该主机系统103经该控制装置104侦测出该记忆卡接口101电性连接该主机系统接口102,并以该第一通讯协议与该记忆卡100连接,以该第一通讯协议初始化或启动(Initialization process)该记忆卡 100。该初始化例如是该主机系统接口102对该记忆卡100提供运作所需要的电力,该主机系统接口102对该记忆卡100传送运作、存取的指令,透过该记忆卡接口101以建立该主机系统接口102与该记忆卡100之间双向通信。如第1 图所示,在一实施例中,该桥接装置109包括第一接口110以及第二接口112。该第一接口110电性连接该主机系统接口102以及该第一选择器108,该第二接口112电性连接该记忆卡接口101、该第一接口110以及该第二选择器114。

如第1图所示,在一实施例中,当该记忆卡100以该第一通讯协议运作时,该记忆卡100的该第一通讯协议例如为安全数字(SD)模式时,该记忆卡接口101 可经由该第二选择器114、该第二接口110以及该第一接口112,并且经由该控制装置104的该第一选择器108,以与该主机系统接口102电性连接,其中该记忆卡接口101、该第二接口112、该第一接口110以及该主机系统接口102 间的传输路径定义为第一传输路径P1,该记忆卡接口101、该第二选择器114、该第二接口112、该第一接口110、该第一选择器108以及该主机系统接口102 间的传输路径定义为第二传输路径P2,使该主机系统接口102透过该第一传输路径P1以与该记忆卡接口101通讯并且透过该第二传输路径P2以该第一通讯协议读写该记忆卡100的该数据。在一实施例中,该主机系统接口102经该第一传输路径P1侦测出该记忆卡接口101电性连接该主机系统接口102。该主机系统接口102经该第一传输路径P1以该第一通讯协议对该记忆卡100初始化。在一较佳实施例中,在侦测该记忆卡100的连接过程中,该主机系统103例如是透过主机系统接口102与该桥接装置109的该第一接口110以及该第二接口 112,以该第一通讯协议初始化或启动该记忆卡100。

如第1图所示,在一实施例中,当该记忆卡100以该第二通讯协议运作时,例如该记忆卡100的第二通讯协议为快捷安全数字(SD Express)模式时,该记忆卡接口101经由该第二选择器114与该主机系统接口102电性连接,并且该记忆卡接口101经由该控制装置104的该第一选择器108,以与该主机系统接口 102电性连接,其中该记忆卡接口101、该第二选择器114以及该主机系统接口 102间的传输路径定义为第三传输路径P3,该记忆卡接口101、该第一选择器 108以及该主机系统接口102间的传输路径定义为第四传输路径P4,使该主机系统接口102透过该第三传输路径P3以与该记忆卡接口101通讯并且透过该第四传输路径P4以该第二通讯协议读写该记忆卡100的该数据。其中,在判断该记忆卡100支持该第二通讯协议运作后,本实施例例如会先以该第二通讯协议初始化或启动(Initializationprocess)该记忆卡100,以再进行后续的通讯或是读写作业。

如第1图所示,在一实施例中,记忆接口101例如是安全数字记忆卡(securedigital memory card)协议,如SD-UHS I、SD-UHS II、SD-UHS III、SD 7.0等协议版本,但不限于此。在一实施例中,该记忆卡100的该第一通讯协议定义为安全数字(SD)模式,例如是SD-UHS I、SD-UHS II、SD-UHS III协议版本。该记忆卡100的该第二通讯协议定义为快捷安全数字(SD Express)模式。该安全数字模式系为快捷安全数字模式以前的协议版本,该快捷安全数字模式系为安全数字(SD)7.0协议版本,例如是支持安全数字(SD)7.0协议版本或是之后更新的协议版本。该记忆卡100的该第一通讯协议的数据传输率小于该第二通讯协议的数据传输率。主机系统接口102例如是快捷周边组件互联根复合(peripheralcomponent interconnect express(PCIe)root complex)组件,用以将处理器与内存连接到由一个或多个交换装置组成的PCIe交换架构,可设置于笔记本电脑、手机、平板计算机,或是其他的处理器与内存连接的电子装置中。控制装置104 例如是卡片阅读机的控制芯片或是控制电路,但不限于此。

如第1图所示,在一实施例中,该主机系统接口102包括第一子接口102a 以及第二子接口102b,该第一选择器108包括第一传收端FT以及第二传收端 ST。例如,该第一子接口102a包括快捷周边组件互联重设(PCI Express Reset, PERST#)信号、频率请求运行信号(clock request,CLKREQ#)、以及参考频率差分对信号(reference clock,REFCLK+,REFCLK-),其中快捷周边组件互联重设 (PERST#)信号用以管理该第二子接口102b的复位运作;频率请求运行信号

(clock request,CLKREQ#)用以请求参考频率运行;参考频率差分对信号(reference clock,REFCLK+,REFCLK-)用以提供参考频率。第一子接口102a电性连接于该桥接装置109的第一接口110、以及该第二选择器114,用以传输上述4个信号,包括PERST#、CLKREQ#、REFCLK+、REFCLK-4个信号。该第二子接口102b用以执行接口装置102与记忆卡接口101之间的数据传送/接收(transmit/receive,TX/RX)。该第二子接口102b支持PCIe1.0、PCIe2.0以及 PCIe3.0协议版本。如PCIe1.0的传输带宽系为2.5GHz,如PCIe2.0的传输带宽系为5.0GHz,如PCIe3.0的传输带宽系为8.0GHz。第一传收端FT例如是一低速传收端,第二传收端ST例如是一高速传收端,但不以此为限,例如是第一传收端FT与第二传收端ST具有不同的传输带宽。

如第1图所示,在一实施例中,当该记忆卡100以该第一通讯协议运作时,该主机系统接口102以第一触发信号TS1触发该第一选择器108的该第一传收端FT,以让该记忆卡接口101透过该桥接装置109以及该第一传收端FT电性连接该主机系统接口102的该第二子接口102b,该记忆卡接口101亦透过该第二选择器114以及该桥接装置109电性连接该主机系统接口102的该第一子接口102a。第一传收端FT例如是一低速传收端,但不以此为限,例如是第一传收端FT与第二传收端ST具有不同的传输带宽。

如第1图所示,在一实施例中,当该记忆卡100以该第二通讯协议运作时,该桥接装置109的第二接口112以第二触发信号TS2触发该第二选择器114,以让该记忆卡接口101透过该第二选择器114电性连接该主机系统接口102的该第一子接口102a,且该主机系统接口102以该第一触发信号TS1触发该第一选择器108的该第二传收端ST,以让该记忆卡接口101透该第二传收端ST电性连接该主机系统接口102的该第二子接口102b。在一实施例中,当该记忆卡 100以该第二通讯协议运作时,该主机系统接口102断开该第一选择器108的该第一传收端FT。

如第1图所示,该主机系统103例如会经该主机系统接口102以透过该第一选择器108的该第二传收端ST以及该第二选择器114扫描该记忆卡100,以判断该记忆卡100是否支持该主机系统接口102的协议版本,该协议版本包括 PCIe1.0、PCIe2.0以及PCIe3.0协议版本。当确认该记忆卡100的该第一通讯协议支持该主机系统接口102的PCIe1.0协议版本或是PCIe2.0协议版本,该主机系统103例如会经该主机系统接口102以透过该第一选择器114的该第一传收端FT读写该记忆卡100的该数据。当确认该记忆卡100的该第二通讯协议支持该主机系统接口102的PCIe3.0协议版本,该主机系统103例如会经该主机系统接口102以透过该第一选择器108的该第二传收端ST读写该记忆卡100 的该数据。

如第1图所示,在一实施例中,该桥接装置109的第二接口112包括控制接口112a以及传收接口112b,该控制接口112a连接该记忆卡接口101,该传收接口112b连接该第二选择器114。控制接口112a包括安全数字指令(secure digital command,SD CMD)以及安全数字频率(secure digital clock,SD CLK)等信号,用以建立第二接口112与记忆卡接口101之间的通信链接。传收接口112b 包括安全数字数据(secure digital data,SD DAT),例如是SD DAT 0~3,其包括4 个位,用以传收第二接口112与记忆卡接口101之间的数据。该第二接口112 的控制接口112a以及传收接口112b分别用以转换该主机系统接口102的该第一子接口102a以及第二子接口102b与该第一通讯协议之间的通讯以及数据传输格式。在一实施例中,该第二选择器114例如多任务器,但不限于此,例如以电路组件或是逻辑组件组合而成的选择器。在一实施例中,第二接口112例如是SD-UHS I的主控制器。

如图1所示,在一实施例中,该读写控制系统用以控制一记忆卡100的数据之读写,该读写控制系统包括第一传输路径P1、第二传输路径P2、第三传输路径P3以及第四传输路径P4。该第一传输路径P1连接于一记忆卡接口101、一桥接装置109以及一主机系统接口102之间,其中该记忆卡接口101用以连接该记忆卡100。该第二传输路径P2连接于该记忆卡接口101、一第二选择器 114、该桥接装置109、一第一选择器108以及该主机系统接口102之间。该第三传输路径P3连接于该记忆卡接口101、该第二选择器114以及该主机系统接口102之间。该第四传输路径P4连接于该记忆卡接口101、该第一选择器108 以及该主机系统接口102之间。其中,当该记忆卡100以该第一通讯协议运作时,该主机系统103透过该第一传输路径P1以与该记忆卡接口101通讯并且透过该第二传输路径P2以该第一通讯协议读写该记忆卡100的该数据。其中,当该记忆卡100以该第二通讯协议运作时,该主机系统103透过该第三传输路径 P3以与该记忆卡接口101通讯并且透过该第四传输路径P4以该第二通讯协议读写该记忆卡100的该数据。

第2图系绘示依据本发明第二实施例中读写控制系统之方块图,第2图的读写控制系统类似于第1图的读写控制系统,其差异在于第二接口112与第一接口110之间还设置一非挥发性内存快捷(NVMe)协议控制器200。当该主机系统103确认该记忆卡100支持该第一通讯协议,例如是支持该主机系统接口102 的PCIe1.0协议版本或是PCIe2.0协议版本,该主机系统103经该主机系统接口 102透过该第一选择器108的该第一传收端FT经由第一接口110、NVMe控制器200以及第二接口112读写该记忆卡100的该数据。当该主机系统接口102确认该记忆卡100支持该第二通讯协议,例如是支持该主机系统接口102的 PCIe3.0协议版本,该主机系统103内的一非挥发性内存快捷(NVMe)协议驱动程序可透过该第一选择器108的该第二传收端ST读写该记忆卡100的该数据。

根据上述,本发明之读写控制系统,藉由控制装置104的控制模块106以及第一选择器108,使主机系统103只需透过一个接口,即可支持不同的通讯协议读写记忆卡100的数据,解决记忆卡100与读写控制系统之间兼容性的问题,并且提高记忆卡100的使用弹性,同时降低读写控制系统的生产成本。

参考第1图以及第3图,第3图系绘示依据本发明第一实施例中读写控制方法之流程图。该读写控制方法用于一读写控制系统,以供主机系统103透过该读写控制系统读写记忆卡100。该读写控制系统包括一记忆卡接口101、一主机系统接口102以及一控制装置104,该控制装置104包括一控制模块106以及一第一选择器108,该控制模块106包括一第一接口110、一第二接口112 以及第二选择器114,该主机系统接口102包括一第一子接口102a以及一第二子接口102b,该第一选择器108包括第一传收端FT以及第二传收端ST,该读写控制方法包括下列步骤:

在步骤S300中,该主机系统103经该主机系统接口102以第一触发信号 TS1触发该第一选择器108的第一传收端FT,该主机系统103经由该主机系统接口102、该第一选择器108的该第一传收端FT以及该控制模块106电性连接该记忆卡接口101。

在步骤S302中,侦测出该记忆卡100连接于该主机系统接口102以及该控制装置104。在一实施例中,该主机系统103是以一第一通讯协议与该记忆卡100连接。

在步骤S304中,判断该记忆卡100是否支持一第二通讯协议的运作。

在步骤S306中,当判断该记忆卡100不支持该第二通讯协议的运作时(即,该记忆卡100以该第一通讯协议运作),该记忆卡接口101经该第二选择器114、该桥接装置109以及该第一选择器108来与该主机系统接口102电性连接,使该主机系统103透过该主机系统接口102以该第一通讯协议读写该记忆卡100 的该数据。

在步骤S308中,当判断该记忆卡100支持该第二通讯协议运作时,该记忆卡接口101经该第二选择器114来与该主机系统接口102电性连接,该记忆卡接口101亦经该第一选择器108来与该主机系统接口102电性连接,并且该主机系统103透过该主机系统接口102、该控制装置104的该第一选择器108 的该第二传收端ST,以该第二通讯协议读写该记忆卡100的该数据。

参考第1图以及第4图,第4图系绘示依据本发明第二实施例中读写控制方法之流程图。用于读写控制系统,该读写控制系统包括一记忆卡接口101、一主机系统接口102以及一控制装置104,该控制装置104包括一控制模块106 以及一第一选择器108,该控制模块106包括一第一接口110、一第二接口112 以及第二选择器114,该主机系统接口102包括一第一子接口102a以及一第二子接口102b,该第一选择器108包括第一传收端FT以及第二传收端ST,该读写控制方法包括下列步骤:

在步骤S400中,主机系统103透过该主机系统接口102以第一触发信号 TS1触发该第一选择器108的第一传收端FT,该主机系统接口102经由该第一选择器108的该第一传收端FT以及该控制模块106电性连接该记忆卡接口101。

在步骤S402中,侦测该记忆卡100电性连接该记忆卡接口101。其中,本实施例例如是以该第一通讯协议与该记忆卡100进行连接。在一较佳实施例中,该控制装置104侦测出该记忆卡100电性连接该记忆卡接口101。该控制装置 104例如可将侦测讯息传送至该主机系统103。凡具有侦测出该记忆卡100电性连接该记忆卡接口101的动作皆属本揭露的精神与范畴,本文在此不作任何限制。

在步骤S404中,该第二接口112产生第二触发信号TS2以触发该第二选择器114。

在步骤S406中,以该第一通讯协议初始化或启动(Initialization process)该记忆卡100。在一实施例中,该主机系统103例如可透过该控制模块106的桥接装置109之第一接口110以及第二接口112,以该第一通讯协议来初始化或启动该记忆卡100。在其他实施例中,该控制模块106亦可透过桥接装置109 之第一接口110以及第二接口112,以该第一通讯协议来对该记忆卡100初始化或启动。凡以该第一通讯协议初始化或启动该记忆卡100的动作皆属本揭露的精神与范畴,本文在此不作任何限制。

在步骤S408中,判断该记忆卡100是否支持该第二通讯协议的运作。在一实施例中,该主机系统103可经该主机系统接口102以透过该第一选择器108 的该第一传收端FT,以判断该记忆卡100是否支持该第二通讯协议的运作。在其他实施例中,例如可由控制模块106来判断该记忆卡100是否支持该第二通讯协议的运作。凡判断该记忆卡100是否支持该第二通讯协议的运作的技术皆属本揭露的精神与范畴,本文在此不作任何限制。值得一提的是,当判断该记忆卡100支持该第二通讯协议运作之后,亦例如会再以该第二通讯协议初始化或启动(Initialization process)该记忆卡。

在步骤S410中,当判断该记忆卡100支持该第二通讯协议运作时,该第二接口112以该第二触发信号TS2触发该第二选择器114,以让该记忆卡接口101 透过该第二选择器114电性连接该主机系统接口102的该第一子接口102a,在一实施例中,该第一子接口102a例如是支持PCIe3.0协议版本。

在步骤S412中,当该记忆卡100以该第二通讯协议运作时,该主机系统接口102以该第一触发信号TS1触发该第一选择器108该第二传收端ST,以让该记忆卡接口101透该第二传收端ST电性连接该主机系统接口102的该第二子接口102b,在一实施例中,该第二子接口102b例如是支持PCIe3.0协议版本。

在步骤S414中,当该记忆卡100以该第二通讯协议运作时,该主机系统接口102断开该第一选择器108的该第一传收端FT,该第一传收端FT例如是支持PCIe1.0以及PCIe2.0协议版本。

在步骤S416中,该主机系统接口102透过该第一选择器108的该第二传收端ST以及该第二选择器114的控制接口112a与该记忆卡100通讯,以判断该记忆卡100是否支持该主机系统103的协议版本,该协议版本包括PCIe1.0、 PCIe2.0以及PCIe3.0协议版本。

在步骤S408之后,若判断该记忆卡100不支持该第二通讯协议的运作,即进行步骤S418。亦即,在步骤S418中,该主机系统103经该主机系统接口 102确认该记忆卡100的该第一通讯协议支持该主机系统接口102的PCIe1.0 协议版本或是PCIe2.0协议版本,该主机系统接口102透过该第一选择器108 的该第一传收端FT读写该记忆卡100的该数据。

承上,在步骤S416时,若判断该记忆卡100支持PCIe1.0、PCIe2.0协议版本,则进行步骤S418。相对地,若判断该记忆卡100支持PCIe3.0协议版本,则进行步骤S420。在步骤S420中,当该主机系统接口102确认该记忆卡100 的该第二通讯协议支持该主机系统接口102的PCIe3.0协议版本,该主机系统103经该主机系统接口102透过该第一选择器108的该第二传收端ST读写该记忆卡100的该数据。

在一较佳实施例中,于执行步骤414之后,亦可直接执行步骤S420,以让该主机系统接口102透过该第一选择器108的该第二传收端ST读写该记忆卡 100的该数据。

综上所述,本发明之读写控制系统及其方法,藉由控制装置的控制模块以及第一选择器,使主机系统只需透过一个接口,即可以不同的通讯协议读写记忆卡的数据,解决记忆卡与读写控制系统之间兼容性的问题,并且提高记忆卡的使用弹性,同时降低读写控制系统的生产成本。

虽然本申请已以优选实施例揭露如上,但上述优选实施例并非用以限制本申请,本领域的普通技术人员,在不脱离本申请的精神和范围内,均可作各种更动与润饰,因此本申请的保护范围以权利要求界定的范围为准。

- 记忆卡的读写控制系统及其方法

- 记忆卡的读写控制系统