一种半导体制造方法

文献发布时间:2023-06-19 11:27:38

技术领域

本发明涉及半导体零部件以及芯片领域,特别是涉及一种在单次半导体外延沉积过程中在同一平面内生长不同层厚度量子阱的半导体制造方法。

背景技术

在光电半导体集成结构中,光模必须能够沿着水平面波导以最小的损耗从一个部分传播到另一属性不同的部分。一般外延能够以多次生长完成平面上不同属性部分但成本高,不同属性的波导高度需要严格控制。能够以单个外延生长来生长具有多个不同属性部分的截面的技术,对于降低成本和复杂性是有益的,需要对此进行开发和研究。

诸如所谓的选择性区域生长(Selective Area Growth, SAG)之类的现有技术涉及绝缘膜掩模,该绝缘膜掩模图案充当用于修改预定区域中的层生长速率的掩模。该技术首先在半导体衬底上形成介电绝缘膜,对其进行光刻形成掩模构图,然后使用MOCVD外延生长法(生长半导体材料。在绝缘膜掩模的顶部上不会发生半导体材料的沉积。与周边没有介绝缘膜掩模的区域相比,绝缘膜掩模之间的间隙内部的增长率得到了改善。

如图1所示,为现有技术美国专利5543353中详细概述了的现有技术方案的结构示意图,US5543353A公开了制造半导体光子集成电路的方法,半导体光子集成电路包括第一和第二光电子器件,第一和第二光电子器件在单个半导体衬底上彼此光学连接并且通过选择性区域生长工艺形成,选择性区域生长工艺包括生长构成第一和第二光电子器件的化合物半导体层的步骤,第一光子器件使用一组绝缘膜掩模在半导体衬底上的特定区域中形成,绝缘膜掩模之间具有开放空间宽度,开放空间宽度范围为第III族物种蒸汽扩散长度的1.0到0.125倍,掩模与第一光子器件的光轴平行布置,每个掩模的宽度与光轴垂直,范围为16到800μm,第二光电子器件在不使用绝缘膜掩模的情况下形成。以美国专利5543353为例,与未通过任何掩模图案进行改性的区域相比,改性生长的区域较小。与未修改的区域相比,该技术始终导致修改后的正速率增长,即修改区域中的外延层比未修改的区域厚(图1)。当集成结构需要在关键应用中使用这些小区域时,必须仔细表征这些区域的属性,例如光致发光(Photoluminescence,PL)和晶格匹配。表征PL和晶格匹配的大多数设备都只能读取大面积的数据,读不到较小尺寸的修改区域,所以难以采用必要的精度直接表征;此外,如果采用小区域表征设备,设备成本非常昂贵。

此外,集成结构的示例是具有无源光束形成部分(Beam Forming Section BFS)的激光器。 这种集成结构的关键组件是激光器,在制造中需要直接监视和表征这部分的外延层。 但是,使用SAG技术,必须在未修饰的外延区域形成BFS,而必须在修饰的外延区域形成激光。 因此,难以通过SAG技术监视和表征用于激光组件的材料。

发明内容

本发明的目的在于提供一种半导体制造方法,用于在单个半导体外延沉积过程中在同一平面内生长不同层厚度量子阱,发明构思在于采用选择性耗尽外延 (SelectiveDepletion Epitaxy SDE) 的方法,包括如下步骤:

步骤1,进行第一次层外延,生长基本的外延层结构,所述基本的外延层结构包括衬底(1)、一个牺牲层(2)和一个桥接层(3),所述牺牲层(2)位于所述衬底(1)和所述桥接层(3)之间;

步骤2,通过光刻和蚀刻形成桥图案,并形成带有图案化桥头悬垂的晶片;

步骤3,将步骤2处理后的晶片进行清洗;

步骤4,将清洗后带有图案化桥头悬垂的晶片送回外延设备进行第二次层外延;

步骤5,在第二次层外延后,选择性去除高架桥结构(4),从而形成不同区域中具有不同厚度外延层的晶片。

优选的,所述步骤1通过金属有机化学气相沉积(MOCVD)方式进行。

优选的,所述步骤1的所述衬底的材料为InP、GaAs,GaN或InAs或其他半导体单晶材料。

优选的,所述牺牲层(2)和所述桥接层(3)具有与所述衬底(1)的材料的晶格完全匹配或与晶格大致匹配的成分,当所述衬底(1)材料为InP的情况下,所述牺牲层(2)材料为InGaAs,所述桥接层(3)材料为InP。

优选的,所述步骤2采用选择性耗尽外延实施,从而在需要修改的区域上形成所述桥图案。

优选的,所述步骤2包括:

步骤21,在图案外蚀刻穿过桥接层(3);

步骤22,使用选择性蚀刻去除牺牲层(2),但保留了图案内的桥接层部分,从而使得桥悬置于要修改的区域上。

优选的,所述桥图案包括支撑结构(5)、高架桥结构(4)以及附着在支撑结构(5)上的侧梁(6),其中所述支撑结构(5)大于高架桥结构(4)的宽度和侧梁(6)宽度。

优选的,所述步骤4所述第二次层外延生长期间,将层沉积在晶片上,所述高架桥结构下方的区域被修改为负增长率,形成比高架桥结构外的区域厚度更小的层。

本发明的目的还在于提供一种在单个半导体外延沉积过程中在同一平面内生长不同层厚度量子阱的激光器集成结构制造方法,在步骤1-5实施后,还包括:

步骤6,进行第三次外延生长,形成电接触后完成激光器集成器件的制备;或者为了形成分布反馈(DFB)激光器,在第三次外延生长一层光栅层,然后采用全息曝光或电子束形成光栅后,再进行第四次外延形成电接触后完成激光器集成器件的制备;

步骤7,通过标准处理形成二维光导结构,所述二维光导结构包括具有电触点的激光器(14)和波束形成部分(13),所述激光器(14)和所述波束形成部分(13)组合形成所述激光器集成结构。

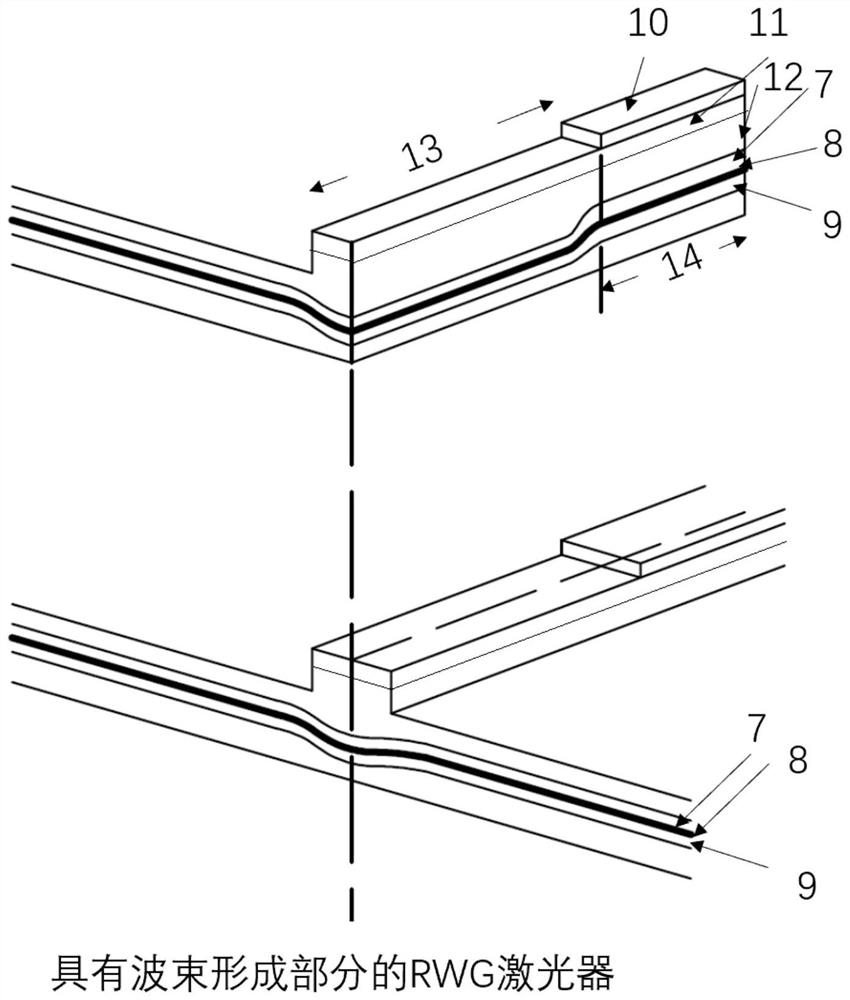

本发明的目的还在于提供一种在单个半导体外延沉积过程中在同一平面内生长不同层厚度量子阱的激光器集成结构,所述激光器集成结构包括分别形成在不同区域中的激光器(14)以及波束形成部分(13),所述激光器(14)形成在未改性外延的高架桥结构(4)以外的区域中,所述波束形成部分(13)形成在高架桥结构(4)的下方改性外延的区域中,所述波束形成部分(13)为有源波导,所述激光器(14)上部和下部具有上部SCH(SeparateConfinement Heterostructure,分离限制异质层结构)(7)和下部分离限制异质层结构(9)从而形成两层SCH(Separate Confinement Heterostructure 分离限制异质层结构)层,两层SCH层之间形成多量子阱MQW(Multiple Quantum Wells)(8),所述激光器(14)上方设置P+-InGaAs接触层(11)与InP过渡层(12),所述P+-InGaAs接触层(11)上方设置接触金属层(10)。

本发明的有益效果:

(1)当该光学模式通过波束形成部分离开集成设备时,与没有波束形成部分的简单激光设备相比,所得的远场图案更窄。

(2)对于将设备光耦合到光纤中是有利的,当外延层足够薄以表现出量子尺寸效应时,由于形成的量子阱比激光部分窄并且因此具有更高的带隙,波束形成部分也变得不吸收激光部分所发出的光。由于波束形成部分对激光学模式具有低损耗,并且出光镜面也是非吸收性的,因此有利于器件的可靠性。

根据下文结合附图对本发明具体实施例的详细描述,本领域技术人员将会更加明了本发明的上述以及其他目的、优点和特征。

附图说明

后文将参照附图以示例性而非限制性的方式详细描述本发明的一些具体实施例。附图中相同的附图标记标示了相同或类似的部件或部分。本领域技术人员应该理解,这些附图未必是按比例绘制的。本发明的目标及特征考虑到如下结合附图的描述将更加明显,附图中:

附图1为根据现有技术的制造半导体光子集成电路的方法;

附图2为根据本发明实施例的通过MOCVD方式实施第一次层外延结构示意图;

附图3为根据本发明实施例的通过光刻和蚀刻形成桥图案的结构示意图;

附图4(a)为根据本发明实施例的通过光刻和蚀刻形成桥后MOCVD所长出的外延层A-A截面结构示意图;

附图4(b)为根据本发明实施例的通过光刻和蚀刻形成桥后MOCVD所长出的外延层B-B截面结构示意图;

附图4(c)为根据本发明实施例的通过光刻和蚀刻形成桥后MOCVD所长出的外延层C-C截面结构示意图;

附图5为根据本发明实施例的具有波束形成部分波导的RWG(Ridge Waveguide)激光器。

具体实施方式

本实施例提供一种在单个半导体外延沉积过程中在同一平面内生长不同层厚度量子阱的半导体制造方法,首先在需要修改的区域上形成高架桥结构,如图3所示。由于减少了在桥结构下方的气体源扩散,桥下的外延层比桥结构外的外延层薄。 因此,与未修改区域相比,此技术导致修改区域的层外延速率为负,如图4(a)-(c)所示,发明人将此项技术成为选择性耗尽外延(Selective Depletion Epitaxy SDE)。

本实施例涉及一种在单个半导体外延沉积过程中在同一平面内生长不同层厚度量子阱的晶片制造方法,包括如下步骤:

步骤1,参见图2,通过MOCVD(metal-organic chemical vapor deposition,金属有机化学气相沉积)方式实施第一次层外延,从而生长基本的外延层结构,基本的外延层结构由衬底1、一个牺牲层2和一个桥接层3组成,牺牲层2位于衬底1和桥接层3之间。其中,衬底1材料的示例可以是InP。根据应用和激光发射波长,衬底1材料可以是GaAs,GaN,InAs或其他类似材料。牺牲层2和桥接层3具有与衬底1材料的晶格完全匹配或与晶格大致匹配的成分。

作为优选实施方式,所选择牺牲层2材料和桥接层3材料使得存在选择性优于另一种的选择性化学蚀刻剂。在该示例中,衬底1材料是InP,牺牲层2材料可以是InGaAs,桥接层3材料可以是InP或满足上述条件的其他组合。

步骤2,通过光刻和蚀刻形成桥图案,并形成带有图案化桥头悬垂的晶片;其中光刻和蚀刻过程包括两个步骤:步骤21,在图案外蚀刻穿过桥接层3;步骤22,使用选择性蚀刻去除牺牲层2,但保留了图案内的桥接层3部分,从而使得桥悬置于要修改的区域上。

如图3所示,首先在需要修改的区域上形成高架桥结构4。高架桥与桥下晶圆表面最佳距离为2-6um,但其他尺寸也可以,桥结构最佳宽度为2-10um但其他尺寸也可以。桥结构的长度随设计集成结构需求而定。桥结构的宽度也可以顺着轴方向有所变化导致波导与量子阱的厚度变化。为了保持桥接层处桥梁悬空,桥梁的结构包括支撑结构5、高架桥结构4以及附着在支撑结构5上的侧梁6。侧梁6可以不止一个,也可以置于高架桥的一侧或两侧。支撑结构5大于高架桥4结构的宽度和侧梁6宽度,因此某些牺牲层2在第二次蚀刻过程中并未完全去除。参见图4,由于减少了在桥结构下方的气体源扩散,桥下的外延层比桥结构外的外延层薄。 因此,与未修改区域相比,SDE技术导致修改区域的层外延速率为负。

步骤3,将步骤2处理后的晶片进行清洗;

步骤4,将清洗后带有图案化桥头悬垂的晶片送回MOCVD设备进行第二次层外延。第二次层外延生长期间,将层沉积在晶片上。高架桥结构下方的区域被修改为负增长率,因此与高架桥结构外的区域相比所形成的层更薄。

步骤5,在第二次层外延后,选择性去除部分高架桥结构4,从而形成不同区域中具有不同厚度外延层的晶片。

本实施例根据上述方法提供一种在单个半导体外延沉积过程中在同一平面内生长不同层厚度量子阱的激光器集成结构制造方法,在步骤1-5实施后,还包括:

步骤6,进行第三次外延生长,形成电接触后完成激光器集成器件的制备;或者为了形成DFB(distributed feedback)激光器,在第三次外延生长一层光栅层,然后采用全息曝光或电子束形成光栅后,再进行第四次外延形成电接触后完成激光器集成器件的制备;

步骤7,此后,标准处理可以形成二维光导结构。进一步的处理可以形成具有电触点的激光器14和波束形成部分13。

本实施例使用步骤1-7构成的完整的制备方法制备一种在单个半导体外延沉积过程中在同一平面内生长不同层厚度量子阱的激光器集成结构,本实施例是RWG(RidgeWaveguide)结构,参见图5,激光器集成结构包括分别形成在不同区域中的激光器14以及波束形成部分13,其发明构思在于将在单个半导体外延沉积过程中在同一平面内生长不同层厚度量子阱的技术应用于具有无源波束形成部分(BFS)的激光器的集成结构的示例中,激光器14形成在未改性外延的高架桥结构4以外的区域中,波束形成部分13形成在高架桥结构4下方改性外延的区域中。由于未修饰外延的面积比修饰外延的面积大得多,因此使用本发明的技术很容易监控和表征激光切片的材料,譬如用XRD测外延层的晶格匹配,PL测外延层的光谱。波束形成部分13为无源波导。激光器14上部和下部具有上层分离限制异质层结构7和下层分离限制异质层结构9,从而形成两层分离限制异质层结构层,两层分离限制异质层结构层之间形成多量子阱8,即MQW,Multiple Quantum Wells。激光器14上方设置P+-InGaAs接触层11与InP过渡层12,P+-InGaAs接触层11上方设置接触金属层10。

在RWG的实施例中,波束形成部分13具有较薄的层,因此激光光学模式占用较大的横截面面积。这部分可作为无源波导。对本领域技术人员,即熟悉工艺的技术人员可以熟知该技术也可以实施为其他实施例,譬如BH (Buried Heterostructure).

当该光学模式通过波束形成部分离开集成设备时,与没有波束形成部分的简单激光设备相比,所得的远场图案更窄。这对于将设备光耦合到光纤中是有利的。当外延层足够薄以表现出量子尺寸效应时,由于形成的量子阱比激光部分窄并且因此具有更高的带隙,因此波束形成部分也变得不吸收激光部分所发出的光。这很重要,因为波束形成部分对激光学模式具有低损耗。出光镜面也是非吸收性的,有利于器件的可靠性。

虽然本发明已经参考特定的说明性实施例进行了描述,但是不会受到这些实施例的限定而仅仅受到附加权利要求的限定。本领域技术人员应当理解可以在不偏离本发明的保护范围和精神的情况下对本发明的实施例能够进行改动和修改。

- 半导体光发射装置的制造方法、半导体光发射装置、半导体装置的制造方法、半导体装置、一种装置的制造方法、以及一种装置

- 半导体用膜组合物、半导体用膜组合物的制造方法、半导体用构件的制造方法、半导体用加工材料的制造方法以及半导体装置