基于峰保持方法的能量测量装置

文献发布时间:2023-06-19 11:35:49

技术领域

本发明属于信号能量测量技术领域,具体涉及基于峰保持方法的能量测量装置。

背景技术

目前,能量测量方法分为很多种,例如基于中高速模数转换器(Analog DigitalConverter,ADC)芯片的数字积分方法,基于脉宽测量的过阈时间甄别(Time overthreshold,TOT)技术等。其中,峰保持(Peak Hold)电路由于其简易的结构和较高的精度,目前广泛应用在电信号能量测量装置中,例如CT、PET系统等。

目前市面上主流的能量测量技术是基于商用中高速ADC芯片将模拟电信号进行模数变换,然后将得到的数字化信息送入FPGA芯片通过积分算法实现能量测量。但该方案存在的问题是,由于PET探测器通道数很多,需要使用较多数量的商用中高速ADC芯片实现,这会提高系统成本和带来较大功耗,严重限制电子学系统集成度。

此外,有的还使用TOT技术实现能量测量,但是其动态范围和线性较差;

另外,有的还采用峰保持方案,使用ASIC和商用ADC芯片完成,但是存在成本高且配置不灵活的问题。

因此,设计一种适合多通道能量测量,结构简单,测量精度高以及成本低的能量测量装置就显得十分必要。

为了提高系统的能量测量精度,本发明使用模拟峰保持电路将输入的脉冲电流信号转换为幅度与信号能量成正比的直流电平,然后利用FPGA-ADC完成高精度能量测量。本发明具有结构简单,测量精度高以及成本低的优点,非常适合多通道能量测量的应用场合。

例如,申请号为CN201810481263.7的中国发明专利所述的一种基于FPGA的超高通过率电流型数字化脉冲处理方法,前级经过超高速的电流前置放大器将探测器微弱电流信号放大后传入数字电路部分,进入FPGA后在快通道经过数字高通滤波器提取得到触发信号,在慢通道收到触发信号的同时开始对原始电流信号开始积分得到脉冲信号的原始能量幅度信息。虽然通过复合电流前置放大电路进行电流放大,能极好的保留原始的脉冲信息,解决了1GSPS剂量率的粒子信号的单个粒子信号能量与时间等脉冲信息的测量,通过并行处理的模式可将常规高速数字多道分析能力进步提高数倍,可达到1GHz的脉冲计数通过率,但是其缺点在于输入的脉冲信号的能量信息需要经过多个步骤才能转换为直流电平,处理效率低,且整体方法所需要的硬件环节较多,成本较高,不利于广泛应用。

发明内容

本发明是为了克服现有技术中,现有的能量测量技术存在系统成本高,功耗大,动态范围和线性差以及配置不灵活的问题,提供了一种适合多通道能量测量,结构简单,测量精度高以及成本低的基于峰保持方法的能量测量装置。

为了达到上述发明目的,本发明采用以下技术方案:

基于峰保持方法的能量测量装置,包括峰保持电路、FPGA-ADC电路和电荷泄放电路;所述峰保持电路用于将输入的脉冲信号能量转换为直流电压,所述峰保持电路与FPGA-ADC电路电连接;所述FPGA-ADC电路用于实现信号的模数转换和能量测量,所述FPGA-ADC电路与电荷泄放电路电连接;所述电荷泄放电路用于能量测量后,使电荷快速泄放并等待下一次测量,所述电荷快速泄放与峰保持电路电连接。

作为优选,所述峰保持电路包括运算放大器A1、保持电容C

作为优选,所述FPGA-ADC电路包括FPGA芯片和电阻Rs;所述电阻Rs与FPGA芯片电连接;所述运算放大器A1的输出端与FPGA芯片电连接。

作为优选,所述电荷泄放电路包括开关SW、电阻R1和电阻R2;所述开关SW与FPGA芯片电连接;所述电阻R1的一端与开关SW电连接,所述电阻R1的另一端分别与保持电容C

作为优选,所述FPGA芯片内部包括时钟发生器、内部比较器和进位链TDC结构;所述时钟发生器的信号输出接口与电阻Rs的一端电连接,所述电阻Rs的另一端与内部比较器的负输入接口电连接;所述内部比较器的输出端与进位链TDC结构电连接;所述内部比较器的正输入接口与运算放大器A1的输出端电连接。

作为优选,所述时钟发生器采用锁相环结构。

作为优选,所述FPGA芯片内部还包括寄生电容Cp。

作为优选,所述寄生电容Cp和电阻Rs构成低通滤波电路。

本发明与现有技术相比,有益效果是:(1)本发明利用运算放大器、保持电容和电阻组成的峰保持电路,能够将输入的脉冲信号能量直接转换为直流电压;(2)本发明利用一个片外电阻,实现FPGA-ADC功能,能够对直流电压的模数进行变换;(3)利用FPGA芯片的三态门和时序控制逻辑,在模数转换结束后,快速释放保持电容上的电荷,实现低死时间的测量;(4)本发明整体具有结构简单,成本低和精度高的优点。

附图说明

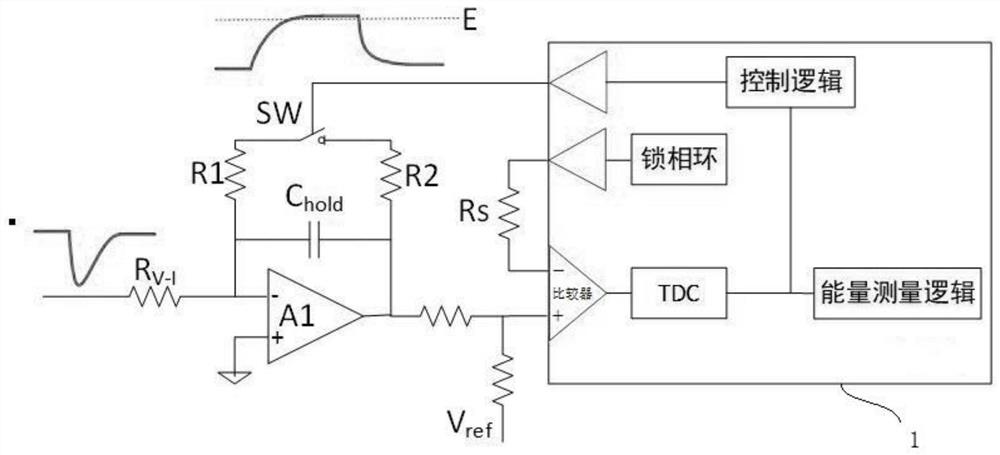

图1为本发明基于峰保持方法的能量测量装置的一种原理框图;

图2为本发明中FPGA-ADC电路进行测量的一种原理示意图;

图3为本发明中进位链TDC结构的一种结构示意图;

图4为本发明基于峰保持方法的能量测量装置进行能量测量的一种流程图;

图5为本发明基于峰保持方法的能量测量装置的一种仿真效果图;

图6为图5对应的一种输入-输出转换曲线仿真结果图。

图中:FPGA芯片1。

具体实施方式

为了更清楚地说明本发明实施例,下面将对照附图说明本发明的具体实施方式。显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图,并获得其他的实施方式。

实施例1:

如图1所示的基于峰保持方法的能量测量装置,包括峰保持电路、FPGA-ADC电路和电荷泄放电路;所述峰保持电路用于将输入的脉冲信号能量转换为直流电压,所述峰保持电路与FPGA-ADC电路电连接;所述FPGA-ADC电路用于实现信号的模数转换和能量测量,所述FPGA-ADC电路与电荷泄放电路电连接;所述电荷泄放电路用于能量测量后,使电荷快速泄放并等待下一次测量,所述电荷快速泄放与峰保持电路电连接。

进一步的,所述峰保持电路包括运算放大器A1、保持电容C

进一步的,所述FPGA-ADC电路包括FPGA芯片1和电阻Rs;所述电阻Rs与FPGA芯片电连接;所述运算放大器A1的输出端与FPGA芯片电连接。

进一步的,所述FPGA芯片内部包括时钟发生器、内部比较器和进位链TDC结构;所述时钟发生器的信号输出接口与电阻Rs的一端电连接,所述电阻Rs的另一端与内部比较器的负输入接口电连接;所述内部比较器的输出端与进位链TDC结构电连接;所述内部比较器的正输入接口与运算放大器A1的输出端电连接。所述内部比较器的正输入接口还外接基准电压V

进一步的,所述时钟发生器采用锁相环结构。

所述时钟发生器产生采样时钟,经过低通滤波电路后形成准三角波,与输入模拟信号通过FPGA芯片的内部比较器进行比较,得到待测脉冲。待测脉冲的脉宽与输入信号的能量相关,待测脉冲的宽度可近似与输入模拟信号的幅度成正比,测量待测脉冲的脉宽即可完成模数变换,反推输入信号的能量。脉宽测量基于进位链TDC结构完成,具体原理如图2所示。图2中,c指代的为输入模拟信号,a指代的为待测脉冲,b指代的为输入模拟信号的幅度。

为了提高时间测量动态范围,采用粗细时间相结合的时间内插方式。待测脉冲信号进入FPGA芯片内部进位链TDC结构,进位链TDC结构的进位单元包含抽头,每个抽头对应一个触发器单元。进位链TDC结构的抽头使用各自的触发器链锁存得到抽头状态电平。待测脉冲前后沿在不同时刻进位链抽头上的状态不同,通过编码电路对各抽头状态进行编码即可得到待测脉冲信号前后沿的细时间戳信息。本发明利用同一个进位链同时标记待测脉冲前后沿时间状态信息。利用粗时间计数器可以得到待测信号前后沿的粗时间戳信息,通过打包逻辑对粗细时间戳进行合并,即可获得待测信号前后沿的时间信息。后沿时间减去前沿时间即可得到脉冲信号宽度。另外,由于进位链各抽头之间延迟不均匀性,需要对延迟进行非线性修正。系统初始化时,脉冲信号生成器通过与系统时钟非同源时钟驱动产生大量待测脉冲信号并进行细时间测量,非线性修正电路根据统计各细时间的数量计算修正系数,并将修正系数作为查找表(Look up table,LUT)存放于FPGA芯片内部的随机存储器(Random access memory,RAM)中。进位链TDC结构具体如图3所示。

进一步的,如图3所示,所述FPGA芯片内部还包括寄生电容Cp。所述寄生电容Cp的一端分别与电阻Rs和内部比较器的负输入接口电连接,所述寄生电容Cp的另一端信号接地。

所述寄生电容Cp和电阻Rs构成低通滤波电路。

进一步的,所述电荷泄放电路包括开关SW、电阻R1和电阻R2;所述开关SW与FPGA芯片电连接;所述电阻R1的一端与开关SW电连接,所述电阻R1的另一端分别与保持电容C

所述电荷泄放电路用于在能量测量完毕后,通过FPGA芯片的IO控制开关SW,使保持电容C

当FPGA-ADC电路检测到输入电平形状,判断信号平顶出现后,将直流电平电压减去基线电平,得到最终的能量值,然后闭合开关SW。上述整个能量测量的过程流程图如图4所示。

进一步的,为了更好的说明本发明的技术效果,利用PSPICE软件对本发明装置中的电路进行仿真,瞬态波形如图5所示。仿真结果表明,本发明装置中的电路工作正常,可以将输入信号积分为直流电平,并且泄放过程正确。

调整输入信号幅度,然后画出输入-输出转换曲线,如图6所示。如图6所示的仿真结果表明,本发明装置中的电路工作线性良好,动态范围较大。

本发明利用运算放大器、保持电容和电阻组成的峰保持电路,能够将输入的脉冲信号能量直接转换为直流电压;本发明利用一个片外电阻,实现FPGA-ADC功能,能够对直流电压的模数进行变换;利用FPGA芯片的三态门和时序控制逻辑,在模数转换结束后,快速释放保持电容上的电荷,实现低死时间的测量。

本发明基于FPGA-ADC原理,使用运算放大器和电容器件组成简单的峰保持电路,将输入的脉冲信号的能量信息转换为直流电平,并利用FPGA芯片控制保持电容的充放电时序,完成能量测量。本发明硬件只需要一个普通运算放大器、一个开关和几个电阻、电容器件,以及FPGA芯片的三个IO管脚,具体的模数变换和测量均使用代码实现,本发明整体具有结构简单,成本低和精度高的优点。

以上所述仅是对本发明的优选实施例及原理进行了详细说明,对本领域的普通技术人员而言,依据本发明提供的思想,在具体实施方式上会有改变之处,而这些改变也应视为本发明的保护范围。

- 基于峰保持方法的能量测量装置

- 一种基于人体运动能量采集的心率测量装置及测量方法