半导体器件的制造方法

文献发布时间:2023-06-19 12:02:28

技术领域

本发明涉及集成电路制造技术领域,尤其涉及一种半导体器件的制造方法。

背景技术

屏蔽栅沟槽型功率器件(Shield Gate Trench,SGT)是一种典型的沟槽型MOSFET管,具有传统沟槽型MOSFET管导通损耗低的优点,应用广泛。

图1a-图1d为传统的SGT器件的制造方法中部分步骤对应的结构示意图。首先,参阅图1a,SGT器件的衬底100内形成有沟槽110,所述衬底100的表面和所述沟槽110的内壁形成有场氧化层111,衬底100表面和所述沟槽110侧壁上的场氧化层111上形成有研磨停止层112,所述研磨停止层112的表面及其两侧的场氧化层111上形成有第一介质层113,所述沟槽110内形成有屏蔽栅120。接着,参阅图1b,进行第一次湿法刻蚀工艺,刻蚀部分所述场氧化层111和部分所述第一介质层113,以暴露所述屏蔽栅120的部分侧壁。随后,参阅图1c,进行高密度等离子体化学气相沉积工艺(HDP),在所述沟槽110内填充第二介质层121并延伸覆盖所述沟槽110两侧的研磨停止层112和第一介质层113。参阅图1d,进行化学机械研磨工艺(CMP),以去除部分所述第二介质层121和所述研磨停止层112表面的第一介质层113,随后进行第二次湿法刻蚀工艺,刻蚀所述场氧化层111、所述研磨停止层112和部分所述第二介质层121以暴露所述衬底100。

然而,由于湿法刻蚀工艺具有各项同性的特点,因此,在第一次湿法刻蚀工艺中,所述衬底100和所述研磨停止层112之间的部分场氧化层111被刻蚀形成空洞(即图1b中A所表示的部分)。由于所述空洞位于研磨停止层112的下方,因此HDP工艺中形成的所述第二介质层121无法完全填满所述空洞。在第二次湿法刻蚀的过程中,所述空洞被腐蚀液腐蚀变大形成缺陷沟槽(即图1d中B所表示的部分)。

在后续的SGT器件的制造方法中,所述缺陷沟槽处容易出现多晶硅残留,从而影响所述SGT器件的形貌及性能。因此,需要一种方法解决上述问题。

发明内容

本发明的目的在于提供一种半导体器件的制造方法,刻蚀部分研磨停止层以暴露场氧化层中的空洞所在的区域,从而减少或避免所述空洞在后续工艺中对半导体器件的性能产生影响。

为了达到上述目的,本发明提供了一种半导体器件的制造方法,包括:

提供衬底,所述衬底内形成有沟槽,所述衬底的表面和所述沟槽的侧壁及底部依次形成有场氧化层和第一介质层,所述衬底的表面的所述场氧化层和所述第一介质层之间形成有研磨停止层,所述沟槽内形成有屏蔽栅;

采用湿法刻蚀工艺去除部分所述场氧化层和部分所述第一介质层,以暴露所述屏蔽栅的上表面及部分侧壁;以及,

去除部分所述研磨停止层,以暴露所述沟槽两侧的部分所述衬底的表面。

可选的,所述湿法刻蚀工艺中,所述场氧化层靠近所述沟槽的位置处形成有空洞。

可选的,刻蚀部分所述研磨停止层暴露出的所述衬底的表面至少覆盖所述空洞所在区域。

可选的,采用回刻工艺刻蚀去除部分所述研磨停止层。

可选的,所述回刻工艺的刻蚀剂为磷酸,所述刻蚀剂的浓度范围为80%~90%,工艺温度的范围为150℃~170℃,工艺时间的范围为30min~90min。

可选的,去除部分所述研磨停止层之后还包括:

在暴露的所述衬底的表面形成保护层,所述保护层延伸覆盖所述沟槽的侧壁上的所述场氧化层。

可选的,所述保护层的材料包括氧化硅、氮化硅或氮氧化硅。

可选的,形成所述保护层之后,还包括:

在所述沟槽内填充第二介质层并延伸覆盖所述沟槽两侧的所述保护层及所述第一介质层;

进行平坦化处理,去除所述衬底的表面的部分所述第二介质层和所述研磨停止层上的所述第一介质层;

进行湿法刻蚀工艺去除所述研磨停止层、所述场氧化层和部分所述第二介质层,以暴露所述沟槽两侧的衬底。

可选的,采用高密度等离子体化学气相沉积工艺形成所述第二介质层。

可选的,所述研磨停止层为氮化硅层。

可选的,所述半导体器件的制造方法用于制造SGT器件。

综上所述,本发明提供一种半导体器件的制造方法,包括:提供衬底,所述衬底内形成有沟槽,所述衬底的表面和所述沟槽的侧壁及底部依次形成有场氧化层和第一介质层,所述衬底的表面的所述场氧化层和所述第一介质层之间形成有研磨停止层,所述沟槽内形成有屏蔽栅;采用湿法刻蚀工艺去除部分场氧化层和部分所述第一介质层,以暴露屏蔽栅的上表面及部分侧壁;以及,去除部分所述研磨停止层,以暴露沟槽两侧的部分衬底的表面。本发明通过刻蚀部分研磨停止层暴露并消除湿法刻蚀场氧化层过程中形成的空洞,减少或避免空洞在后续工艺中对半导体器件的性能产生影响。此外,本发明在空洞所在区域的衬底表面及沟槽侧壁的部分场氧化层上形成保护层,避免衬底在后续工艺中受到损伤。

附图说明

图1a-图1d为一SGT器件的制造方法中部分步骤对应的结构示意图;

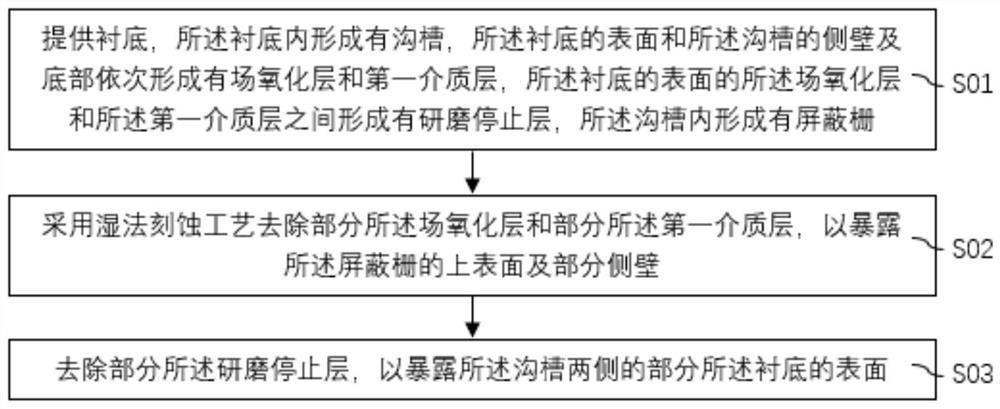

图2为本发明一实施例提供的半导体器件的制造方法的流程图;

图3-图9为本发明一实施例提供的半导体器件的制造方法中各个步骤对应的结构示意图;

其中,附图标记如下:

100-衬底;110-沟槽;111-场氧化层;112-研磨停止层;113-第一介质层;120-屏蔽栅;121-第二介质层;

200-衬底;210-沟槽;211-场氧化层;212-研磨停止层;213-第一介质层;220-屏蔽栅;221-保护层;222-第二介质层。

具体实施方式

下面将结合示意图对本发明的具体实施方式进行更详细的描述。根据下列描述,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

图2为本发明一实施例提供的半导体器件的制造方法的流程图。参阅图2,所述半导体器件的制造方法包括:

步骤S01:提供衬底,所述衬底内形成有沟槽,所述衬底的表面和所述沟槽的侧壁及底部依次形成有场氧化层和第一介质层,所述衬底的表面的所述场氧化层和所述第一介质层之间形成有研磨停止层,所述沟槽内形成有屏蔽栅;

步骤S02:采用湿法刻蚀工艺去除部分所述场氧化层和部分所述第一介质层,以暴露所述屏蔽栅的上表面及部分侧壁;以及,

步骤S03:去除部分所述研磨停止层,以暴露所述沟槽两侧的部分所述衬底的表面。

图3-图9为本实施例提供的半导体器件的制造方法中各个步骤对应的结构示意图。下面结合图3-图9详细说明本实施例提供的所述半导体器件的制造方法。

首先,参阅图3,执行步骤S01,提供衬底200,所述衬底200内形成有沟槽210,所述衬底200的表面和所述沟槽210的侧壁及底部依次形成有场氧化层211和第一介质层213,所述衬底200表面的所述场氧化层211和所述第一介质层213之间形成有研磨停止层212,所述沟槽210内的所述第一介质层213上形成有屏蔽栅220。具体的,形成所述屏蔽栅220的过程包括:在所述衬底200上形成图案化的光刻胶层(图中未示出),以所述图案化的光刻胶层为掩模层刻蚀所述衬底200,形成沟槽210;在所述衬底200的表面及所述沟槽210的侧壁及底部形成场氧化层211;在所述衬底200表面的场氧化层211上形成研磨停止层212;在所述场氧化层211和所述研磨停止层212上形成第一介质层213;在所述沟槽210内填充屏蔽栅材料层(图中未示出)并延伸覆盖所述沟槽210两侧的所述第一介质层213,刻蚀所述屏蔽栅材料层以形成屏蔽栅220。在本发明的其他实施例中,形成所述屏蔽栅220的工艺流程和工艺方法可以根据实际情况进行调整,本发明对此不作限制。

本实施例中,所述衬底200为硅衬底,在本发明的其他实施例中,所述衬底200所选用的材料可以是以下所提到的材料中的至少一种:Si、Ge、SiGe、SiC、SiGeC、InAs、GaAs、InP或者其它III/V化合物半导体,所述衬底200还可以是这些半导体材料构成的多层结构或者为绝缘体上硅(SOI)、绝缘体上层叠硅(SSOI)、绝缘体上层叠锗化硅(S-SiGeOI)、绝缘体上锗化硅(SiGeOI)以及绝缘体上锗(GeO)等,本发明对此不作限制。本实施例中,所述研磨停止层212为氮化硅层,所述场氧化层211为氧化硅层,所述第一介质层213为正硅酸乙酯(TEOS)层,在本发明的其他实施例中,所述场氧化层211、所述研磨停止层212和所述第一介质层213的材料可以根据实际需要进行调整。可选的,所述屏蔽栅220的材料包括多晶硅。

随后,参阅图3和图4,执行步骤S02,采用湿法刻蚀工艺去除部分所述场氧化层211和部分所述第一介质层213,以暴露所述屏蔽栅220的上表面及部分侧壁。由于所述研磨停止层212为氮化硅层,所述场氧化层211和所述第一介质层213均为氧化物层,因此,所述研磨停止层212的刻蚀速率小于所述场氧化层211和所述第一介质层213的刻蚀速率。由于湿法刻蚀工艺具有各向同性的特点,所述场氧化层211靠近所述沟槽210的位置处形成空洞(即图4中C所表示的部分),所述空洞位于所述研磨停止层212的下方,同时,所述沟槽210的顶部侧壁上的部分所述场氧化层211也被腐蚀,使得所述研磨停止层212凸出。本实施例中,所述空洞使得部分所述衬底200暴露在空气中,所述沟槽210的部分顶部侧壁也暴露在空气中,由于所述场氧化层211被刻蚀的情况与所述湿法刻蚀工艺的具体参数有关,在本发明的其他实施例中,所述场氧化层211被刻蚀后的形貌可能与本实施例所述的情况不同,本发明对此不作限制。

接着,参阅图5,执行步骤S03,去除部分研磨停止层212,以暴露所述沟槽210两侧的部分所述衬底200的表面。本实施例中,采用回刻(pull back)工艺刻蚀去除部分所述研磨停止层212,所述回刻工艺采用刻蚀剂漂洗所述半导体器件,使得所述研磨停止层212两侧的侧墙被刻蚀而回缩,从而使得两个沟槽210之间的所述研磨停止层212的宽度减小,从而暴露所述沟槽210两侧的部分所述衬底200的表面。可选的,所述回刻工艺的刻蚀剂为磷酸,所述刻蚀剂的浓度范围包括80%~90%,工艺温度的范围包括150℃~170℃,工艺时间的范围包括30min~90min。可选的,刻蚀部分所述研磨停止层212暴露出的所述衬底200的表面至少覆盖所述空洞所在区域。需要说明的是,在本发明的其他实施例中,可以刻蚀部分所述研磨停止层212直至暴露所述沟槽210两侧的部分所述衬底200的表面以及所述衬底200表面的部分所述场氧化层211,以确保所述空洞所在的区域完全暴露。

此外,参阅图6,在刻蚀部分所述研磨停止层212之后还包括,在暴露的所述衬底200的表面形成保护层221,所述保护层221延伸覆盖所述沟槽210的侧壁上的所述场氧化层211。制备所述保护层221的主要目的在于覆盖所述空洞所在区域暴露的部分所述衬底200及所述沟槽210的顶部侧壁,避免所述衬底200在后续工艺中受到损伤。本实施例中,所述保护层221为氧化硅层,在本发明的其他实施例中,所述保护层221的材料还包括氮化硅或氮氧化硅。

参阅图7-图9,在形成所述保护层221之后,本实施例所述的半导体器制造方法还包括:在所述沟槽210内填充第二介质层222并延伸覆盖所述沟槽210两侧的所述保护层221和所述第一介质层213;进行平坦化处理,去除所述衬底200的表面的部分所述第二介质层222和所述研磨停止层212上的所述第一介质层213;进行湿法刻蚀工艺去除所述研磨停止层212、所述场氧化层211和部分所述第二介质层222,以暴露所述沟槽210两侧的衬底200。参阅图7,本实施例中,采用高密度等离子体化学气相沉积工艺(HDP)形成所述第二介质层222,由于所述空洞所在区域被所述保护层221填满,因此,在形成所述第二介质层222的过程中,所述空洞所在区域暴露的部分所述衬底200不会受到损伤。参阅图9,由于所述空洞所在区域被所述保护层221填满,因此,所述场氧化层211在刻蚀的过程中不会形成缺陷沟槽(即图1d中B所表示的部分)。本实施例中,采用化学机械研磨工艺进行平坦化处理,在本发明的其他实施例中,可以采用其他方法进行平坦化处理,本发明对此不作限制。

对比图1d和图9可知,所述半导体器件的制造方法刻蚀部分研磨停止层以暴露场氧化层中的空洞所在的区域,并在所述空洞所在区域的衬底上及沟槽侧壁的部分场氧化层上形成了保护层,减少或避免所述空洞在后续工艺中扩大成沟槽缺陷,从而避免所述沟槽缺陷处出现多晶硅残留,进而确保半导体器件的稳定性。本实施例中,所述半导体器件的制造方法用于制造SGT器件,在本发明的其他实施例中,所述半导体器件的制造方法可以用于制造其他半导体器件。

综上,本发明提供一种半导体器件的制造方法,包括:提供衬底,所述衬底内形成有沟槽,所述衬底的表面和所述沟槽的侧壁及底部依次形成有场氧化层和第一介质层,所述衬底的表面的所述场氧化层和所述第一介质层之间形成有研磨停止层,所述沟槽内形成有屏蔽栅;采用湿法刻蚀工艺去除部分场氧化层和部分所述第一介质层,以暴露屏蔽栅的上表面及部分侧壁;以及,去除部分所述研磨停止层,以暴露沟槽两侧的部分衬底的表面。本发明通过刻蚀部分研磨停止层暴露并消除湿法刻蚀场氧化层过程中形成的空洞,减少或避免空洞在后续工艺中对半导体器件的性能产生影响。此外,本发明在空洞所在区域的衬底表面及沟槽侧壁的部分场氧化层上形成保护层,避免衬底在后续工艺中受到损伤。

上述仅为本发明的优选实施例而已,并不对本发明起到任何限制作用。任何所属技术领域的技术人员,在不脱离本发明的技术方案的范围内,对本发明揭露的技术方案和技术内容做任何形式的等同替换或修改等变动,均属未脱离本发明的技术方案的内容,仍属于本发明的保护范围之内。

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置

- 半导体器件的制造方法、半导体器件的制造装置、半导体器件、半导体器件的制造程序、半导体用处理剂以及转印用部件