半导体射频器件及其制备方法

文献发布时间:2023-06-19 19:27:02

技术领域

本申请涉及半导体技术领域,尤其是涉及一种半导体射频器件及其制备方法。

背景技术

传统的GaN HEMT射频器件为水平结构,通过栅极控制Al(Ga)N/GaN异质结界面中的二维电子气实现功率放大,通过设计T形结构的栅电极以减小栅电阻来提高器件工作频率。器件的工作频率越高,要求T形栅结构的栅足更窄,降低了栅极的机械稳定性,而且对加工设备的精度要求也越高,制造难度大。水平结构的器件,由于电流传输为水平方向,器件所占面积也会相对比较大。

发明内容

本申请的目的在于提供一种半导体射频器件及其制备方法,以缓解上述技术问题。

第一方面,本申请实施例提供一种半导体射频器件,半导体射频器件包括:从下到上依次设置的衬底、n型源极掺杂层;n型源极掺杂层上,设置有处于中间位置的脊形沟道结构、设置于脊形沟道结构一侧的第一异质结构层、以及设置于脊形沟道结构另一侧的第二异质结构层;脊形沟道结构上设置有漏电极;第一异质结构层上和第二异质结构层上均设置有栅介质和栅电极;衬底远离n型源极掺杂层一侧呈背孔结构,暴露出n型源极掺杂层;衬底的背孔结构中设置有源电极;第一异质结构层在脊形沟道结构的侧壁上具有二维电子气。

在本申请较佳的实施方式中,上述脊形沟道结构包括:设置于n型源极掺杂层上的非故意掺杂层和n型漏极掺杂层。

在本申请较佳的实施方式中,上述脊形沟道结构的侧壁所在平面与衬底的(0001)面平行。

在本申请较佳的实施方式中,上述栅电极与脊形沟道结构侧壁处的第一异质结构层和第二异质结构层形成肖特基接触。

在本申请较佳的实施方式中,上述肖特基接触位于远离漏电极靠近n型源极掺杂层一端。

在本申请较佳的实施方式中,上述第一异质结构层和第二异质结构层具有相同结构,由AlGaN、InAlN、AlN或者InAlGaN其中的一种与GaN组成。

在本申请较佳的实施方式中,上述衬底为具有非极性面表面的三族氮化物半导体。

在本申请较佳的实施方式中,上述衬底具有高电阻。

在本申请较佳的实施方式中,上述栅介质覆盖第一异质结构层和第二异质结构层的部分侧壁。

第二方面,本申请实施例还提供一种半导体射频器件的制备方法,方法包括:提供衬底;在衬底上依次生长n型源极掺杂层、非故意掺杂层、n型漏极掺杂层;刻蚀n型漏极掺杂层和非故意掺杂层,形成脊形沟道结构;在脊形沟道结构上形成覆盖于脊形沟道结构侧壁、脊形沟道结构中的n型漏极掺杂层、以及n型源极掺杂层上的异质结构层,且异质结构层在脊形沟道结构的一侧侧壁上形成二维电子气;在异质结构层上沉积绝缘介质层;刻蚀异质结构层侧壁上的部分绝缘介质层和脊形沟道结构中n型漏极掺杂层上的异质结构层,形成栅介质层;在栅介质层上沉积金属,形成栅电极,栅电极与脊形沟道结构侧壁上的第一异质结构层和第二异质结构层形成肖特基接触;在脊形沟道结构中的n型漏极掺杂层上沉积金属,形成漏电极;在衬底远离n型源极掺杂层一侧刻蚀出背孔结构,暴露出n型源极掺杂层;在背孔结构中沉积金属形成源电极。

本申请实施例提供的半导体射频器件及其制备方法中,半导体射频器件包括:从下到上依次设置的衬底、n型源极掺杂层;n型源极掺杂层上,设置有处于中间位置的脊形沟道结构、设置于脊形沟道结构一侧的第一异质结构层、以及设置于脊形沟道结构另一侧的第二异质结构层;脊形沟道结构上设置有漏电极;第一异质结构层上和第二异质结构层上均设置有栅介质和栅电极;衬底远离n型源极掺杂层一侧呈背孔结构,暴露出n型源极掺杂层;衬底的背孔结构中设置有源电极;第一异质结构层在脊形沟道结构的侧壁上具有二维电子气。本实施例中提供的半导体射频器件为垂直结构设计,相比水平结构可以有更高的器件密度,栅长及沟道尺寸可通过膜厚控制,对光刻设备的精度要求低,制造难度小。该器件中电流通过脊形沟道结构侧壁上形成的二维电子气传输,器件具有较小的沟道电阻;源电极和漏电极均制作在预先生长的n

附图说明

为了更清楚地说明本申请具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本申请的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1为现有技术中的一种半导体射频器件的示意图;

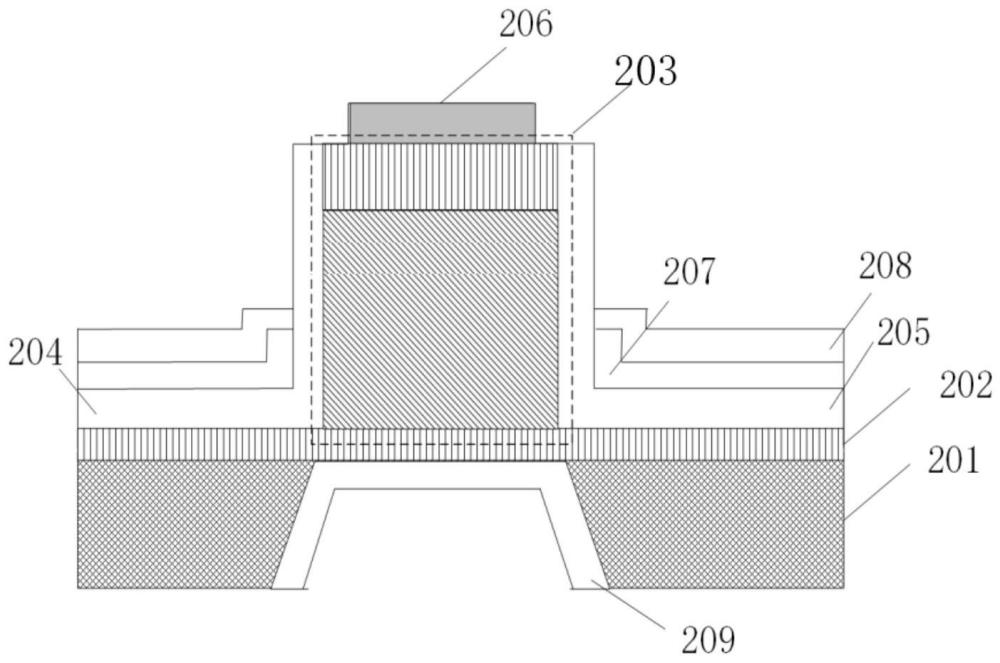

图2为本申请实施例提供的一种半导体射频器件的结构示意图;

图3为本申请实施例提供的另一种半导体射频器件的结构示意图;

图4为本申请实施例提供的一种半导体射频器件的传输特性和跨导特性曲线;

图5为本申请实施例提供的一种半导体射频器件的输出特性曲线;

图6为本申请实施例提供的一种半导体射频器件的制备方法的流程图;

图7为本申请实施例提供的一种半导体射频器件的制备过程示意图。

具体实施方式

下面将结合实施例对本申请的技术方案进行清楚、完整地描述,显然,所描述的实施例是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

参见图1所示,传统的GaN HEMT射频器件为水平结构,通过栅极控制Al(Ga)N/GaN异质结界面中的二维电子气实现功率放大。水平结构器件的制造需要对掺杂和器件尺寸进行精细控制。例如在图1所示的结构当中,为了提高器件工作频率,一方面栅极制作成下面窄(栅足)上面宽(栅帽)的T形结构,其栅足长度一般小于100nm,当频率更高(例如超过200GHz),栅足长度需要很短(比如30nm),因此对加工设备的精度要求很高,制造难度大;另一方面,为了减小源漏沟道间电阻,源漏间距往往需要微缩到1um以下,而为了减小源电极和漏电极的接触电阻,通常会在源、漏区域再生长一层重掺杂的n

水平结构需要对掺杂和器件尺寸进行精细控制,对加工设备的精度要求很高,制造难度大,其缺陷主要包括以下几个方面:

1)T形栅结构的制造需要高精度的光刻设备和光刻胶,而且当栅足很短时,会影响T形栅整体的机械稳定性,制造难度大;

2)电流传输为水平方向,器件面积比较大。

基于此,本申请实施例提供一种半导体射频器件及其制备方法,为便于对本实施例进行理解,首先对本申请实施例所公开的一种半导体射频器件进行详细介绍。

图2为本申请实施例提供的一种半导体射频器件,该半导体射频器件包括:从下到上依次设置的衬底201、n型源极掺杂层202;n型源极掺杂层202上,设置有处于中间位置的脊形沟道结构203、设置于脊形沟道结构203一侧的第一异质结构层204、以及设置于脊形沟道结构203另一侧的第二异质结构层205;脊形沟道结构203上设置有漏电极206;第一异质结构层204上和第二异质结构层205上均设置有栅介质207和栅电极208;衬底201远离n型源极掺杂层202一侧呈背孔结构,暴露出n型源极掺杂层202;衬底201的背孔结构中设置有源电极209;第一异质结构层204在脊形沟道结构203的侧壁上具有二维电子气。

本实施例中提供的半导体射频器件为垂直结构设计,相比水平结构可以有更高的器件密度,栅长及沟道尺寸可通过膜厚控制,对光刻设备的精度要求低,制造难度小。该器件中电流通过脊形沟道结构侧壁上形成的二维电子气传输,器件具有较小的沟道电阻;源电极和漏电极均制作在预先生长的n

在本申请较佳的实施方式中,上述脊形沟道结构包括:设置于n型源极掺杂层上的非故意掺杂层和n型漏极掺杂层。

在本申请较佳的实施方式中,上述脊形沟道结构的侧壁所在平面与衬底的(0001)面平行。

在本申请较佳的实施方式中,上述栅电极与脊形沟道结构侧壁处的第一异质结构层和第二异质结构层形成肖特基接触。

在本申请较佳的实施方式中,上述肖特基接触位于远离漏电极靠近n型源极掺杂层一端。

在本申请较佳的实施方式中,上述第一异质结构层和第二异质结构层具有相同结构,由AlGaN、InAlN、AlN或者InAlGaN其中的一种与GaN组成。

在本申请较佳的实施方式中,上述衬底为具有非极性面表面的三族氮化物半导体。

在本申请较佳的实施方式中,上述衬底具有高电阻。

在本申请较佳的实施方式中,上述栅介质覆盖第一异质结构层和第二异质结构层的部分侧壁。

下面列举一种具体的氮化镓半导体射频器件,其结构示意图如图3所示,该结构中,上述第一异质结构层、第二异质结构层均为AlGaN/GaN层;上述衬底为非极性GaN层;上述n型源极掺杂层为高阻GaN层;上述n型源极掺杂层和n型漏极掺杂层均为n

氮化镓半导体射频器件具备以下特征:

1)从下到上依次为衬底、n

2)脊形沟道结构侧壁和n

3)在AlGaN表面沉积的SiN

4)在脊形沟道结构最上层n

5)在衬底背面刻蚀出背孔结构,暴露出源极掺杂层;在背孔结构中沉积金属形成源电极。

图4为图3所示的具体的GaN射频器件结构的传输特性和跨导特性曲线。器件阈值电压约为-4V,在栅极电压为-3V到2V的范围内,器件具有较好的线性度;

图5为图3所示的具体的GaN射频器件结构的输出特性曲线。

基于上述结构实施例,本申请实施例还提供一种半导体射频器件的制备方法,参见图6所示,该方法具体包括以下步骤:

步骤S402,提供衬底;

步骤S404,在衬底上依次生长n型源极掺杂层、非故意掺杂层、n型漏极掺杂层;

步骤S406,刻蚀n型漏极掺杂层和非故意掺杂层,形成脊形沟道结构;步骤S408,在脊形沟道结构上形成覆盖于脊形沟道结构侧壁、脊形沟道结构中的n型漏极掺杂层、以及n型源极掺杂层上的异质结构层,且异质结构层在脊形沟道结构的一侧侧壁上形成二维电子气;

步骤S410,在异质结构层上沉积绝缘介质层;刻蚀异质结构层侧壁上的部分绝缘介质层和脊形沟道结构中n型漏极掺杂层上的异质结构层,形成栅介质层;在栅介质层上沉积金属,形成栅电极,栅电极与脊形沟道结构侧壁上的第一异质结构层和第二异质结构层形成肖特基接触;

步骤S412,在脊形沟道结构中的n型漏极掺杂层上沉积金属,形成漏电极;

步骤S414,在衬底远离n型源极掺杂层一侧刻蚀出背孔结构,暴露出n型源极掺杂层;在背孔结构中沉积金属形成源电极。

参见图7所示,具体实施中,半导体射频器件的制备过程如下:

1)提供一非极性氮化镓模板作为衬底;

2)在氮化镓模板上生长n型源极掺杂层(n

3)在n型源极掺杂层上生长非故意掺杂氮化镓层(u-GaN);在非故意掺杂氮化镓层上生长n型漏极掺杂层(n

4)刻蚀n

5)再生长AlGaN形成垂直沟道;

6)沉积介质层;

7)刻蚀不需要的介质层和顶层AlGaN;

8)制作源、栅、漏电极。

本实施例中提供的半导体射频器件的制备方法,实现了一种垂直结构设计方法,相比水平结构可以有更高的器件密度,栅长及沟道尺寸可通过膜厚控制,对光刻设备的精度要求低,制造难度小。该器件中电流通过脊形沟道结构侧壁上形成的二维电子气传输,器件具有较小的沟道电阻;源电极和漏电极均制作在预先生长的n

本申请实施例提供的方法,其实现原理及产生的技术效果和前述结构实施例相同,为简要描述,方法的实施例部分未提及之处,可参考前述结构实施例中相应内容。

除非另外具体说明,否则在这些实施例中阐述的部件和步骤的相对步骤、数字表达式和数值并不限制本申请的范围。

在本申请的描述中,需要说明的是,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本申请和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本申请的限制。此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

最后应说明的是:以上所述实施例,仅为本申请的具体实施方式,用以说明本申请的技术方案,而非对其限制,本申请的保护范围并不局限于此,尽管参照前述实施例对本申请进行了详细的说明,本领域的普通技术人员应当理解:任何熟悉本技术领域的技术人员在本申请揭露的技术范围内,其依然可以对前述实施例所记载的技术方案进行修改或可轻易想到变化,或者对其中部分技术特征进行等同替换;而这些修改、变化或者替换,并不使相应技术方案的本质脱离本申请实施例技术方案的精神和范围,都应涵盖在本申请的保护范围之内。因此,本申请的保护范围应所述以权利要求的保护范围为准。

- 提高氮化硅耐腐蚀性的方法和半导体器件的制备方法

- 一种半导体功率器件封装及其制备方法

- 一种超低功耗半导体功率器件及其制备方法

- 半导体器件及定位标记的制备方法

- 拓扑量子框架、包括其的复合负极活性材料、负极、锂电池、半导体和器件、及其制备方法

- 用于制备氮化镓射频器件的衬底及其制备方法、氮化镓射频器件

- 功率半导体器件及其制备方法和射频功率放大器