双通道自动化测试设备

文献发布时间:2024-01-17 01:26:37

技术领域

本发明涉及自动测试设备技术领域,特别涉及一种双通道自动化测试设备。

背景技术

目前关于接收机测试方法主要为手动测试,其测试的方法相当繁琐,部分测试内容在不同条件下也需要重复测试。甚至于批量生产时,需要投入大量的人力物力,费时费力。

发明内容

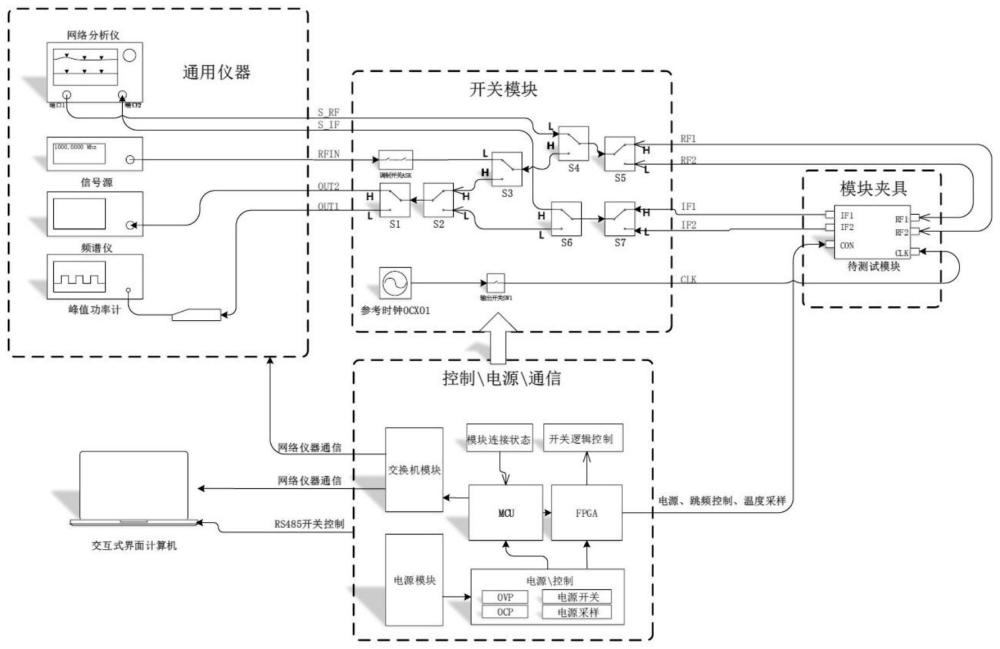

本发明提供了一种双通道自动化测试设备,采用相互连接的通用仪器、控制机箱和模块夹具自动运行测试,自动输出报表,结构简单,便于搭建测试,省时省力。

本发明提供了一种双通道自动化测试设备,包括通用仪器、控制机箱和模块夹具,所述控制机箱包括开关模块、电源供电及通信控制电路,所述开关模块分别连接所述通用仪器、模块夹具、电源供电及通信控制电路,所述电源供电及通信控制电路还连接所述模块夹具和通用仪器,所述电源供电及通信控制电路还连接交互式界面计算机,所述模块夹具用于承载并连接被测模块;

所述电源供电及通信控制电路包括MCU、FPGA、交换机模块、电源\控制模块和电源模块,所述MCU分别连接所述交换机模块、FPGA、电源\控制模块,所述电源\控制模块分别连接所述电源模块、FPGA,FPGA连接模块夹具,用于进行开关逻辑控制,所述交换机模块连接所述通用仪器和交互式界面计算机;

所述控制机箱提供被测模块所需要的射频测试信号、低频控制信号、电源,并通过射频开关模组实现各种信号方向的控制,配合所述通用仪器以实现各电性能指标的自动测试、数据收集和分析。

进一步地,所述开关模块具有多个输入输出接口,包括S_RF、S_IF、RFIN、OUT2、OUT1、CLK、IF1中频输入、IF2中频输入、RF1射频输出、RF2射频输出;所述模块夹具具有多个输入输出接口,包括IF1、IF2、CON、RF1、RF2、CLK;

所述开关模块的S_RF、S_IF口用于连接所述网络分析仪,所述开关模块的RFIN口用于连接所述信号源,所述开关模块的OUT2口用于连接所述频谱仪,所述开关模块的OUT1口用于连接峰值功率计,所述开关模块的CLK口用于连接所述模块夹具的CLK口,所述开关模块的IF1中频输入口连接所述模块夹具的IF1口,所述开关模块的IF2中频输入口连接所述模块夹具的IF2口,所述开关模块的RF1射频输出口连接所述模块夹具的RF2口,所述开关模块的RF2射频输出口连接所述模块夹具的RF1口,所述模块夹具的CON口连接FPGA。

进一步地,所述模块夹具还包括射频电缆引出口IF1、IF2,所述被测模块具有IF1口、IF2口,所述被测模块的IF1口连接所述模块夹具的射频电缆引出口IF1,所述被测模块的IF2口连接所述模块夹具的射频电缆引出口IF2。

进一步地,所述通用仪器包括网络分析仪、信号源、频谱仪和峰值功率计,所述网络分析仪完成所述被测模块输出输入口的驻波测量,并通过所述开关模块实现通道切换;所述信号源通过开关模块切换RF1、RF2产生射频测试信号;所述频谱仪通过开关模块选择IF1、IF2中频信号输入至频谱仪以完成中频幅度测量;所述峰值功率计用于观察脉下工作状态。

进一步地,测试所需的电源由所述控制机箱内电源模块产生,并完成电流采样和开关控制,所述被测模块电源电压从夹具端口采样;交互式界面程序在交互式界面计算机中运行,通过网络交换机与通用仪器互联通信,开关模块中通道切换控制与电源控制通过机箱后串口实现通信。

进一步地,所述开关模块包括:

芯片D1的第一引脚连接电容C1的一端、电阻R2的一端,电容C1的另一端连接电阻R2的另一端并接地,芯片D1的第五引脚连接电阻R36的一端,电阻R36的另一端接地,芯片D1的第十四引脚连接电容C3的一端、电容C2的一端,电容C3的另一端连接电容C2的另一端并接地;

芯片U1的第一引脚连接电容C127的一端、芯片U1的第三引脚、电容C258的一端、电容C259的一端、电容C260的一端、电阻R1的一端,电容C127的另一端接地,电阻R1的另一端连接芯片U1的第二引脚和第四引脚,电容C258的另一端连接电容C259的另一端、电容C260的另一端、电容C111的一端、电容C112的一端、电容C97的一端、电容C98的一端并接地,电容C111的另一端连接电感T3的一端、芯片U1的第五引脚、第六引脚、第七引脚、第八引脚,电感T3的另一端连接电容C112的另一端、电容C97的另一端、电容C98的另一端、和芯片Y1的第十四引脚,芯片Y1的第八引脚连接电容C99的一端、电容C99的另一端连接电阻R89的一端、电阻R87的一端,电阻R89的另一端连接电阻R90的一端并接地,电阻R90的另一端连接电阻R87的另一端、电容C136的一端和SX1,电容C136的另一端连接电阻R66的一端,电阻R66的另一端连接二极管D7的一端,二极管D7的另一端连接电阻R65的一端和电容C135的一端,电容C135的另一端连接电容R65的另一端并接地;

芯片U3的第一引脚连接电容C29的一端,电容C29的另一端连接电容C28的一端并接地,电容C28的另一端连接芯片U3的第二引脚,芯片U3的第四引脚连接电容C43的一端,电容C43的另一端连接SX4,芯片U3的第八引脚连接电容C26的一端,电容C26的另一端连接电阻R3的一端,电阻R3的另一端接地,芯片U3的第五引脚连接电容C44的一端,电容C44的另一端连接电容C45的一端,电容C45的另一端连接芯片U6的第三引脚;

芯片U6的第一引脚连接电容C19的一端,电容C19的另一端连接电容C18的一端并接地,电容C18的另一端连接芯片U6的第二引脚,芯片U6的第八引脚连接电容C32的一端,电容C32的另一端连接电阻R4的一端,电阻R4的另一端接地,芯片U6的第五引脚连接电容C48的一端,电容C48的另一端连接电容C49的一端,电容C49的另一端连接芯片U8的第八引脚;

芯片U8的第五引脚连接电容C55的一端,电容C55的另一端连接电容C73的一端,电容C73的另一端连接芯片U14的第五引脚,芯片U8的第一引脚连接电容C33的一端、电容C14的一端,电容C33的另一端连接电容C14的另一端并接地,芯片U8的第二引脚连接电容C34的一端、电容C15的一端,电容C34的另一端连接电容C15的另一端并接地,芯片U8的第三引脚连接电容C54的一端,电容C54的另一端连接电容C50的一端,电容C50的另一端连接芯片U4的第五引脚;

芯片U4的第八引脚连接电容C36的一端,电容C36的另一端连接SX2,芯片U4的第一引脚连接电容C30的一端、电容C13的一端,电容C30的另一端连接电容C13的另一端并接地,芯片U4的第二引脚连接电容C24的一端、电容C10的一端,电容C24的另一端连接电容C10的另一端并接地,芯片U4的第三引脚连接电容C46的一端,电容C46的另一端连接电容C47的一端,电容C47的另一端连接芯片U5的第三引脚;

芯片U5的第一引脚连接电容C17的一端、电容C11的一端,电容C17的另一端连接电容C11的另一端并接地,芯片U5的第二引脚连接电容C16的一端、电容C9的一端,电容C16的另一端连接电容C9的另一端并接地,芯片U5的第八引脚连接电容C38的一端,电容C38的另一端连接电容C12的一端,电容C12的另一端连接芯片U2的第三引脚,芯片U5的第五引脚连接电容C51的一端,电容C51的另一端电容C57的一端,电容C57的另一端连接芯片U12的第三引脚;

芯片U2的第一引脚连接电容C7的一端、电容C5的一端、电阻R71的一端,电容C7的另一端连接电容C5的另一端并接地,芯片U2的第二引脚连接电容C6的一端、电容C4的一端,电容C6的另一端连接电容C4的另一端并接地,芯片U2的第八引脚连接电容C8的一端,电容C8的另一端连接SX3,芯片U2的第五引脚连接电容C20的一端,电容C20的另一端连接电阻R5的一端,电阻R5的另一端接地;

芯片U12的第一引脚连接电容C53的一端、电容C42的一端,电容C53的另一端连接电容C42的另一端并接地,芯片U12的第二引脚连接电容C52的一端、电容C40的一端,电容C52的另一端连接电容C40的另一端并接地,芯片U12的第八引脚连接电容C56的一端,电容C56的另一端连接电阻R6的一端,电阻R6的另一端接地,芯片U12的第五引脚连接电容C58的一端,电容C58的另一端连接SX5;

芯片U14的第一引脚连接电容C67的一端、电容C61的一端,电容C67的另一端连接电容C61的另一端并接地,芯片U14的第二引脚连接电容C66的一端、电容C59的一端,电容C66的另一端连接电容C59的另一端并接地,芯片U14的第三引脚连接电容C78的一端,电容C78的另一端连接电容C77的一端,电容C77的另一端连接芯片U13的第三引脚,芯片U14的第八引脚连接电容C80的一端,电容C80的另一端连接电容C81的一端,电容C81的另一端连接芯片U15的第八引脚;

芯片U13第一引脚连接电容C70的一端、电容C62的一端,电容C70的另一端连接电容C62的另一端并接地,芯片U13的第二引脚连接电容C68的一端、电容C60的一端,电容C68的另一端连接电容C60的另一端并接地,芯片U13的第八引脚连接电容C76的一端,电容C76的另一端连接SX6,芯片U13的第五引脚连接电容C79的一端,电容C79的另一端连接SX8;

芯片U15的第一引脚连接电容C75的一端、电容C69的一端,电容C75的另一端连接电容C69的另一端并接地,芯片U15的第二引脚连接电容C74的一端、电容C64的一端,电容C74的另一端连接电容C64的另一端并接地,芯片U15的第三引脚连接电容C83的一端,电容C83的另一端连接电容C84的一端,电容C84的另一端连接芯片U16的第三引脚;

芯片U16的第一引脚连接电容C72的一端、电容C65的一端,电容C72的另一端连接电容C65的另一端并接地,芯片U16的第二引脚连接电容C71的一端、电容C63的一端,电容C71另一端连接电容C63的另一端并接地,芯片U16的第八引脚连接电容C82的一端,电容C82的另一端连接SX7,芯片U16的第五引脚连接电容C86的一端,电容C86的另一端连接SX9;

芯片U17的第一引脚连接芯片U17的第二十引脚、电容C87的一端、电容C88的一端、电容C89的一端、电容C90的一端,电容C87的另一端连接电容C88的另一端、电容C89的另一端、电容C90的另一端并接地,芯片U17的第二引脚连接电阻R56,芯片U17的第二引脚连接电阻R57,芯片U17的第二引脚连接电阻R58,芯片U17的第二引脚连接电阻R59,芯片U17的第二引脚连接电阻R60,芯片U17的第二引脚连接电阻R61,芯片U17的第二引脚连接电阻R62。

本发明的有益效果为:

本发明的控制机箱连接模块夹具,模块夹具承载并连接接收机的被测模块,控制机箱提供被测模块所需要的射频测试信号、低频控制信号、电源,并通过射频开关模组实现各种信号方向的控制,配合所述通用仪器以实现各电性能指标的自动测试、数据收集和分析,能够自动运行测试,自动输出报表,结构简单,便于搭建测试,省时省力。

附图说明

图1为本发明双通道自动化测试设备的结构框图。

图2为本发明中控制机箱机械结构内部结构示意图。

图3为本发明中控制机箱机械结构正面的接口示意图。

图4为本发明中控制机箱机械结构反面的接口示意图。

图5为本发明中模块夹具的机械结构示意图。

图6为本发明中交互式界面和机箱控制软件运行流程示意图。

图7为本发明中FPGA电源的电路图。

图8为本发明中FPGA接口的电路图。

图9为本发明中FPGA的电路图。

图10为本发明中FPGA第一外围电路图。

图11为本发明中FPGA第二外围电路图。

图12为本发明中FPGA计算机通信口电路图。

图13为本发明中FPGA第一通信接口电路图。

图14为本发明中FPGA第二通信接口电路图。

图15为本发明中控制机箱状态显示屏的电路图。

图16为本发明中电源模块的电路图。

图17为本发明中开关模块的电路图。

图18为本发明中MCU电源采样、电源控制的电路图。

图19为本发明中通信接口的电路图。

图20为本发明中模块夹具二次稳压、电压采样和温度采样电路图。

本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

如图1所示,本发明提供了一种双通道自动化测试设备,包括通用仪器、控制机箱和模块夹具,所述控制机箱包括开关模块、电源供电及通信控制电路,所述开关模块分别连接所述通用仪器、模块夹具、电源供电及通信控制电路,所述电源供电及通信控制电路还连接所述模块夹具和通用仪器,所述电源供电及通信控制电路还连接交互式界面计算机,所述模块夹具用于承载并连接被测模块;

如图2所示,控制机箱包括开关模块、电源供电及通信控制电路,所述电源供电及通信控制电路包括MCU、FPGA、交换机模块、电源\控制模块和电源模块,所述MCU分别连接所述交换机模块、FPGA、电源\控制模块,所述电源\控制模块分别连接所述电源模块、FPGA,FPGA连接模块夹具,用于进行开关逻辑控制,所述交换机模块连接所述通用仪器和交互式界面计算机;

所述控制机箱提供被测模块所需要的射频测试信号、低频控制信号、电源,并通过射频开关模组实现各种信号方向的控制,配合所述通用仪器以实现各电性能指标的自动测试、数据收集和分析。

所述开关模块具有多个输入输出接口,其表现在控制机箱的机械结构的表面形式上,如图3、图4,包括S_RF、S_IF、RFIN、OUT2、OUT1、CLK、IF1中频输入、IF2中频输入、RF1射频输出、RF2射频输出;所述模块夹具具有多个输入输出接口,如图5所示,包括IF1、IF2、CON、RF1、RF2、CLK,模块夹具还包括旋转锁紧装置,用于固定被测模块。

所述开关模块的S_RF、S_IF口用于连接所述网络分析仪,所述开关模块的RFIN口用于连接所述信号源,所述开关模块的OUT2口用于连接所述频谱仪,所述开关模块的OUT1口用于连接峰值功率计,所述开关模块的CLK口用于连接所述模块夹具的CLK口,所述开关模块的IF1中频输入口连接所述模块夹具的IF1口,所述开关模块的IF2中频输入口连接所述模块夹具的IF2口,所述开关模块的RF1射频输出口连接所述模块夹具的RF2口,所述开关模块的RF2射频输出口连接所述模块夹具的RF1口,所述模块夹具的CON口连接FPGA。

所述模块夹具还包括射频电缆引出口IF1、IF2,所述被测模块具有IF1口、IF2口,所述被测模块的IF1口连接所述模块夹具的射频电缆引出口IF1,所述被测模块的IF2口连接所述模块夹具的射频电缆引出口IF2。

所述通用仪器包括网络分析仪、信号源、频谱仪和峰值功率计,所述网络分析仪完成所述被测模块输出输入口的驻波测量,并通过所述开关模块实现通道切换;所述信号源通过开关模块切换RF1、RF2产生射频测试信号;所述频谱仪通过开关模块选择IF1、IF2中频信号输入至频谱仪以完成中频幅度测量;所述峰值功率计用于观察脉下工作状态。

测试所需的电源由所述控制机箱内电源模块产生,并完成电流采样和开关控制,所述被测模块电源电压从夹具端口采样;交互式界面程序在交互式界面计算机中运行,运行流程图如图6所示,通过网络交换机与通用仪器互联通信,开关模块中通道切换控制与电源控制通过机箱后串口实现通信。

本发明具有的电源和保护功能包括:1、被测模块失锁检测功能;2、被测模块采用二次稳压,保证+5V稳定;3、测试电源信息显示;4、测试模块连接异常告警;5、测试模块电源短路、过载保护;

本发明的功能特性包括:1、工作频率测试;2、通道增益测试;3、2通道幅度一致性测试;4、射频程控步进、程控深度测试;5、中频带外抑制测试;6、接收通道隔离度测试;7、频率容差测试;8、输入P-1dB测试;9、中频饱和输出测试;10、抑制、杂波抑制、镜频抑制测试;11、输入端口本振泄露测试;12、输出输入端口驻波测试;13、测试系统误差修正功能;14、测试报告输出功能;

本发明的工作原理:

a.端口驻波测量,通用仪器中网络分析仪完成被测模块输出输入口的驻波测量,通道切换通过开关模块实现。

b.测试信号产生,信号源产生射频测试信号通过开关模块切换RF1、RF2实现测试所的测试信号。

c.中频幅度测量,IF1、IF2中频信号经过开关模块选择输入至频谱仪完成幅度测量。

d.峰值功率计为预留设计,便于观察脉下工作状态。

e.测试所需的电源由机箱内AC-DC电源模块产生,并完成电流采样和开关控制,被测模块电源电压从夹具端口采样。

f.交互式界面程序在计算机中运行,通过网络交换机与其他通用仪器互联通信,开关模块中通道切换控制与电源控制通过机箱后串口实现通信;

在安装接线时,连接电源AC电源线到双通道自动化测试系统,连接主机前面板射频口与模块夹具的射频线RF1、RF2、IF1、IF2、100Mhz,连接主机后面板射频口与模块夹具的射频线,信号源RF_IN、频谱仪OUT2、网络分析仪1端口S_RF、网络分析仪2端口S_IF,连接主机前面板与模块夹具的37芯低频线。

本发明系统结构简单,便于搭建测试;自动运行,自动输出报表;供电短路保护,被测模块电源异常时关断输出;异常告警功能,可快速定位故障模块及通道;操作界简单,可快速上手。

如图7-20展示了本发明双通道自动化测试设备中FPGA电源的电路图、FPGA接口的电路图、FPGA的电路图、FPGA第一外围电路图、FPGA第二外围电路图、FPGA计算机通信口电路图、FPGA第一通信接口电路图、FPGA第二通信接口电路图、控制机箱状态显示屏的电路图、电源模块的电路图、开关模块的电路图、MCU电源采样和电源控制的电路图、通信接口的电路图、模块夹具二次稳压以及电压采样和温度采样电路图。

如图17所示,所述开关模块具体包括:

芯片D1的第一引脚连接电容C1的一端、电阻R2的一端,电容C1的另一端连接电阻R2的另一端并接地,芯片D1的第五引脚连接电阻R36的一端,电阻R36的另一端接地,芯片D1的第十四引脚连接电容C3的一端、电容C2的一端,电容C3的另一端连接电容C2的另一端并接地;

芯片U1的第一引脚连接电容C127的一端、芯片U1的第三引脚、电容C258的一端、电容C259的一端、电容C260的一端、电阻R1的一端,电容C127的另一端接地,电阻R1的另一端连接芯片U1的第二引脚和第四引脚,电容C258的另一端连接电容C259的另一端、电容C260的另一端、电容C111的一端、电容C112的一端、电容C97的一端、电容C98的一端并接地,电容C111的另一端连接电感T3的一端、芯片U1的第五引脚、第六引脚、第七引脚、第八引脚,电感T3的另一端连接电容C112的另一端、电容C97的另一端、电容C98的另一端、和芯片Y1的第十四引脚,芯片Y1的第八引脚连接电容C99的一端、电容C99的另一端连接电阻R89的一端、电阻R87的一端,电阻R89的另一端连接电阻R90的一端并接地,电阻R90的另一端连接电阻R87的另一端、电容C136的一端和SX1,电容C136的另一端连接电阻R66的一端,电阻R66的另一端连接二极管D7的一端,二极管D7的另一端连接电阻R65的一端和电容C135的一端,电容C135的另一端连接电容R65的另一端并接地;

芯片U3的第一引脚连接电容C29的一端,电容C29的另一端连接电容C28的一端并接地,电容C28的另一端连接芯片U3的第二引脚,芯片U3的第四引脚连接电容C43的一端,电容C43的另一端连接SX4,芯片U3的第八引脚连接电容C26的一端,电容C26的另一端连接电阻R3的一端,电阻R3的另一端接地,芯片U3的第五引脚连接电容C44的一端,电容C44的另一端连接电容C45的一端,电容C45的另一端连接芯片U6的第三引脚;

芯片U6的第一引脚连接电容C19的一端,电容C19的另一端连接电容C18的一端并接地,电容C18的另一端连接芯片U6的第二引脚,芯片U6的第八引脚连接电容C32的一端,电容C32的另一端连接电阻R4的一端,电阻R4的另一端接地,芯片U6的第五引脚连接电容C48的一端,电容C48的另一端连接电容C49的一端,电容C49的另一端连接芯片U8的第八引脚;

芯片U8的第五引脚连接电容C55的一端,电容C55的另一端连接电容C73的一端,电容C73的另一端连接芯片U14的第五引脚,芯片U8的第一引脚连接电容C33的一端、电容C14的一端,电容C33的另一端连接电容C14的另一端并接地,芯片U8的第二引脚连接电容C34的一端、电容C15的一端,电容C34的另一端连接电容C15的另一端并接地,芯片U8的第三引脚连接电容C54的一端,电容C54的另一端连接电容C50的一端,电容C50的另一端连接芯片U4的第五引脚;

芯片U4的第八引脚连接电容C36的一端,电容C36的另一端连接SX2,芯片U4的第一引脚连接电容C30的一端、电容C13的一端,电容C30的另一端连接电容C13的另一端并接地,芯片U4的第二引脚连接电容C24的一端、电容C10的一端,电容C24的另一端连接电容C10的另一端并接地,芯片U4的第三引脚连接电容C46的一端,电容C46的另一端连接电容C47的一端,电容C47的另一端连接芯片U5的第三引脚;

芯片U5的第一引脚连接电容C17的一端、电容C11的一端,电容C17的另一端连接电容C11的另一端并接地,芯片U5的第二引脚连接电容C16的一端、电容C9的一端,电容C16的另一端连接电容C9的另一端并接地,芯片U5的第八引脚连接电容C38的一端,电容C38的另一端连接电容C12的一端,电容C12的另一端连接芯片U2的第三引脚,芯片U5的第五引脚连接电容C51的一端,电容C51的另一端电容C57的一端,电容C57的另一端连接芯片U12的第三引脚;

芯片U2的第一引脚连接电容C7的一端、电容C5的一端、电阻R71的一端,电容C7的另一端连接电容C5的另一端并接地,芯片U2的第二引脚连接电容C6的一端、电容C4的一端,电容C6的另一端连接电容C4的另一端并接地,芯片U2的第八引脚连接电容C8的一端,电容C8的另一端连接SX3,芯片U2的第五引脚连接电容C20的一端,电容C20的另一端连接电阻R5的一端,电阻R5的另一端接地;

芯片U12的第一引脚连接电容C53的一端、电容C42的一端,电容C53的另一端连接电容C42的另一端并接地,芯片U12的第二引脚连接电容C52的一端、电容C40的一端,电容C52的另一端连接电容C40的另一端并接地,芯片U12的第八引脚连接电容C56的一端,电容C56的另一端连接电阻R6的一端,电阻R6的另一端接地,芯片U12的第五引脚连接电容C58的一端,电容C58的另一端连接SX5;

芯片U14的第一引脚连接电容C67的一端、电容C61的一端,电容C67的另一端连接电容C61的另一端并接地,芯片U14的第二引脚连接电容C66的一端、电容C59的一端,电容C66的另一端连接电容C59的另一端并接地,芯片U14的第三引脚连接电容C78的一端,电容C78的另一端连接电容C77的一端,电容C77的另一端连接芯片U13的第三引脚,芯片U14的第八引脚连接电容C80的一端,电容C80的另一端连接电容C81的一端,电容C81的另一端连接芯片U15的第八引脚;

芯片U13第一引脚连接电容C70的一端、电容C62的一端,电容C70的另一端连接电容C62的另一端并接地,芯片U13的第二引脚连接电容C68的一端、电容C60的一端,电容C68的另一端连接电容C60的另一端并接地,芯片U13的第八引脚连接电容C76的一端,电容C76的另一端连接SX6,芯片U13的第五引脚连接电容C79的一端,电容C79的另一端连接SX8;

芯片U15的第一引脚连接电容C75的一端、电容C69的一端,电容C75的另一端连接电容C69的另一端并接地,芯片U15的第二引脚连接电容C74的一端、电容C64的一端,电容C74的另一端连接电容C64的另一端并接地,芯片U15的第三引脚连接电容C83的一端,电容C83的另一端连接电容C84的一端,电容C84的另一端连接芯片U16的第三引脚;

芯片U16的第一引脚连接电容C72的一端、电容C65的一端,电容C72的另一端连接电容C65的另一端并接地,芯片U16的第二引脚连接电容C71的一端、电容C63的一端,电容C71另一端连接电容C63的另一端并接地,芯片U16的第八引脚连接电容C82的一端,电容C82的另一端连接SX7,芯片U16的第五引脚连接电容C86的一端,电容C86的另一端连接SX9;

芯片U17的第一引脚连接芯片U17的第二十引脚、电容C87的一端、电容C88的一端、电容C89的一端、电容C90的一端,电容C87的另一端连接电容C88的另一端、电容C89的另一端、电容C90的另一端并接地,芯片U17的第二引脚连接电阻R56,芯片U17的第二引脚连接电阻R57,芯片U17的第二引脚连接电阻R58,芯片U17的第二引脚连接电阻R59,芯片U17的第二引脚连接电阻R60,芯片U17的第二引脚连接电阻R61,芯片U17的第二引脚连接电阻R62。

如图2-3,AC电源线连接到双通道自动化测试系统后按下左测电源按钮设备将开机,电源按钮指示灯点亮;设备在开机状态下按下电源按钮后将立即切断整机电源,仅保留待机电源通电;关机前应首先关闭连接开关;按下“连接\断开”按钮测试电源将被开启,+5V、-5V开始上电,同时监测电源状态;

在机箱主界面中,设备在加电后初始化完成后显示“开关状态”界面,当上位机程序对内部射频开关进行控制后,屏幕上将会同步更新显示开关当前的状态;在夹具连接完成后,按下“连接\断开”后屏幕将显示电源信息界面,+Vs为被测模块+5V电源实时电压,-V为被测模块负电源实时电压,Icc为被测模块+5v电源的实时电流,nI为北侧模块负电源电流;“电源信息”界面在持续数秒后将自动切换到“开关状态界面”。

在交互式用户界面中,电脑与测试系统的连接通过USB<->RS232转换线连接测试电脑USB口与测试机箱面板的RS232接口;交叉网线连接测试电脑与测试机箱面板或背板的RJ45口;

在被测件与测试系统的连接中,专用相参双通道连接线连接被测件与测试机箱面板对应专用接口;射频电缆连接相参双通道被测件与测试机箱面板对应接口(询问连询问,应答连应答)。

需要说明的是,在本文中,术语“包括”、“包含”或者其任何其它变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、装置、物品或者方法不仅包括那些要素,而且还包括没有明确列出的其它要素,或者是还包括为这种过程、装置、物品或者方法所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括该要素的过程、装置、物品或者方法中还存在另外的相同要素。

以上所述仅为本发明的优选实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

- 用于测试包括处理单元和程序和/或数据存储器的被测装置的自动化测试设备和包括测试控制器、与被测装置的一个或多个接口、共享存储器的自动化测试设备以及用于测试被测装置的方法

- 电源、自动化测试设备、用于操作电源的方法、用于操作自动化测试设备的方法和使用电压变动补偿机制的计算机程序