一种跨模块的高速数据流连续回放处理方法

文献发布时间:2024-01-17 01:26:37

技术领域

本发明属于数据流回放处理技术领域,具体涉及一种跨模块的高速数据流连续回放处理方法。

背景技术

高速数据流连续回放处理是数据流回放领域的一项关键技术。随着数据采集量日益增大,数据流回放业务需要面对的数据流速率越来越大,如何保证大容量数据流高速传输、连续回放成为亟需解决的问题;同时,为了连续回放多个存储模块中的数据流,保证还原后的数据的连续性,需要设计可靠的交互机制;并且,面对多格式、多速率的数据流,解帧数据流的参数特征,如采样率,并针对数据特征进行回放数据流速率自动匹配,是有必要的。

现有数据流回放处理技术总体框图如图1,利用高速传输口将存储模块中的数据流传回主控单元,然后进行数据流缓存,数据流缓存多采用FIFO实现,解决数据流缓存的同时,完成了跨时钟域处理;接着从缓存区读出数据流,根据采样率完成数据还原,最终数据从DA完成回放。现有技术,多采用大容量FLASH的、FLASH阵列、板上磁盘阵列或采用大容量CF卡进行数据流存储,当面临容量扩展、系统中需要设置多个存储模块时,没有给出有效的控制机制,以保证高速大容量高速数据流连续回放;同时FLASH存储或者CF卡存储,存储容量有限;并且,面对多格式、多速率的数据流回放需求时,无法实现回放数据流速率自动匹配。

发明内容

针对现有技术中存在的上述技术问题,本发明提出了一种跨模块的高速数据流连续回放处理方法,设计合理,克服了现有技术的不足,具有良好的效果。

为了实现上述目的,本发明采用如下技术方案:

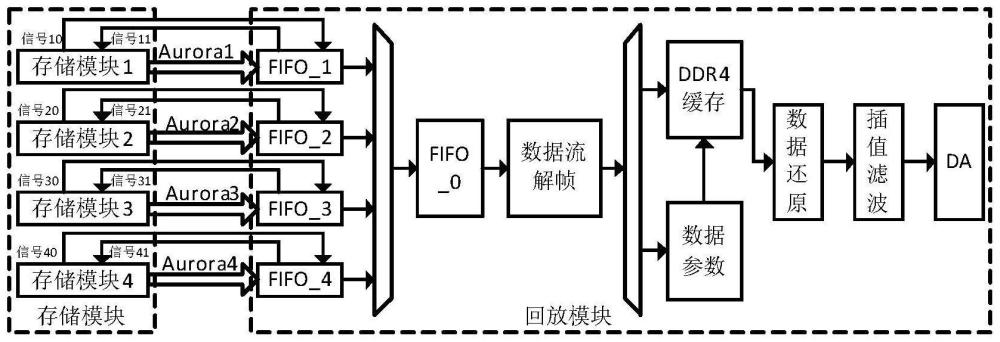

一种跨模块的高速数据流连续回放处理方法,设置存储模块和回放模块,所述存储模块中包括4个存储单元1~4,所述回放模块中配置了缓存器FIFO_x,x为0、1、2、3和4,4个存储单元分别与缓存器FIFO_1~FIFO_4通过2根通信信号线相连,缓存器FIFO_1~FIFO_4共同连接至缓存器FIFO_0;

该方法包括以下步骤:

S1、待回放数据流从存储模块自动连续传输到回放模块,每个存储单元和回放模块之间的数据流传输通过AURORA高速传输口实现;所述数据流文件包括多个文件,每个文件由一个文件头和M个数据段组成;每个数据段由一个数据段头和N个数据块组成;每个数据块由一个数据块头和Q个待还原数据组成;

S2、数据流解帧,当一个数据流文件中的所有数据段以及各数据段中的全部数据块解帧完毕,即完成一个文件解帧,解帧得到数据类型、采样率及待还原数据,继续解帧下一个文件;

S3、将待还原数据缓存到DDR4中,数据类型和采样率写入寄存器待用;

S4、利用采样率和数据类型控制DDR4数据读出的速度,自动匹配不同格式、不同采样率的数据的还原,最后通过DA输出,实现数据回放。

进一步地,步骤S1包括以下子步骤:

S1.1、当系统上电后,上位机控制存储单元1作为在线模块进入工作状态,当存储单元1接收到来自FIFO_1的信号11的第一个上升沿后进入数据流可传输状态,当缓存深度达到对应缓存器的深度的3/4,信号11归零,停止数据流传输;当数据量少于对应缓存器的深度的1/4,信号11置1,继续传输数据流;

S1.2、当存储单元1中的数据流全部传输完毕,控制信号10归零后置1,同时在数据流中插入一个数据尾1,值为一个位宽为512位的可设置数据;当回放模块接收到来自存储单元1的信号10传输的信号的上升沿以后,开始搜索数据尾1,当接收到数据尾1时,表示存储单元1的数据流全部传输到缓存器FIFO_1;

S1.3、上位机依次控制存储单元2~4作为在线模块进入工作状态,将存储单元2~4中的数据流全部传输到缓存器FIFO_2~FIFO_4,FIFO_1~FIFO_4最后将数据统一传输给FIFO_0。

进一步地,每个AURORA共有8个lane,单lane传输速度为8Gb/s,综合传输效率能够给实现不小于54.4Gb/s的数据流传输速率。

进一步地,步骤S2包括以下子步骤:

S2.1、空闲状态下,等一个时钟周期后开始识别头数据,若未识别到头数据,则停留在识别文件头数据状态;

S2.2、当识别到头数据,则判断头数据类型状态;若识别到的头数据为文件头,则开始解帧文件头,并将文件头的数据寄存;

S2.3、再次开始识别头数据,识别到第一个数据段头,解帧数据段头,从数据段头中解帧出数据采样率和数据类型;

S2.4、继续识别头数据,识别到第一个数据块头,从数据块头中解帧出数据块长度;

S2.5、从数据块头后可依次从数据块中解帧出Q个待还原数据;

S2.6、继续识别头数据,识别到第二个数据块头,完成第二个数据块的数据块头和待还原数据解帧操作,直到完成所有N个数据块的解帧,即完成第一个数据段的解帧;

S2.7、继续识别头数据,识别到第二个数据段头,完成第二个数据段头中全部数据块的解帧,直到完成所有单个文件中M个数据段中全部数据块的解帧,从而完成当前数据流中一个文件的解帧。

S2.8、继续解帧下一个文件,返回到S2.2继续执行。

进一步地,步骤S3中,DDR4采用读数据优先级高于写数据的优先级工作,在读数据空闲的周期内进行数据写入,补充新的数据;同时使解帧写入的数据保持比读出的数据多一段地址片。

进一步地,所述DDR4用户式中采用1333/4MHZ,用户数据处理宽度为512位。

在步骤S4中,将采样率小于DA输入数据采样率的待还原数据利用插值滤波器实现采样率的提高,最终将统一了数据采样率的数据通过DA输出。

进一步地,待还原数据的最大采样率为200MSPS,8路并行,单路数据位宽最大为32位,待还原数据最大数据速率为51.2Gb/s。

本发明所带来的有益技术效果:

1)跨模块数据连续回放:在需要回放数据量扩展的场景中,支持配置多个存储模块。设计了有效的机制,完成跨模块数据流连续传输控制,可实现跨模块回放数据连续。

2)数据流回放速率自动匹配:本方法可自动完成多格式、多采样率的数据流的解帧,不同格式、采样率的数据还原需要不同的数据量,进而决定缓存区内待还原数据的读出速度,并反馈到缓存区的数据写入速度和高速传输口的数据流传输速度,从而实现回放数据流速率自动匹配。

附图说明

图1为现有数据流回放处理方法原理框图;

图2为本发明提出的高速数据流连续回放处理方法原理框图;

图3为本发明提出存储模块和回放模块数据流传输原理图;

图4为本发明提出的数据流中文件格式图;

图5为本发明中提出的数据流解帧原理图;

具体实施方式

一种跨模块的高速数据流连续回放处理方法,设置存储模块和回放模块,存储模块中包括4个存储单元1~4,回放模块中配置了缓存器FIFO_x,x为0、1、2、3和4,4个存储单元分别与缓存器FIFO_1~FIFO_4通过2根通信信号线x0和x1相连,负责存储单元切换及存储单元与回放单元之间的信号交互,缓存器FIFO_1~FIFO_4共同连接至缓存器FIFO_0;

如图2所示,该方法包括以下步骤:

S1、待回放数据流从存储模块自动连续传输到回放模块,如图4所示,数据流包括多个文件,每个文件由一个文件头和M个数据段组成,每个数据段由一个数据段头和N个数据块组成,每个数据块由一个数据块头和Q个待还原数据组成,存储模块和回放模块之间的数据流传输通过AURORA高速传输口实现,单个AURORA一共8个lane,单lane传输速度8Gb/s,结合传输效率,考虑传输效率,可保证不许爱与54.4Gb/s的数据流传输速度;

步骤S1包括以下子步骤:

S1.1、当系统上电后,上位机控制存储单元1作为在线模块进入工作状态,当存储单元1接收到来自FIFO_1的信号11的第一个上升沿后进入数据流可传输状态,当缓存深度达到对应缓存器的深度的3/4,信号11归零,停止数据流传输;当数据量少于对应缓存器的深度的1/4,信号11置1,继续传输数据流;

S1.2、当存储单元1中的数据流全部传输完毕,控制来自存储单元1的信号10归零后置1,同时在数据中插入一个数据尾1,如图3所示,值为一个位宽为512位的可设置数据;当回放模块接收到信号10的上升沿以后,开始搜索数据尾1,当接收到数据尾1时,表示存储单元1的数据流全部传输到缓存器FIFO_1,如图4所示;

S1.3、当存储单元2接收到信号21的第一个上升沿后开始数据传输,信号21监控FIFO_2的数据量,当缓存深度达到FIFO_2的深度的3/4,信号21归零,停止数据流传输;当缓存深度小于FIFO_2的深度的1/4,信号21置1,继续传输数据流。当存储单元2中的数据流全部传输完毕,控制来自存储单元2的信号20归零后置1,同时在数据流中插入一个数据尾2,值同数据尾1;当回放模块接收到信号20的上升沿以后,开始搜索数据尾2,当接收到数据尾2时,表示存储单元2的数据流全部传输到缓存器FIFO_2;上位机依次控制存储单元3和4作为在线模块进入工作状态,将存储单元3和4中的数据流全部传输到缓存器FIFO_3~FIFO_4,数据尾3和数据尾4的值与数据尾1相同,FIFO_1~FIFO_4最后将数据流传输给FIFO_0。

S2、数据流解帧,当一个数据流文件中的所有数据段以及各数据段中的全部数据块解帧完毕,即完成一个文件解帧,解析得到数据类型、采样率及待还原数据,继续解帧下一个文件;

如图5所示,步骤S2包括以下子步骤:

S2.1、空闲状态下,等一个时钟周期后开始识别头数据,若未识别到头数据,则停留在识别文件头数据状态;

S2.2、当识别到头数据,则判断头数据类型状态;若识别到的头数据为文件头,则开始解帧文件头,并将文件头的数据寄存;

S2.3、再次开始识别头数据,识别到第一个数据段头,解帧数据段头,从数据段头中解帧出数据采样率和数据类型等参数,将数据段头解帧出的数据寄存;

S2.4、继续识别头数据,识别到第一个数据块头,从数据块头中解帧出数据块长度,将数据块头长度数据寄存;

S2.5、从数据块头后可依次从数据块中解帧出Q个待还原数据;

S2.6、继续识别头数据,识别到第二个数据块头,完成第二个数据块的数据块头和待还原数据解帧操作,直到完成所有N个数据块的解帧,即完成第一个数据段的解帧;

S2.7、继续识别头数据,识别到第二个数据段头,完成第二个数据段头中全部数据块的解帧,直到完成所有单个文件中M个数据段中全部数据块的解帧,从而完成当前数据流中一个文件的解帧。

S2.8、继续解帧下一个文件,返回到S2.2继续执行。

S3、将待还原数据缓存到DDR4中,数据类型和采样率写入寄存器待用,采用单DDR4完成数据缓存,DDR4用户时钟采用1333/4MHz,用户数据处理宽度为512b,结合数据处理效率,可保证大于64Gb/s的数据处理速度;

DDR4采用读数据优先级高于写数据的优先级工作,在读数据空闲的周期内进行数据写入,补充新的数据;同时保证解帧后写入DDR4的数据保持比读出的数据多一段地址片,在本实施例中,多缓存的数据量为不同采样率数据流在150毫秒时间内的数据量,这样控制存储模块切换过程在100毫秒内完成,即可以保证有足够的数据保证还原后数据的连续性。

S4、利用采样率和数据类型控制DDR4数据读出的速度,通过逐级反馈控制实现不同格式、采样率的数据流回放速率的自动匹配。将采样率小于DA输入数据采样率的待还原数据利用插值滤波器实现采样率的提高,最终将统一了数据采样率的数据通过DA输出。待还原数据的最大采样率为200MSPS,8路并行,单路数据位宽最大为32位,待还原数据最大数据速率为51.2Gb/s。

当然,上述说明并非是对本发明的限制,本发明也并不仅限于上述举例,本技术领域的技术人员在本发明的实质范围内所做出的变化、改型、添加或替换,也应属于本发明的保护范围。

- 一种用于高速大规模并发数据流的数据流表处理方法及装置

- 一种用于高速大规模并发数据流的数据流表处理方法及装置