基于流速控制的大面阵CMOS探测器数据缓存异速匹配方法

文献发布时间:2024-01-17 01:27:33

技术领域

本发明涉及图像数据处理技术领域,特别是涉及一种基于流速控制的大面阵CMOS探测器数据缓存异速匹配方法。

背景技术

在利用FPGA对大面阵CMOS探测器输入图像数据流进行缓存处理时,需要对输入输出不同速率的图像数据流进行缓存速率匹配,保证缓存区无数据堆积,数据流输出稳定。在空间遥感领域,大面阵CMOS探测器图像数据缓存处理时,多采用乒乓存储结构,实现行图像和帧图像缓存。行图像缓存是指缓存1行图像数据,按照输出速率要求输出一行图像;帧图像缓存是指缓存一帧图像数据,在执行图像预处理后,并按照输出速率要求输出一帧图像。

在空间可见光遥感中使用的大面阵CMOS探测器,靶面越来越大。行图像达到10K像元以上,帧图像达到100M像元以上,如长光辰芯公司的GMAX32152探测器,像元规模达到了16K×9K。由于FPGA内部存储资源限制,单片FPGA已无法完成帧图像缓存,因此,设计时增加了外部高速存储器,如DDR2-SDRAM、DDR3-SDRAM等。SDRAM存储器在数据写入时,需要对存储单元执行定时刷新操作,因此,数据写入过程被中断,图像数据不是以固定速率完成写入操作;DDR3-IP核用户端口根据SDRAM的执行状态判断当前是否可执行读写操作。当用户驱动时钟为100Mhz时,其图像数据存取平均速率可达80Mhz左右。因此,在为DDR3-IP核提供待存储图像数据时,需要按照存取平均速率设计,这就产生了图像数据缓存速率不匹配问题(即异速问题)。

解决数据异速问题的一般方法是采用数据乒乓存储的方式,在FPGA内部开辟两组RAM存储区域,第一组RAM存储奇数行图像数据,第二组RAM存储偶数行图像数据,交替完成。在存储第二组RAM时,读取第一组RAM数据,完成数据整合后,存入DDR3-SDRAM,以此类推。这种缓存模式,只需要保证图像数据从RAM中读出并存储到DDR3-SDRAM的时间小于输入图像数据的缓存时间,即可避免数据存取冲突。

在上述图像数据缓存设计方法中,占用了FPGA较多的RAM存储资源。对于行缓存120Kb的图像,需要占用240Kb的RAM存储资源;如果采用BlockRAM,则BLOCKRAM的例化数量增加一倍,对于需要RAM资源执行预处理算法的大规模数字系统来说,是极其不利的;RAM的大量使用,增大了FPGA的动态功耗,对电源系统、散热均有影响。

发明内容

针对现有的大面阵CMOS探测器图像数据缓存设计方法存在的FPGA内部RAM的资源占用率高、增加FPGA动态功耗的问题,本发明提供了一种基于流速控制的大面阵CMOS探测器数据缓存异速匹配方法,在实现基于DDR3-SDRAM的图像数据缓存异速处理时,能够降低FPGA内部RAM资源占用率,从而释放RAM资源,完成更多图像预处理功能,同时降低器件功耗。

为解决上述问题,本发明采取如下的技术方案:

基于流速控制的大面阵CMOS探测器数据缓存异速匹配方法,大面阵CMOS探测器采用多通道同步输出方式输出图像数据至FPGA,FPGA内部双口RAM对输入的多通道图像数据进行缓存,DDR3-IP核控制器从FPGA内部双口RAM中读出缓存数据并写入DDR3-SDRAM中;

利用流速控制的方法对FPGA内部双口RAM的读写操作进行异速匹配,具体包括以下过程:

根据双口RAM的写速率计算图像数据缓存量A;

判断缓存量A是否大于门限T

计算缓存量A与读出量B的流量差C,并根据流量差C与门限T

当T

当C≤T

当C=T

当C>T

其中,门限T

与现有技术相比,本发明具有以下有益效果:

本发明所提出的基于流速控制的大面阵CMOS探测器数据缓存异速匹配方法通过一级缓存双口RAM,利用流速控制的方法,实现了图像数据异速匹配;在对图像数据缓存和输出控制时,降低了FPGA内部RAM的资源利用率;与现有方法相比,能够释放1/2的双口RAM资源用于图像处理;资源利用率的降低也导致FPGA动态功耗的降低。

附图说明

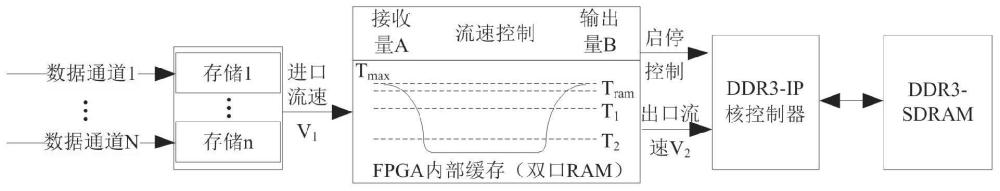

图1为本发明实施例中流速控制原理框图;

图2为本发明实施例中流速控制方法和控制时序;

图3为本发明实施例中大面阵CMOS探测器数据存储组织结构示意图;

图4为本发明实施例中采用流速控制方法获得的可见光相机图像。

具体实施方式

下面将结合附图及较佳实施例对本发明的技术方案进行详细描述。

本发明针对不同速率的图像数据流,在FPGA内进行缓存处理占用较多存储资源的问题,提出了一种基于流速控制的大面阵CMOS探测器数据缓存异速匹配方法,能够对数据缓存控制时序进行优化,在图像数据缓存时,通过流速追赶法实现图像数据流速控制,达到图像数据缓存时异速匹配的目的。

大面阵CMOS探测器采用多通道同步输出方式输出图像数据至FPGA,FPGA内部双口RAM对输入的多通道图像数据进行缓存,DDR3-IP核控制器从FPGA内部双口RAM中读出缓存数据并写入DDR3-SDRAM中。

本实施例提供的异速匹配方法主要包括大面阵CMOS探测器图像缓存数据组织结构、图像缓存流速控制原理、图像缓存流速控制时序以及图像存储空间分配策略四个方面。

1)数据组织结构

大面阵CMOS探测器采用多通道同步输出方式输出图像数据,输入通道最多可达100路;图像数据量化位数多为12bits。FPGA在完成数据接收缓存时,根据DDR3-IP核并行输入图像数据位宽为基准,对输入多通道图像数据进行数据重排。

DDR3-IP核用户数据总线位宽,可设置2Nbit(N=7,8,9,10);FPGA在接收多通道同步输入图像数据时,根据IP核设置,同步写入多通道图像数据。当IP核用户数据总线位宽为256bit时,每次可写入21个图像通道对应的像元(252bits)数据。

当探测器像元输出速率低于DDR3-IP核用户数据总线存储速率时,通过分时处理,实现更多图像通道的数据缓存功能。例如,图像数据输入速率25Mhz,存储平均速率按75Mhz(以DDR3-IP核工作时钟100MHz,效率75%)计算,则可同时完成63通道的图像数据缓存功能。

2)流速控制原理

流速控制的原理如图1所示。进口流速V

根据双口RAM的写速率,计算图像数据缓存量(也称为接收量)A;判断缓存量A是否大于门限T

探测器以一定速率输出图像数据,并匀速写入FPGA,进口流速V

根据SDRAM刷新时间,计算缓存量A与读出量B的理论最大差值,并设置门限T

由于V

该方法通过FPGA内部1组双口RAM实现了探测器图像数据缓存异速匹配,减少FPGA内部RAM资源使用率,从资源、速率方面降低了FPGA的动态功耗。

3)流速控制时序

大面阵CMOS探测器图像数据缓存异速匹配的流速控制时序如图2所示。图像数据输入到缓存RAM时,记录缓存数据数量A,当A>T

图像数据从缓存区读出,写入到SDRAM时,记录读出数据量B,计算缓存量A与读出量B的流量差C=A-B,根据流量差C与门限T

当T

当C≤T

当C=T

当C>T

本方法采用追赶法实现数据流速控制,通过1组BLOCKRAM实现数据缓存异速匹配。通过控制DDR3-IP核驱动时序,减少FPGA内部缓存数据容量,降低FPGA动态功耗。

4)存储空间分配策略

SDRAM的读写速率平均效率可达到80%以上,以大面阵CMOS探测器单通道行像元数量设置RAM的缓存区容量T

由于DDR3-IP核控制器写地址、写数据独立控制,以1帧图像数据量M为单位设置SDRAM存储数据。当读出数据量B=M时,停止IP核写时序,并根据M值,控制写地址范围。

当写数据和写地址数量均达到M后,一帧图像存储结束,启动DDR3-IP核控制器的读时序,输出图像数据。读时序结束后,初始化FPGA内部寄存器,启动下一帧图像数据缓存控制。

本方法通过一级缓存双口RAM,利用流速控制的方法,实现了图像数据异速匹配;在对图像数据缓存和输出控制时,降低了FPGA内部RAM的资源利用率;与现有方法相比,能够释放1/2的双口RAM资源用于图像处理;资源利用率的降低也导致FPGA动态功耗的降低。

下面结合图3所示的具体实例对本发明的异速匹配方法进行详细描述。

在某项目可见光大面阵CMOS探测器成像系统设计中,图像数据以行为单位传输,并行输入图像36路,每路图像数据频率为25MHz,等效像元数据率为25×36=900Mhz。

采用一片DDR3-SDRAM完成数据转存,通过FPGA内部集成的DDR3-ip核控制器实现存储控制。IP核用户端口数据率为100Mhz×128bits,DDR3-SDRAM等效为800Mhz×16bits。

图像数据以12路×25MHz×10bits数据输入,等效为25MHz-120bit位宽的图像数据;因此,36路图像数据等效为120bits,75MHz图像数据输入,按照SDRAM效率80%计算,满足SDRAM的数据速率要求。

首先,通过FPGA内部RAM对36路图像数据缓存,RAM容量为256,当缓存数据量达到T

SDRAM的写操作时需要插入定时刷新时序,因此,根据SDRAM即时写入数据速率控制双口RAM的读速率;通过RAM数据的读出量B,控制SDRAM写操作的启动和停止。

双口RAM数据为循环写入(先入先出),即当缓存数据量A达到RAM的最大值T

通过cameralink接口,将图像数据从SDRAM中读出,传输至快视设备,经验证,该图像数据能够完整传输,无数据覆盖、数据丢失等情况,该方法实用有效。外景成像图像如图4所示。

以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

- 一种大面阵CMOS探测器异常像元检测及实时替换方法

- 基于CMOS IC的探测器阵列和TDI-CMOS线阵探测器的叠层结构