电压到延迟前置放大器阵列的增益失配校正

文献发布时间:2024-01-17 01:27:33

背景技术

模数(A/D)转换器(ADC)可以用于生成表示模拟信号电平的数字代码。射频(RF)采样接收器可以用于接收高频模拟信号并对其进行数字化。用于对射频采样接收器中的信号进行数字化的模数转换器可能需要以高速运行。美国专利申请公开号2012/0212358(Shi等人)、2015/0244386(El-Chammas)、2019/0007071(Nagarajan等人)和2019/0280703(Naru等人)中描述了模数转换器。

一些模数转换器具有一个或多个电压到延迟(voltage-to-delay,V2D)部件,并且至少部分地在延迟域中运行。美国专利号10,673,452(Soundararajan等人)、10,673,456(Dusad等人)和10,673,453(Pentakota等人)中描述了基于延迟的模数转换器。美国专利号10,673,452、10,673,456和10,673,453的全部披露通过引用并入本文。此外,以下表1中确定的五项美国专利申请的全部披露通过引用并入本文。如果需要,基于延迟的模数转换器可以以高速运行,同时减少了面积和功率需求。

表1

发明内容

本披露涉及一种使用模数转换器系统的方法,该方法包括:接收与输入电压和已知电压中的一个相对应的采样电压;使前置放大器基于该采样电压生成输出信号;基于这些输出信号生成第一信号和第二信号;使延迟解析延迟到数字后端生成表示该第一信号和该第二信号的接收顺序的单比特数字信号;以及基于该单比特数字信号来调整这些前置放大器中的一个或多个。

根据本披露的一个方面,该模数转换器系统包括校准引擎/处理器,以用于在校准期间建立已知校准电压,用于在校准期间控制折叠多路复用器并超控其输出,以及用于调整一个或多个前置放大器的性能。该校准引擎/处理器可以包括数字处理器。然而,本披露不应局限于本披露的这些方面。

本披露还涉及一种模数转换器系统,该模数转换器系统包括:电压到延迟前端,该电压到延迟前端用于接收与输入电压和已知电压中的一个相对应的采样电压,其中,该前端包括用于基于该采样电压生成输出信号的前置放大器,以及连接至该前置放大器的用于基于来自这些前置放大器中的一个的信号来生成第一延迟信号和第二延迟信号的折叠多路复用器;以及延迟解析延迟到数字后端,该延迟解析延迟到数字后端连接至该前端,用于接收来自该前端的该第一延迟信号和该第二延迟信号,其中,该后端包括用于比较第一输入和第二输入的时序的延迟比较器,以及连接至该折叠复用器的用于通过将第三延迟信号与该第一延迟信号和该第二延迟信号多路复用来生成该第一输入和该第二输出的延迟多路复用器。

本披露还涉及一种操作模数转换器系统的方法,该方法包括:使基于延迟的前置放大器阵列接收与输入电压和已知电压中的一个相对应的采样电压,其中,该前置放大器阵列包括具有不同阈值电压的前置放大器;使这些前置放大器基于该采样电压来生成输出信号;基于这些输出信号生成第一信号和第二信号,并将该第一信号和该第二信号施加到延迟解析延迟到数字转换器后端,该延迟解析延迟到数字转换器后端包括延迟比较器;使该延迟比较器生成表示该第一信号和该第二信号的接收顺序的单比特数字信号;使该延迟比较器向相继延迟比较器传输残余延迟信号;以及使校准引擎/处理器向这些前置放大器传输信号,以基于该单比特数字信号来调整这些前置放大器中的一个或多个。

附图说明

图1是基于延迟的模数转换器系统的示例的框图;

图2是图1的模数转换器系统的一部分的框图;

图3是图1的模数转换器系统的阈值校正和饱和检测过程的时序图;

图4是图1的模数转换器系统的前置放大器的延迟输出随电压输入而变化的曲线图;

图5和图6分别是对前置放大器阵列使用共用电流调整和对前置放大器中的每一个使用电容调整的增益最大化过程的流程图;

图7是图1的模数转换器系统的前置放大器的增益随电压输入而变化的曲线图,示出了整个前置放大器范围内的增益;

图8是图1的模数转换器系统的各个前置放大器的增益归一化过程的流程图;

图9是用于对图1的模数转换器系统的整个前置放大器阵列的增益进行归一化的过程的流程图;

图10是用于图1的模数转换器系统的前置放大器阵列的可变共用电流设备的电路图;

图11是图1的模数转换器系统的前置放大器的可变电容设备的电路图;

图12是电流突跳过程的时序图;

图13是使用或操作图1的模数转换器系统的方法的流程图;

图14是用于图1的模数转换器系统的前置放大器阵列和折叠延迟多路复用器的框图;

图15是用于图1的模数转换器的后端延迟到数字转换器的框图;

图16是用于图1的模数转换器系统的与符号输出电路和延迟输出电路合并的比较器电路的示例的电路图;

图17和图18是与符号输出电路和延迟输出电路合并的比较器电路的其他示例的电路图;

图19是图示了分别由图1的模数转换器系统的与门和延迟比较器生成的与门延迟和比较器延迟的曲线图,其中,与门延迟和比较器延迟是输入信号延迟的函数;

图20是图示了输出信号延迟随图19的输入信号延迟而变化的曲线图。

在整个附图中,相似的元件由相似的附图标记和其他字符指代。

具体实施方式

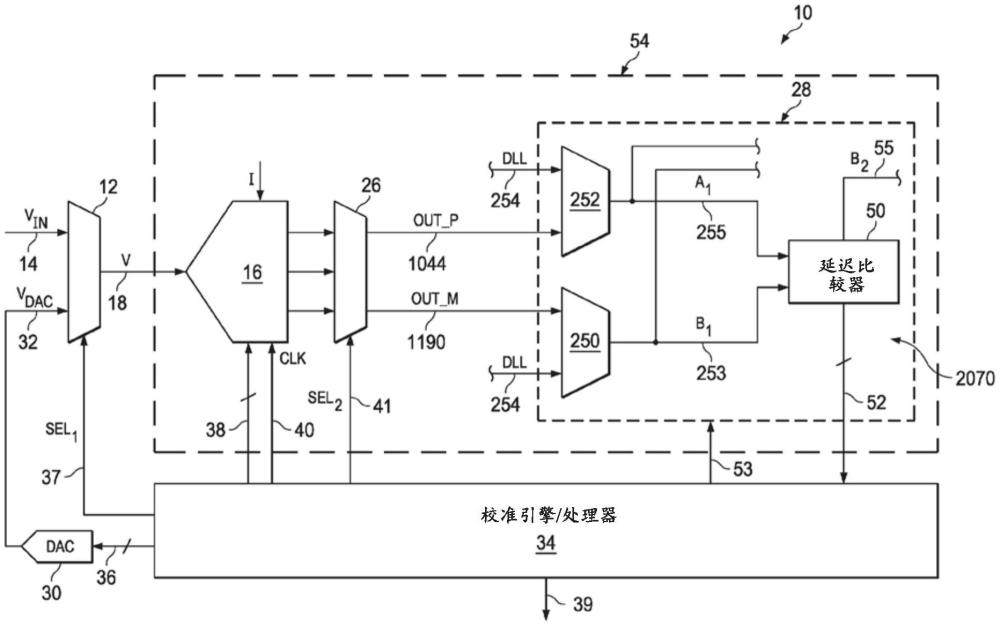

图1图示了根据本披露构造的模数转换器系统10。模数转换器系统10具有用于接收输入线路14上的输入电压V

如图2所图示的,前置放大器阵列16具有第一前置放大器20和第二前置放大器22至第N前置放大器24(N=3、4、5或更多)。在操作中,前置放大器20、22和24基于采样电压V与施加到前置放大器20、22和24的阈值电压TH

模数转换器系统10(图1)还具有折叠延迟多路复用器26,该折叠延迟多路复用器接收输出信号OUT_M

折叠延迟多路复用器26的折叠电路的示例在图14中进行了图示,并且在下面进行了更详细的描述。延迟多路复用器26是延迟域(其中,信息由延迟表示)中的数据选择器。延迟多路复用器26从若干对延迟信号中选择一对延迟信号,并输出具有与所选择的一对信号相对应的延迟的单对信号。所图示的延迟多路复用器26使用逻辑门来执行如图14所图示并如下面更详细描述的折叠过程。

在图2所图示的示例中,如果采样电压V更接近第一前置放大器20的阈值电压TH

另一方面,如果采样电压V更接近第二前置放大器22的阈值电压TH

模数转换器系统10(图1)还具有用于接收和处理线路253和255上的输入信号的模数转换器后端28,其中,输入信号(253和255)至少部分地基于延迟信号OUT_M和OUT_P。模数转换器后端28生成在适合的线路52上被传输到校准引擎/处理器34的数字信号(代码)。针对模数转换器后端28的时序控制由校准引擎/处理器34在另一适合的线路53上提供。

模拟到延迟转换器后端28具有第一延迟比较器50,其用于在线路52上生成单比特数字信号,以指示延迟信号OUT_M和OUT_P中的哪个信号(或线路253和255上的信号中的哪个信号)首先到达延迟比较器50。线路52上的数字信号表示延迟比较器50处接收到信号(253和255)的顺序。残余延迟信号在适合的线路55上从第一延迟比较器50输出到第二延迟比较器(图1和图2中未图示出)。延迟比较器50、第二延迟比较器和相继比较器的结构和操作的示例在图15至图18中进行了图示。

在所图示的配置中,延迟解析后端28包括基于延迟的级的级联。第一基于延迟的级2070(图15)通过适合的线路55连接至相继的基于延迟的级。在图15所示的示例中,所有基于延迟的级都是单比特级。根据本披露的其他方面,延迟解析后端28可以具有一个或多个多比特级。例如,一个或多个基于延迟的级可以是两比特级和/或一个或多个基于延迟的级可以是四比特级。例如,第一级2070可以是单比特级,而相继的第二、第三和第四级可以分别是四比特级、单比特级和两比特级,并且第四级之后剩余的基于延迟的级可以全部都是单比特级。每个级可以具有一个或多个延迟比较器。因此,模数转换器后端28可以具有两个、三个、四个或更多个延迟比较器。由延迟比较器生成的数字信号被校准引擎/处理器34用来确定采样电压V的值的较低有效位。

在校准阶段期间,已知电压V

在模数转换器系统10的操作阶段期间,输入电压V

在图1所图示的示例中,在操作阶段期间,控制线路37上的选择信号SEL

前置放大器阵列16被配置为生成在适合的线路38(图1)上被传输到校准引擎/处理器34的数字信号。这些数字信号可以用来确定采样电压V的值的一个或多个最高有效位,并识别前置放大器阵列16内的最相关前置放大器(即,生成最高有效延迟信息的前置放大器)。电压到延迟前置放大器阵列16在校准引擎/处理器34所生成的适合的定时信号CLK(图3)的控制下运行。定时信号CLK在适合的线路40上被传输到前置放大器20、22和24(图2)。

在图3所图示的示例中,当定时信号CLK为高电平(“1”)时,模数转换器系统10处于活动阶段A,并且延迟信号OUT_M和OUT_P可以具有高电平分量70和低电平分量72。当定时信号CLK为低电平(“0”)时,模数转换器系统10处于重置阶段R,并且延迟信号OUT_M和OUT_P的所有分量都为低电平(72)。在操作阶段,延迟信号OUT_M和OUT_P的前沿的时序与来自阵列16内的最相关前置放大器的输出信号的前沿的时序相对应。在每个重置阶段R开始时,(线路40上的)定时信号CLK使前置放大器20、22和24重置。因此,延迟信号OUT_M和OUT_P在每个重置阶段R内都为低电平(72)。

折叠延迟多路复用器26(图2)在线路41上的来自校准引擎/处理器34的一个或多个信号(包括第二选择信号SEL

总之,模数转换器系统10具有电压到延迟前置放大器阵列前端(包括前置放大器16和多路复用器26),之后是延迟-解析模数后端28。前端16、26和后端28的一个或多个元件可以集成到集成电路(IC)54中和/或根据各种半导体工艺和/或其他工艺而形成在单个半导体管芯(图中未示出)上或上方。导电线路可以是形成在半导体管芯上的绝缘层中的金属结构、形成在半导体管芯中的掺杂区域(其可以是硅化的)、或形成在半导体管芯上方的掺杂半导体结构(其可以是硅化的)。用于实施示例实施例中的电路结构的晶体管可以是双极结型晶体管(BJT)或金属氧化物半导体场效应晶体管(MOSFET),并且可以是n型或p型。集成设备和元件可以还包括电阻器、电容器、逻辑门、以及为了清楚起见而未在附图中示出的其他适合的电子设备。

第一基于延迟的级2070(图15)(通过线路253和255)连接至折叠延迟多路复用器26。相继的基于延迟的级(通过线路55和57)连接至第一基于延迟的级2070。在操作中,模数后端28基于所选择的延迟信号来生成数字信号,并且在校准阶段,所图示的前置放大器20、22和24中的一个或多个基于由模数后端28输出的数字信号来进行调整。然而,本披露不应局限于附图中所图示以及通过本文的示例所描述的配置。

如果需要,模数转换器系统10可以以高速(例如,>3GSPS)和高性能(例如,>55dBFS)运行。此外,如果需要,模数转换器系统10可以消耗比传统的基于流水线的模数转换器更少的功率。如果需要,根据本披露所构造的基于延迟的模数转换器系统可以用来克服传统模数转换器所特有的在速度、面积和功率方面的障碍。

阵列16内的前置放大器20、22和24(图2)由于各种因素而具有不同的增益,这些因素可以包括设计、工艺、输入电压V

阈值电压校准可以通过向阵列16内的最相关前置放大器的阈值电压施加适合的偏移电压(具有n1、n2、n3…的值)来实现。然后,使第一延迟比较器50的数字输出(在线路52上)发生转换(即,从高电平(“1”)变为低电平(“0”),反之亦然)的偏移量被用作校准最相关前置放大器的偏移量。图3所图示的示例假设第一前置放大器20是阵列16内的最相关前置放大器(即,假设第一前置放大器20的阈值电压TH

如上面所指出的,在校准阶段期间,选择信号SEL

在图3所图示的示例中,当偏移量的值为0(如区域300所示)时,因为第二延迟信号OUT_P的前沿366与第一延迟信号OUT_M的前沿368重合,所以线路52上的比较器输出转换为高电平/低电平。因此,在图3所图示的示例中,第一前置放大器20的阈值电压TH

在不同的示例中,如果确定施加n1或n2的偏移电压值会使第一前置放大器20转换第一延迟比较器50的数字输出(52),则将第一前置放大器20的阈值电压TH

在前置放大器20、22和24的阈值电压TH

阈值电压校正过程和这三个调整过程都可以通过观测第一延迟比较器50(图2)在线路52上的单比特输出来执行。除下面所描述的增益测量过程外,线路52上的输出在第二延迟信号OUT_P的上升沿先于第一延迟信号OUT_M的上升沿时为高电平“1”,这进而表明采样电压V大于最相关前置放大器的阈值。如下面结合图14所描述的,折叠选择最相关前置放大器,即,其阈值电压最接近采样电压V的前置放大器。

前置放大器20、22和24中的每一个的传递函数(电压差到延迟)都是非线性的。给定前置放大器的延迟输出是其两个输出的上升沿之间的时序差。在图4中以图形方式表示的示例中,其中第一前置放大器20是阵列16中的最相关前置放大器,作为采样电压V的函数的第一前置放大器20的延迟输出可以如下计算:延迟输出=D+g1*V

再次参考图3,阵列16中的每个前置放大器在定时信号CLK的控制下都具有其中前置放大器被重置的重置阶段R和其中前置放大器提供输出的活动阶段A。重置阶段R分别在时钟信号CLK下降和上升时开始和结束。活动阶段A分别在时钟信号上升和下降时开始和结束。相关延迟信息是来自最相关前置放大器的两个输出的上升沿之间的时间差。

当最相关前置放大器的增益大到使来自该最相关前置放大器的输出信号的较晚到达的上升沿在活动阶段A结束之前没有到达时,就会发生饱和条件(SAT)。饱和条件(SAT)的示例在图3中在区域366中进行了图示,其中,V

图5和图6中图示了用于使各个前置放大器的增益最大化的两种不同的过程(过程一)。每个过程的目的都是不在任何前置放大器中产生饱和条件的情况下使阵列16内的每个前置放大器的增益最大化。通常,减小流过前置放大器的电流会使前置放大器的增益增大。因此,在电流驱动的过程(图5)中,校准引擎/处理器34在不使第一前置放大器20(n=1;步骤100)处于饱和条件的情况下,使所有前置放大器20、22和24的共用电流都被设置为可能的最低值(步骤102)。

饱和检查(步骤102)可以通过逐步减小共用电流直到识别出饱和条件、然后将共用电流设置为紧接在识别出饱和条件之前施加的值来执行。在特定共用电流下不存在饱和条件可以通过确认来自最相关前置放大器的输出在该前置放大器的整个电压范围内在整个对应活动阶段A内都不是低电平(“0”)来确定。如果在前置放大器的电压范围内的任何一点,前置放大器的任何一个输出在整个活动阶段A内都为低电平,则前置放大器在该共用电流值下处于饱和条件。

在步骤102之后,当采样电压V在第二阈值电压TH

在每次增益减小之后(即,在每次经过步骤106之后),检查饱和情况(步骤104),并且如果饱和检查的结果表明需要进一步减小增益才能进行到下一个前置放大器(步骤104为“否”,并且通过进行步骤112使n的值递增),则进一步减小增益(电流增大)(步骤106)。当所有前置放大器的增益都已调整,也就是说,当n=N时,可以结束图5所图示的过程(步骤114)。

对于本文所描述的类型的前置放大器,延迟(增益)=C*V/I,其中,C是电容,I是电流,并且V是电压(固定为VDD)。因此,增益随着电流的减小而增大,并且增益随着电容的增大而增大。在图示的配置中,电流I在所有前置放大器20、22和24(图2)之间都是共用的。因此,如果电流I改变,则所有前置放大器20、22和24的增益都会改变。另一方面,在所图示的配置中,各个前置放大器20、22和24的电容可以彼此不同。如果一个前置放大器的电容改变,则仅这一个前置放大器的增益改变,而其他前置放大器的增益不变。

各种适合的电路和设备都可以用来调整共用电流I。在所图示的配置中,共用电流I的调整可以由可变电流电路600(图10)进行,该可变电流电路具有并联的电流源602、604、606和608的阵列,除了其中一个电流源602之外,所有电流源都有自己的开关610、612和614。在默认状态下,第一开关610可以闭合,使得只有第一电流源602和第二电流源604是活动的。为了增大共用电流I,可以在校准引擎/处理器34的控制下闭合其他开关612和614中的一个或多个,以激活其他电流源606和608。为了减小默认状态下的共用电流I,可以在校准引擎/处理器34的控制下断开第一开关610,以停用第二电流源604。

图6所图示的过程与图5所图示的共用电流过程相同,不同之处在于图6的过程涉及各个前置放大器的电容。通常,增大前置放大器的电容会使前置放大器的增益增大。因此,图6的过程不是使所有前置放大器20、22和24的共用电流被设置为可能的最低值而不让第一前置放大器20处于饱和条件(步骤102),而是使第一前置放大器20的电容被设置为可能的最大值而不让第一前置放大器20处于饱和条件(步骤200)。步骤200中的电容设置可以通过使用图2所图示的测量系统进行的测量来递增地进行,直到电容处于使前置放大器20即将饱和的值。

各种适合的电路和设备都可以用来调整前置放大器20、22和24中的每一个的电容。在所图示的配置中,电容的调整可以由可变电容电路700(图11)进行,该可变电容电路具有并联的电容元件702、704、706和708的阵列,除了其中一个电容元件702之外,所有电容元件都有自己的开关710、712和714。在默认状态下,第一开关710可以闭合,使得只有第一电容元件702和第二电容元件704是活动的。为了增大包含可变电容电路700的前置放大器的电容,可以在校准引擎/处理器34的控制下闭合其他开关712和714中的一个或多个,以激活其他电容元件706和708。为了减小默认状态下的电容,可以在校准引擎/处理器34的控制下断开第一开关710,以停用第二元件704。在所图示的配置中,前置放大器20、22和24中的每一个都有单独的可变电容电路700。

在图6的(基于电容的)过程中,可以以与图5的(基于共用电流的)过程相同的方式来执行饱和检查(步骤104),但图6的过程不是增大所有前置放大器的共用电流,而是减小被发现处于饱和条件的各个前置放大器的电容(步骤104之后的步骤202)。在每个前置放大器内,需要检查负区和正区是否饱和。图6的流程图仅示出了要对一个前置放大器执行的步骤。对前置放大器20、22和24中的每一个重复图6的过程。

再次参考图2,可以使用两个延迟多路复用器250和252以及承载延迟锁定环信号DLL的线路254来测量前置放大器的增益。第一延迟多路复用器250接收第一延迟信号OUT_M和延迟锁定环信号DLL。第二延迟多路复用器252接收第二延迟信号OUT_P和延迟锁定环信号DLL。延迟多路复用器250和252可以由来自校准引擎/处理器34的适合信号控制。为了测量最相关前置放大器的增益,可以使用图2所图示的测量系统相对于延迟锁定环信号DLL分别测量这两个延迟信号OUT_M和OUT_P的前沿的上升时间。上升时间在时间上间隔越远,增益就越大。

在图2所图示的测量系统中,线路254上的延迟锁定环信号DLL包含由延迟锁定环(未图示出)生成的具有高分辨率(该分辨率可以为例如约1ps)的延迟。在操作中,为了测量第二延迟信号OUT_P的时序,会将第二延迟信号OUT_P传输到延迟比较器50(经由多路复用器252),而将线路254连接至比较器50(经由多路复用器250)而不是第一延迟信号OUT_M。线路254中的延迟被递增地增大,直到比较器50发生转换。线路254中使延迟比较器50(在线路52上)发生转换的延迟是第二输出信号OUT_P的延迟的度量。

采取类似的方法来测量第一延迟信号OUT_M的延迟。将第一延迟信号OUT_M传输到延迟比较器50(经由多路复用器250),而将线路254经由线路255连接至比较器50(经由多路复用器252)而不是第二延迟信号OUT_P。线路254中的延迟被递增地增大,直到比较器50发生转换。在这种情况下,线路254中使延迟比较器50发生转换的延迟是第一输出信号OUT_M的延迟的度量。然后,根据两个所测得的延迟如下计算前置放大器20的增益:增益=delay_out/(V–TH

在本披露的上下文中,还有测量增益的其他方式。例如,可以将已知校准电压设置为Vth+X,而不是使用延迟锁定环(DLL)线路254,其中,X使得前置放大器仍然是相关前置放大器。然后,由延迟解析后端28输出的数字代码本身就是前置放大器增益的表示。

参考过程二,N个前置放大器20、22和24中的每一个都有两个区,其中,如果采样电压V处于某个前置放大器的这些区中的一个内,则该前置放大器是最相关前置放大器。对于每个前置放大器,采样电压V在这些区中的一个中大于阈值电压,并且采样电压在另一个区中小于阈值电压。因此,前置放大器阵列16具有2N个区。图7示意性地表示了前置放大器的增益随采样电压V的变化。在由实线170和172表示的不相等条件下,前置放大器在采样电压V小于阈值电压TH时的增益小于前置放大器在采样电压V大于采样电压V时的增益。

通过使阈值电压TH改变到另一个值TH

增益归一化过程在图8中进行了图示。所图示的过程包括对一个前置放大器所执行的步骤。对其他前置放大器中的每一个重复该过程。因此,从第一前置放大器20开始(步骤400),使用图2所图示的测量系统来测量前置放大器20的两个区的增益。如果这两个增益之间的差Gain_Diff大于预定限制(即,太大)(步骤402为“是”),则改变前置放大器20的体电压,使得前置放大器20的增益差小于或等于预定限制(步骤404)。可以利用使用图2所图示的测量系统进行的测量递增地改变体电压,直到前置放大器20的增益差小于或等于预定限制。可以通过例如改变前置放大器的阈值电压来改变体电压。然后,对其他前置放大器22和24中的每一个重复该过程。如在本文所使用的,术语“体电压”与“背栅电压”同义。

图9图示了用于对整个前置放大器阵列16的增益进行归一化的迭代算法方法(过程三)。如果需要,该方法可以用于通过识别具有最小增益的前置放大器,然后增大该前置放大器的增益(如果可能的话,考虑其他约束)来使模数转换器系统10的性能最大化。一个这样的约束是避免饱和条件。

在操作中,可以使用图2所图示的测量系统来确定阵列16内的所有前置放大器的增益,使得可以识别出阵列16内具有最小增益的前置放大器和阵列内具有最大增益的前置放大器。然后,可以通过确定最高增益与最低增益之间的差是否在预定限制内来开始增益归一化过程(步骤500)。如果差在预定限制内(步骤500为“是”),则前置放大器阵列的增益范围是可接受的,并且所述该完成(步骤502)。如果增益范围是不可接受的(步骤500为“否”),则选择具有最小增益的前置放大器(步骤504),并向所选择的前置放大器提供电流突跳,并且增大前置放大器的电容以增大其增益(步骤506)。

施加电流突跳通过使前置放大器远离饱和状态而改善了前置放大器的响应时间。如果不带任何电流突跳的前置放大器接近饱和,则电容(增益)的任何进一步增大都会导致饱和。由于电流突跳使前置放大器远离饱和,因此可以增大前置放大器的电容(增益)而在不会产生饱和条件。电流突跳本身并不会改变前置放大器的增益。如图12所图示的,第一延迟信号OUT_M的前沿与第二延迟信号OUT_P的前沿之间的时序差d在没有电流突跳和有电流突跳的情况下都是相同的。然而,电流突跳使得能够通过使前置放大器远离饱和(即,通过在每个活动阶段A内使第一延迟信号OUT_M和第二延迟信号OUT_P的前沿向前移动(通过在图12中向左移动))来增大增益。因此,电流突跳允许在前置放大器饱和之前有更高的电容设置。用于向前置放大器20、22和24施加电流突跳的时钟信号CLK

如果电流突跳和电容增大在所选择的前置放大器内产生了饱和条件(步骤508为“是”),则通过减小所选择的前置放大器的电容来减小其增益(步骤510)。

然后,如果所选择的前置放大器不再具有最小增益,则过程返回到步骤500(步骤512为“否”)。但是,如果所选择的前置放大器在前置放大器阵列内仍具有最小增益(步骤512为“是”),那么除非在不产生饱和条件的情况下不能减小电容(步骤516为“是”)(在这种情况下过程结束(步骤502)),否则通过减小在阵列16中具有最大增益的前置放大器的电容来减小其增益(步骤514),并且过程返回到步骤500。

根据本披露,可能的情况是,即使在施加了电流突跳并且通过增大所选择的前置放大器的电容来最大化其增益(步骤506)之后,在对阵列16内的所有前置放大器排序之后,所选择的前置放大器仍具有最小增益。在这种情况下(步骤512为“是”),选择具有最大增益的前置放大器,并且如果可能的话,在不产生饱和条件的情况下,通过减小其电容设置来减小其增益(步骤514)。在每次改变增益之后(步骤506、步骤514),进行饱和检查以确保不存在饱和条件(步骤508和步骤516)。

当所有前置放大器增益都在限制内(步骤500为“是”)、最小增益前置放大器的增益不能增大并且最大增益前置放大器的增益不能减小(步骤516为“是”)时,或者在可编程的迭代次数之后(在所图示的示例中,当m=M时),可以结束图9中所图示的过程(步骤502)。如果增大增益会导致前置放大器饱和,则不应这样做。如上面所描述的,饱和检查可以通过确认延迟信号OUT_M和OUT_P的较晚到达的边沿在整个所考虑的前置放大器的范围在活动区域A内是否上升来执行。

图13中图示了使用或操作模数转换系统的方法。该方法包括接收与输入电压V

参考图13,所图示的方法包括使延迟解析模数后端28生成表示第一信号OUT_M和第二信号OUT_P的接收顺序的单比特数字信号(在线路52上)(步骤806),以及基于该单比特数字信号(在线路52上)来调整前置放大器20、22和24中的一个或多个(步骤808)。根据本披露的一个方面,前置放大器20、22和24的增益和范围可以被调整,并且优选地在整个前置放大器阵列16中是匹配的。在前置放大器20、22和24已校准之后,可以调整前置放大器20、22和24的最大增益或经改善的增益,然后针对整个阵列16的增益失配进行校正,在所有这些的同时避免饱和条件。

如图14所图示的,举例来说,前置放大器阵列16可以具有第一前置放大器20、第二前置放大器22、第三前置放大器1056和第四前置放大器24(N=4;TH

在操作中,前置放大器20、22、1056和24所产生的延迟信息由第一或门1138、第二或门1140、第三或门1142、第四或门1144和第五或门1146、以及第一与门1148、第二与门1150、第三与门1152、第四与门1154和第五与门1156处理。该处理使前置放大器所生成的信号被折叠为包含所有关注的信息的单对信号。如果需要,图14中所图示的折叠电路可以如美国专利号10,673,456中所示和所描述的那样构造和操作。在图14所图示的配置中,或门1138、1140、1142、1144和1146以及与门1148、1150、1152、1154和1156是折叠延迟多路复用器26的元件,并且在操作阶段在折叠延迟多路复用器26内被采用。第一输出线路1102中的第一个线路连接至第一或门1138和第一与门1148的输入端,并且第二输出线路1110中的第一个线路连接至第一或门1138和第一与门1148的输入端。同样地,其他前置放大器20、22和1056的第一和第二输出线路1104、1106、1108、1112、1114和1116连接至相应的第二或门1140、第三或门1142和第四或门1144以及第二与门1150、第三与门1152、第四与门1154的输入端。

由第一到第四或门1138、1140、1142和1144(在导电线路1158、1160、1162和1164上)生成的输出信号被输入到第五与门1156,并且由第一到第四与门1148、1150、1152和1154(在导电线路1180、1182、1184和1186上)生成的输出信号被输入到第五或门1146。在各自的情况下,由或门1138、1140、1142、1144和1146生成的输出信号的时序与到达或门1138、1140、1142、1144和1146的相应输入端的第一个信号的时序相对应,而由与门1148、1150、1152、1154和1156生成的输出信号的时序与到达与门1148、1150、1152、1154和1156的相应输入端的最后一个信号的时序相对应。

在操作中,前置放大器阵列16生成具有早期上升沿和晚期上升沿的前置放大器输出。当系统10处于校准阶段时,折叠延迟多路复用器26在选择信号SEL

在操作阶段,第五与门1156在导电线路1044上生成保留了较早到达的信号中最晚到达的信号的时序的信号(OUT_P),并且第五或门1146在导电线路1190上生成保留了较晚信号中最早到达的信号的时序的信号(OUT_M)。美国专利号10,673,456中描述了一种操作图14所图示的折叠电路的方法。美国专利号10,673,456中还描述了可以在系统10中采用的其他折叠电路以及操作这样的电路的方法。

图15图示了用于系统10的后端延迟到数字转换器2048。在所图示的配置中,延迟到数字转换器具有三个或更多个级2070、2072和2074,各个级具有相应的与门2076、2078和2080以及延迟比较器50、2084和2086。请注意,所图示的与门仅仅是根据本披露可以采用的逻辑门的示例。如果需要,本披露可以被实施为具有或不具有与门、和/或具有或不具有除与门之外的其他门。

在所图示的配置中,第二与门2078和第三与门2080与第一与门2076基本上相同,并且第二延迟比较器2084和第三延迟比较器和2086与第一延迟比较器50基本上相同。导电输出线路255和253两者都耦合到第一与门2076的输入端。而且,导电线路255中的第一个导电线路耦合到第一延迟比较器50的第一输入端2092,并且导电线路253中的第二个导电线路耦合到第一延迟比较器50的阈值输入端2094。

始于第一与门2076的输出线路57电耦合到第二与门2078的输入端中的一个输入端、以及第二延迟比较器2084的第一输入端2092。始于第一延迟比较器50的导电线路55电耦合到第二与门2078的输入端中的另一个输入端、以及第二延迟比较器2084的阈值输入端2094。以类似的方式,始于第二与门2078的输出线路2088电耦合到第三与门2080的输入端中的一个输入端、以及第三延迟比较器2086的第一输入端2092,并且始于第二延迟比较器2084的导电线路2090电耦合到第三与门2080的输入端中的另一个输入端、以及第三延迟比较器2086的阈值输入端2094。

如果需要,由第二级2072和第三级2074创建的模式可以继续用于第四级或预期数量的附加级。每一相继级的与门和延迟比较器与第二级2072和第三级2074的与门2078和2080以及延迟比较器2084和2086基本上相同,并且其电耦合到前一级的与门和延迟比较器的方式与第三与门2080和第三延迟比较器2086电耦合到第二与门2078和第二延迟比较器2084的方式相同。

在操作中,信号A

特别地,对于与门2076、2078和2080中的每一个,信号A

同时,信号A

对于任何给定级,从比较器所生成的延迟7102中减去与门所生成的延迟7100得到输出信号延迟T_OUT(图20)。当输入信号延迟T_IN的绝对值小于阈值延迟T_THRES时,输出信号延迟T_OUT为正值(这意味着由相应的延迟比较器50、2084和2086生成的信号B

在操作中,第一延迟比较器50在第一数字线路52上向校准引擎/处理器发出第一符号信号(“1”或“0”)。第一符号信号是基于信号A

然后,第二与门2078和第二延迟比较器2084生成信号A

由于信号A

现在参考图16,延迟比较器50具有比较器电路2083,该比较器电路具有第一晶体管2400、第二晶体管2402、第三晶体管2404、第四晶体管2406、第五晶体管2408、第六晶体管2410、第七晶体管2412和第八晶体管2414。延迟比较器50的时序由导电线路2122上的来自被施加到第一晶体管2400和第四晶体管2406的栅极的时钟的信号来控制。线路255和253上的第一信号A

比较器电路2083的第一导电线路2416和第二导电线路2418经由相应的第三导电线路2422和第四导电线路2424电连接至符号输出电路2420。如图16所图示的,符号输出电路2420与比较器电路2083合并。符号输出电路2420具有第一晶体管2426、第二晶体管2428、第三晶体管2430和第四晶体管2432。第三导电线路2422分别电连接至符号输出电路2420的第一晶体管2426和第二晶体管2428的栅极和源极,而第四导电线路2424分别电连接至符号输出电路2420的第一晶体管2426和第二晶体管2428的源极和栅极。

在操作中,当延迟比较器50由线路2122上的时钟信号启用时,在符号输出电路2420内的线路52上生成符号信号。该符号信号在线路52上被转发到校准引擎/处理器34,并且表示输出信号A

第三导电线路2422和第四导电线路2424还电连接至延迟输出电路2450。如图16所图示的,延迟输出电路2450与比较器电路2083合并。延迟输出电路2450具有第一晶体管2442、第二晶体管2444和第三晶体管2446。第三导电线路2422分别电连接至延迟输出电路2450的第一晶体管2442和第二晶体管2444的栅极和源极,而第四导电线路2424分别电连接至延迟输出电路2450的第一晶体管2442和第二晶体管2444的源极和栅极。

在操作中,在线路55上生成延迟信号B

图17中图示了无时钟延迟比较器50A。如果需要,可以在系统10中使用无时钟延迟比较器50A来代替图16所图示的延迟比较器50。无时钟延迟比较器50A类似于图16所图示的延迟比较器50,不同之处在于(1)无时钟延迟比较器50A具有比较器电路2083A,该比较电路使用了施加到第一输入端2092和阈值输入端2094的信号A

如图17所图示的,比较器电路2083A具有第一额外晶体管2452和第二额外晶体管2454。第一输入信号A

同时,第一输入信号A

反相信号-A

如图17所图示的,比较器电路2083A的第一导电线路2416和第二导电线路2418还经由第三导电线路2422和第四导电线路2424电连接至延迟输出电路2450A。延迟输出电路2450A被合并在无时钟延迟比较器50A内。延迟输出电路2450A具有额外晶体管2464。在操作中,当无时钟延迟比较器50A被启用时,在线路55上生成延迟信号B

尽管图17所图示的合并的无时钟比较器50A具有P势垒配置,但图18所图示的第二合并的无时钟比较器50B具有N势垒配置。第二无时钟延迟比较器50B类似于图17所图示的无时钟延迟比较器50A,不同之处在于(1)使用了非反相输入信号A

如图18所图示的,与比较器电路2083B合并的反相符号输出电路2420B具有第一晶体管2480、第二晶体管2484、第三晶体管2482、第四晶体管2486、第五晶体管2488和第六晶体管2490。第五晶体管2488和第六晶体管2490的源极分别电连接至第三导电线路2422和第四导电线路2424。第五晶体管2488和第六晶体管2490的栅极分别电连接至第四导电线路2424和第三导电线路2422。在操作中,在反相符号输出电路2420B内的线路52B上生成反相符号信号。

线路52B上的反相符号信号由反相器门2468中的一个反相器门反相,以在线路52上生成被施加到校准引擎/处理器34(图18中未图示出)的非反相符号输出信号。非反相符号输出信号表示输入信号A

第一导电线路2416和第二导电线路2418分别经由第三导电线路2422和第四导电线路2424电连接至反相延迟输出电路2450B。反相延迟输出电路2450B具有第一晶体管2492、第二晶体管2494、第三晶体管2496和第四晶体管2498。在操作中,当第二无时钟延迟比较器50B被启用时,在线路55B上生成反相延迟信号-B

如图18所图示的,反相延迟输出电路2450B的第三晶体管2496和第四晶体管2498的源极分别电连接至第三导电线路2422和第四导电线路2424。反相延迟输出电路2450B的第三晶体管2496和第四晶体管2498的栅极分别电连接至第四导电线路2424和第三导电线路2422。反相延迟输出电路2450B的操作由施加到反相延迟输出电路2450B的第二晶体管2494和第一晶体管2492的栅极的输入信号A

本披露描述了许多有利的特征。除其他事项外,还描述了一种算法,前置放大器的两个区内的增益可以通过所述算法进行归一化。增益归一化可以通过改变体电压来执行。此外,还描述了一种优选地使用电流突跳来减少响应时间以对整个阵列16的增益进行归一化的迭代方法。此外,本文中还描述了一种用于检测电压到延迟前置放大器的饱和条件的技术。

本披露中所描述的有利特征涉及仅使用单比特输出来执行所有校准过程和调整过程。此外,本披露描述了一种通过(除其他外)使用延迟锁定环生成的信号测量输出信号的延迟来计算前置放大器的增益的过程。本披露还描述了一种通过电流调整和电容调整的组合来使前置放大器的增益最大化的方法。

本文所描述的模数转换器系统10可以被结合到具有高运行速度和高性能以及低功耗的射频采样模数转换器中。系统10可以被结合到高度集成的基于射频采样的收发器中,以在无线基础设施、特别是更高带宽的多频带应用中使用。除其他事项外,根据本披露构造的设备可以具有低功耗和小面积需求。

通常,可以通过过度设计设备来减少某些设备中的非线性。然而,过度设计的方法往往会不合期望地增加(有时会大大地增大)面积和功率需求,尤其是为了适应宽的温度范围。并且过度设计在较低的工艺节点处可能是不可扩展的,因为在这样的节点处的模拟域往往更加非线性。此外,通常可以使用出厂微调过程来执行校准。然而,可能难以对模数设备的后级进行微调,其中,这样的级以高度非线性的方式运行。尤其是在后级中,可能无法按出厂微调过程的需要跟踪变化。

本披露代表了对通过过度设计来减少非线性的概念的改善,因为过度设计可能会大大增大面积和功率以支持更宽的温度,并且在模拟处理更加非线性的较低工艺节点处是不可扩展的。结合本披露执行的方法也可以代表对出厂微调过程的改善,因为微调是不准确的并且不能跟踪温度,所以出厂微调过程可能仍然需要过度设计。

上面描述的都是示例。本披露旨在涵盖落入本申请范围内、包括所附权利要求的对本文所描述的主题的更改、修改和变化。如本文所使用的,术语“包括”意指包括但不限于。术语“基于”意指至少部分地基于。另外,在本披露或权利要求列举“一个”、“第一”或“另一”元素或其等效物的情况下,应将其解释为包括一个或一个以上这样的元素,既不要求也不排除两个或更多个这样的元素。

- 一种流水线ADC的级间增益失配校正方法

- 一种零中频接收机及其正负频增益失配校正电路