一种像素结构、阵列基板、显示面板以及显示设备

文献发布时间:2023-06-19 11:19:16

技术领域

本申请涉及显示技术领域,特别涉及一种像素结构、阵列基板、显示面板以及显示设备。

背景技术

随着显示技术的发展,人们对显示器件的需求的不断提高。目前,常规的电子纸的像素为双栅TFT(Thin Film Transistor,薄膜晶体管),且在TFT的上方并无ITO(IndiumTin Oxides,透明薄膜导电层)的覆盖,这样,此处的ITO缺口较大,导致像素的开口率较低,导致显示效果不佳。

发明内容

本申请提供了一种像素结构,可以有效的提高像素的开口率,提高显示效果。

为了达到上述目的,本申请提供了一种像素结构,包括:栅线、数据线、栅极、第一电极、第二电极以及第三电极;

所述栅极与所述栅线连接,所述第一电极与所述数据线连接;

所述第二电极具有沿自身延伸方向分布的第一部分和第二部分,其中:

所述第二电极的第一部分与所述第一电极以及栅极配合形成第一薄膜晶体管;

所述第二电极的第二部分与所述第三电极以及栅极配合形成第二薄膜晶体管。

本申请中的像素结构,第二电极具有沿自身延伸方向分布的第一部分和第二部分,且第一部分与第一电极以及栅极配合形成第一薄膜晶体管,第二部分与第三电极以及栅极配合形成第二薄膜晶体管。即一个栅极上设有第一薄膜晶体管和第二薄膜晶体管,这样,相对于现有技术中的两个栅极来说,可以有效的压缩栅极所占有的金属面积,进而提高像素的开口率,以提高显示效果。

优选地,所述栅线沿列的方向设置,所述第二电极沿列方向设置,且所述第一电极和所述第三电极位于所述第二电极的同侧,且所述第一电极与所述第二电极沿行的方向排布,所述第二电极与所述第三电极沿行的方向排布。

优选地,所述栅极沿行的方向设置,所述第二电极沿行方向设置,且所述第一电极和所述第二电极沿列的方向排布,第二电极与所述第三电极沿列的方向排布。

优选地,还包括像素电极,所述第三电极与所述像素电极连接。

优选地,所述栅线具有向所述像素电极一侧的凸出部,所述凸出部及栅线的自身部分形成所述栅极。

优选地,所述第一电极与所述第二电极的间隙为6~12um。

优选地,所述第二电极的宽度为12~14um。

本发明还提供了一种阵列基板,包括多个如上所述的像素结构,多个所述像素结构呈阵列分布。其产生的有益效果与像素结构的有益相同,此处不再赘述。

本发明还提供了一种显示面板,包括多个如上所述的像素结构,多个所述像素结构呈阵列分布。由于像素结构的开口率增加,显示效果的增强,以使显示面板的显示效果。

本发明还提供了一种显示设备,包括多个如上所述的像素结构,多个所述像素结构呈阵列分布。其产生的有益效果与像素结构的有益相同,此处不再赘述。

附图说明

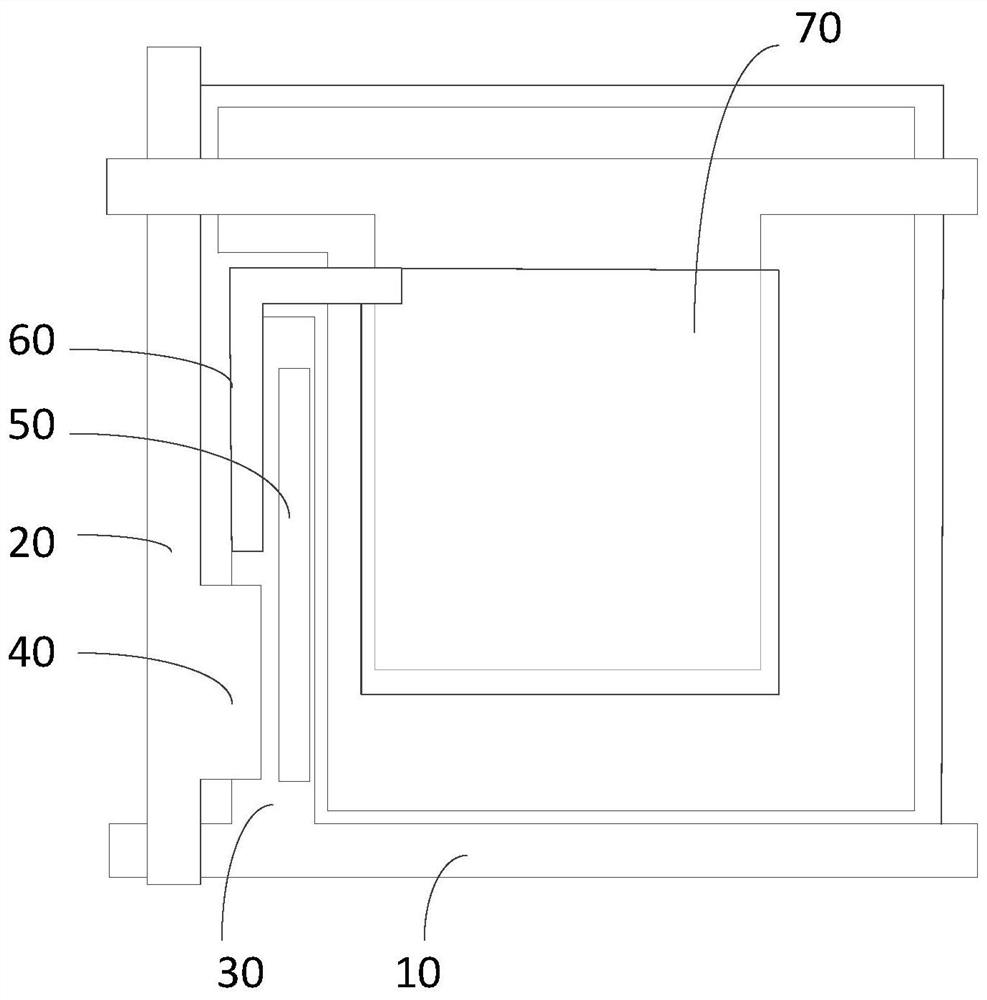

图1为本申请实施例的像素结构的一种结构示意图;

图2为本申请实施例的像素结构的又一种结构示意图。

图标:10-栅线;20-数据线;30-栅极;40-第一电极;50-第二电极;60-第三电极;70-像素电极。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

本申请实施例提供了一种背板,包括:

本申请提供了一种像素结构,包括:栅线10、数据线20、栅极30、第一电极40、第二电极50以及第三电极60;

所述栅极30与所述栅线10连接,所述第一电极40与所述数据线20连接;

所述第二电极50具有沿自身延伸方向分布的第一部分和第二部分,其中:

所述第二电极50的第一部分与所述第一电极40以及栅极30配合形成第一薄膜晶体管;

所述第二电极50的第二部分与所述第三电极60以及栅极30配合形成第二薄膜晶体管。

本申请中的像素结构,第二电极50具有沿自身延伸方向分布的第一部分和第二部分,且第一部分与第一电极40以及栅极30配合形成第一薄膜晶体管,第二部分与第三电极60以及栅极30配合形成第二薄膜晶体管。即一个栅极30上设有第一薄膜晶体管和第二薄膜晶体管,这样,相对于现有技术中的两个栅极30来说,可以有效的压缩栅极30所占有的金属面积,进而提高像素的开口率,以提高显示效果。

需要说明的是,第一电极40与第三电极60可以均为源极或漏极,第二电极50可以为漏极或源极。

在一种可能的实施例中,参照图1,所述栅线10沿列的方向设置,所述第二电极50沿列方向设置,且所述第一电极40和所述第三电极60位于所述第二电极50的同侧,且所述第一电极40与所述第二电极50沿行的方向排布,所述第二电极50与所述第三电极60沿行的方向排布。此种设置方式中,栅极30沿列的方式设置,栅极30与第一电极40、第二电极50以及第三电极60可以形成第一薄膜晶体管和第二薄膜晶体管,以保证装置自身的特性。且第一电极40和第三电极60与第二电极50相对应的部分位于第二电极50的同侧,这样,栅极30、第一电极40、第二电极50以及第三电极60的金属面积可以有效的被压缩,从而提高像素结构的开口率,提高像素结构的显示效果。具体地,当栅极30沿列的方向设置时,像素结构的开口可以由75.01%提升至78.06%。

在一种可能的实施例中,参照图2,所述栅极30沿行的方向设置,所述第二电极50沿行方向设置,且所述第一电极40和所述第二电极50沿列的方向排布,第二电极50与所述第三电极60沿列的方向排布。此种设置方式中,栅极30沿行的方式设置,栅极30与第一电极40、第二电极50以及第三电极60可以形成第一薄膜晶体管和第二薄膜晶体管,以保证装置自身的特性。且第一电极40和第三电极60与第二电极50相对应的部分位于第二电极50的同侧,这样,栅极30、第一电极40、第二电极50以及第三电极60的金属面积可以有效的被压缩,从而提高像素结构的开口率,提高像素结构的显示效果。

需要说明的是,当栅极30沿行的方向设置时,栅极30可以由栅线10向所述像素电极70一侧的形成的凸出部及栅线10的自身部分构成。这样,利用栅线10可以减小栅极30所占用的面积,且第一薄膜晶体管和第二薄膜晶体管并排设置,且第一薄膜晶体管和第二薄膜晶体管共用的第二电极在衬底的正投影与栅线10在衬底上的正投影至少部分交叠,优选的,如图2所示,第一薄膜晶体管和第二薄膜晶体管共用的第二电极在衬底层的正投影位于栅线10在衬底层上的正投影内,利用相邻的两个像素结构之间固有的空间设置了第二电极,有效减小了第一薄膜晶体管和第二薄膜晶体的面积占比;像素开口率显著提升,由75.01%提升至82.30%。

在具体实施的过程中,还包括像素电极70,所述第三电极60与所述像素电极70连接。

在一种可能的实施例中,所述第一电极40与所述第二电极50的间隙为6~12um。所述第二电极50的宽度为12~14um。具体的尺寸需要根据实际的情况进行调整,且该种设置方式可以有效的减小第一薄膜晶体管和第二薄膜晶体管所占与的空间,提高开口率。

在上述实施例中,其仍然采用常规4Mask工艺,在不改变连接关系的情况下,有效的提高了像素结构的开口率。

本发明还提供了一种阵列基板,包括多个如上所述的像素结构,多个所述像素结构呈阵列分布。其产生的有益效果与像素结构的有益相同,此处不再赘述。

本发明还提供了一种显示面板,包括多个如上所述的像素结构,多个所述像素结构呈阵列分布。由于像素结构的开口率增加,显示效果的增强,以使显示面板的显示效果。

本发明还提供了一种显示设备,包括多个如上所述的像素结构,多个所述像素结构呈阵列分布。其产生的有益效果与像素结构的有益相同,此处不再赘述。

显然,本领域的技术人员可以对本发明实施例进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

- 一种像素结构、阵列基板、显示面板以及显示设备

- 阵列基板像素结构、阵列基板、液晶面板及显示设备