正交振荡器电路系统及含正交振荡器电路系统的电路系统

文献发布时间:2023-06-19 11:11:32

技术领域

本发明涉及振荡器电路系统,特别地涉及包括第一差分振荡器电路和第二差分振荡器电路的正交振荡器电路系统,第一差分振荡器电路和第二差分振荡器电路每个均被配置成生成一对差分振荡器信号。

在这样的电路系统中,两对差分振荡器信号被控制成使得它们形成一组正交振荡器信号,即,彼此相互异相90°的信号。这样的信号可以具有分别为0°、90°、180°和270°的相对相位,其可以分别称为I+相位、Q+相位、I-相位和Q-相位。

这样的振荡器电路系统可以被配置成电压控制的,其中输入电压控制信号例如通过控制振荡器电路系统的一个或更多个LC振荡电路的谐振频率来控制振荡器信号的频率(工作频率)。以此方式配置的振荡器电路系统可以被称为压控振荡器(VCO),特别地可以称为正交VCO,在正交VCO中,两对差分振荡器信号形成一组正交振荡器信号。

本发明还涉及包括这种正交振荡器电路系统的电路系统,例如锁相环(PLL)。

背景技术

作为背景,图1是表示先前考虑的差分振荡器电路1、100、200、1E、100E和200E的电路图,上述差分振荡器电路每个均被配置成生成一对差分振荡器信号。因此,这些差分振荡器电路中的任一个均可以生成上述的两对差分振荡器信号中的一对,使得这些差分振荡器电路(及其变型)可以互换使用。本公开内容将相应地来理解。

差分振荡器电路1包括第一尾节点2、第二尾节点4以及在第一尾节点2和第二尾节点4之间并行延伸的一对并联电流路径10、20。一对输出节点12、22分别沿电流路径10、20定位(例如在中间处),在一对输出节点12、22处生成一对差分振荡器信号OUT+和OUT-(分别具有0°和180°的相对相位)。

一对交叉耦合的晶体管14、24,在这种情况下为NMOS场效应晶体管(FET)分别沿电流路径10、20设置在相应的输出节点12、22与第一尾节点2之间,使得它们的沟道形成这些电流路径的相应部分。晶体管14、24的源极端子一起连接到第一尾节点2,并且其漏极端子分别连接到输出节点12、22。晶体管14、24的栅极端子连接到彼此的漏极端子,使得它们形成交叉耦合对。

电容器16、26分别连接在输出节点12、22与电压供应节点之间,所述电压供应节点在这种情况下为接地电源(GND)。电感器18、28分别沿着电流路径10、20连接在相应的输出节点12、22和第二尾节点4之间,使得它们形成这些电流路径10、20的相应部分。电感器18、28可以一起实现为中心抽头电感器(绕组/线圈),其中心抽头(即触点)连接到第二尾节点4,并且其相应的端部连接到输出节点12、22,如图1所示。

第一尾电流路径30将第一尾节点2连接到第一电压源节点32,第一电压源节点32在这种情况下为接地电源(GND),第二尾电流路径40将第二尾节点4连接到第二电压源节点42,第二电压源节点42在这种情况下为VDD。因此,在这种情况下,第一电压源节点32可以是(或用于连接到)低电压源,第二电压源节点42可以是(或用于连接到)高电压源。电流源34沿第一尾电流路径30定位(即,形成第一尾电流路径30的一部分),以便调节或控制如图所示沿该电流路径30流动的偏置电流Ibias。因此,电流源34还调节或控制沿第二尾电流路径40流动的偏置电流Ibias,该电流在第一电流路径10和第二电流路径20之间分配。

在操作中,一对交叉耦合的晶体管14、24用作交叉耦合的反相放大器,以迫使(或偏置或推动)输出节点12、22处的电压为差分的。电容器16、26和电感器18、28形成LC振荡电路的一部分,该LC振荡电路然后使输出节点12、22处的电压以频率f

当然,本领域技术人员将认识到,电容器16、26不需要如图所示设置在输出节点12、22与接地电源GND之间。可以通过将这些电容器16、26串联放置在输出节点12、22之间来实现等效的LC振荡电路。考虑到这一点,参考差分振荡器电路100。

差分振荡器电路100与差分振荡器电路1类似,因此,相似的元件由相似的附图标记表示,并且省略重复的描述。差分振荡器电路100与差分振荡器电路1的不同之处在于,电容器16、26分别被变容器(变容二极管或可变电容二极管)116、126代替,并且这些变容器被串联连接在电流路径10、20之间,有效地在输出节点12、22之间。电容器18、28与变容器116、126的并联连接形成差分振荡器电路100的LC振荡电路。

如图所示,将控制电压Vtune施加到变容器116、126之间的节点。众所周知,通过改变控制电压Vtune,变容器116、126的电容被改变,从而改变(或调谐)谐振频率f

差分振荡器电路200也与差分振荡器电路1类似,并且相似的元件还是由相似的附图标记表示,并且省略重复的描述。差分振荡器电路200与差分振荡器电路1的不同之处在于,电容器16、26被连接在电流路径10、20之间,有效地在输出节点12、22之间的电容器316代替。此外,电感器18、28已经被电感器318代替,电感器318也连接在电流路径10、20之间,有效地在输出节点12、22之间并且与电容器316并联。另外,分别沿电流路径10、20在输出节点12、22与第二尾节点4之间设置另外的一对交叉耦合的晶体管315、325,在这种情况下为PMOS场效应晶体管(FET),使得它们的沟道形成这些电流路径的相应部分。

晶体管315、325的源极端子一起连接到第二尾节点4,并且它们的漏极端子分别连接到输出节点12、22。晶体管315、325的栅极端子连接到彼此的漏极端子,使得它们形成交叉耦合对。像晶体管14、24一样,晶体管315、325用作交叉耦合的反相放大器。实际上,晶体管14、24、315、325的组合用作一对交叉耦合的CMOS反相器。电容器316和电感器318的并联连接形成差分振荡器电路200的LC振荡电路。

因此,显然,差分振荡器电路100、200的操作对应于差分振荡器电路1的操作,并且分别在输出节点12、22处产生差分振荡器信号。电容器316和/或电感器318可以是可调谐的,以例如形成VCO。因此,可以将本文公开的任何差分振荡器电路(并且通过扩展,本文公开的任何正交振荡器电路系统)实现为VCO。本公开内容将相应地来理解。

差分振荡器电路1E等效于差分振荡器电路1,其LC振荡电路以示意形式示出为LC振荡电路50,电容器16、26有效地被认为在该LC振荡电路50内(即,好像它们如前所述而串联连接在输出节点12、22之间)。类似地,差分振荡器电路100E等效于差分振荡器电路100,其LC振荡电路以示意形式示出为LC振荡电路(TC)150,电感器18、28和变容器116、126有效地被认为在该LC振荡电路150内。差分振荡器电路200E等效于差分振荡器电路200,其LC振荡电路示意性地示出为LC振荡电路250,电容器316和电感器318有效地被认为在该振荡电路250内。用于差分振荡器电路1、100、200的附图标记同样适用于其中示出了相似的元件的电路1E、100E、200E,但是为了简洁起见,在等效电路中仅示出了这些附图标记的一部分。

因此,应当理解,本发明可以应用于多种差分振荡器电路拓扑,并且这些可以如在电路1、100、200中那样以“完整形式”来表示,或者如在电路1E、100E、200E中那样以“简化形式”来表示。为了便于说明,在下文中将重点讨论电路1和电路1E,但是应理解,如图1中所论证的,本文公开的技术适用于各个拓扑。即,在本文稍后公开差分振荡器电路并且该差分振荡器电路基于差分振荡器电路1的情况下,应当理解,等效差分振荡器电路可以基于差分振荡器电路100、200、1E、100E和200E中的任一个。而且,显然,其他类似的差分振荡器电路可以通过组合来自电路100、200、1E、100E和200E的元件,例如通过在电路200中采用电容器16和26代替电容器316来得到,因此是同样相关的。

顺便提及,尽管在图1中示出了场效应晶体管(在这种情况下为MOSFET),但是本文公开的电路也可以使用双极结型晶体管(BJT)来实现。而且,例如,可以使用PMOS晶体管代替NMOS晶体管来“颠倒”地实现所示的电路,并且类似的考虑也适用于采用BJT的电路。此外,尽管通常如前所述电流源34有用地调节偏置电流,但是在一些布置中,这些电流源34可以被认为是可选的。在一些布置中,电流源34可以被简单地省略,而在其他布置中,它们可以被电阻器代替,但是这些仅是示例。

如前所述,本发明特别地涉及生成两对差分振荡器信号的振荡器电路系统,其中这两对差分振荡器信号形成一组正交振荡器信号。图2是先前考虑的正交振荡器电路系统300的示意图。

振荡器电路系统300包括通过交叉耦合电路320耦合在一起的在此处示意性地示出的I侧差分振荡器电路310I和Q侧差分振荡器电路310Q。这些差分振荡器电路310I、310Q二者均可以实现为例如图1的差分振荡器电路中的任一个。以差分振荡器电路1为运行示例,差分振荡器电路310I的I+输出和I-输出分别对应于电路1的一个实例的OUT+输出和OUT-输出,并且差分振荡器电路310Q的Q+输出和Q-输出分别对应于电路1的另一实例的OUT+输出和OUT-输出。然后,借助于交叉耦合电路320将这些输出交叉耦合。

交叉耦合电路320包括Gm单元(跨导单元)330和340,Gm单元330和340两者均可以例如如在图2中明确示出的单元330的实现方式330-1中那样实现。单元330将与I侧差分振荡器电路310I的差分电压输出摆幅I+、I-成比例的电流注入到Q侧差分振荡器电路310Q的电流路径10、20中。类似地,单元340将与Q侧差分振荡器电路310Q的差分电压输出摆幅Q+、Q-成比例但极性相反(例如,通过反向连接输入Vin+、Vin-或输出Vout+、Vout-,对此,参见电路330-1)的电流注入到I侧差分振荡器电路310I的电流路径10、20中。由于该注入的电流,I侧差分振荡器电路310I和Q侧差分振荡器电路310Q耦合在一起并被“迫使”正交地工作。

然而,图2中的方法有缺点。添加的Gm单元330、340由有源电路系统实现(例如,参见电路330-1)。这些增加的单元需要额外的电流,其不会对实际的振荡器增益或摆幅(即I+、I-、Q+、Q-)产生贡献,反而会增加总功耗。此外,增加的Gm单元显著地增加了相位噪声并使振荡器性能劣化。

期望解决这样的问题,特别是期望提供更为高效和/或精确的正交振荡器电路系统。

发明内容

根据本发明的第一方面的实施方式,提供了一种正交振荡器电路系统,该正交振荡器电路系统包括:第一差分振荡器电路和第二差分振荡器电路,每个差分振荡器电路包括第一尾节点和第二尾节点、一对输出节点以及分别经由其输出节点在其第一尾节点与第二尾节点之间并行延伸的一对并联电流路径,并且每个差分振荡器电路被配置成在其各自的输出节点处生成一对差分振荡器信号;以及交叉耦合电路,其被连接以将差分振荡器电路交叉耦合,其中:对于差分振荡器电路中的每个差分振荡器电路,第一尾电流路径将第一尾节点连接到第一电压源节点,第二尾电流路径将第二尾节点连接到第二电压源节点,第一电压源节点和第二电压源节点中的一者用于连接到高电压源,并且第一电压源节点和第二电压源节点中的另一者用于连接到低电压源;差分振荡器电路中的每个差分振荡器电路包括共模电压节点,在该共模电压节点处产生共模电压信号,该共模电压节点是连接在该差分振荡器电路的并联电流路径之间(例如,输出节点之间)的分压器的中间节点或者是该差分振荡器电路的第二尾电流路径的节点;并且交叉耦合电路包括:针对差分振荡器电路中的至少一个差分振荡器电路或每个差分振荡器电路的电流控制装置,该电流控制装置形成该差分振荡器电路的第一尾电流路径的一部分,并且被配置成基于差分振荡器电路中的另一者的共模电压信号来控制沿该第一尾电流路径流动的电流,以使各个差分振荡器电路的共模电压信号基本上反相。

这种正交振荡器电路系统可以简单地称为振荡器电路系统或振荡器。当振荡器信号的频率由电压控制信号控制时,该电路系统可以被称为VCO。类似的考虑适用于本文公开的其他正交振荡器电路系统。

通过使各个差分振荡器电路的共模电压信号基本上反相,差分振荡器信号对被控制以形成一组正交振荡器信号。

交叉耦合电路可以包括反相放大器,该反相放大器被配置成,针对差分振荡器电路中的至少一个差分振荡器电路或每个差分振荡器电路,基于差分振荡器电路中的另一个差分振荡器电路的共模电压信号来控制该差分振荡器电路的电流控制装置。以这种方式,可以实现期望的反相关系。

交叉耦合电路可以包括第一晶体管和第二晶体管,分别作为针对第一差分振荡器电路和第二差分振荡器电路的电流控制装置。第一晶体管和第二晶体管可以分别形成第一差分振荡器电路和第二差分振荡器电路的第一尾电流路径的相应部分,使得沿相应的第一尾电流路径流动的电流分别流过第一晶体管和第二晶体管。第一晶体管和第二晶体管的栅极或基极端子可以分别连接到第二差分振荡器电路和第一差分振荡器电路的共模节点,使得它们分别由在第二差分振荡器电路和第一差分振荡器电路的共模节点处产生的共模电压信号来控制。以这种方式,晶体管可以被交叉耦合并且用作一对交叉耦合的反相放大器。

差分振荡器电路中的每个差分振荡器电路可以包括电流源,该电流源形成其第二尾电流路径的一部分并且被配置成调节沿该电流路径流动的偏置电流。第一差分振荡器电路和第二差分振荡器电路的共模电压节点可以是其第二尾节点或者是其第二尾节点与其电流源之间的其第二尾电流路径的节点。

第一晶体管和第二晶体管的栅极或基极端子可以经由阻抗分别连接到第二差分振荡器电路和第一差分振荡器电路的共模节点。这些阻抗可以是电容器或者可以包括电容器。

第一差分振荡器电路和第二差分振荡器电路的共模电压节点可以是其各自的分压器的中间节点。在那种情况下,对于差分振荡器电路中的每个差分振荡器电路,其分压器可以包括:连接在其并联电流路径中的一者(例如,在输出节点中的一者处)与其中间节点之间的分压器阻抗;以及连接在其并联电流路径中的另一者(例如,在其输出节点中的另一者处)与其中间节点之间的另一分压器阻抗。分压器阻抗可以是电容器或者可以包括电容器。

差分振荡器电路中的每个差分振荡器电路可以包括电流源,该电流源形成其第二尾电流路径的一部分以调节沿该电流路径流动的偏置电流。

第一晶体管和第二晶体管的栅极或基极端子可以经由相应的阻抗(例如电阻,用于DC偏置)连接到其漏极或集电极端子或者连接到电压源节点。

根据本发明的第二方面的实施方式,提供了一种正交振荡器电路系统,该正交振荡器电路系统包括:第一差分振荡器电路和第二差分振荡器电路,每个差分振荡器电路包括第一尾节点和第二尾节点、一对输出节点以及分别经由其输出节点在其第一尾节点与第二尾节点之间并行延伸的一对并联电流路径,并且每个差分振荡器电路被配置成在其各自的输出节点处生成一对差分振荡器信号;以及包括第一晶体管和第二晶体管的交叉耦合电路,其被连接以将差分振荡器电路交叉耦合,其中:对于差分振荡器电路中的每个差分振荡器电路,第一尾电流路径将第一尾节点连接到第一电压源节点,第二尾电流路径将第二尾节点连接到第二电压源节点,第一电压源节点和第二电压源节点中的一者用于连接到高电压源,并且第一电压源节点和第二电压源节点中的另一者用于连接到低电压源;第一晶体管和第二晶体管被连接以分别形成差分振荡器电路的第一尾电流路径的相应部分,使得沿相应的第一尾电流路径流动的电流流过相应的晶体管;第一晶体管和第二晶体管的栅极或基极端子分别连接到第二差分振荡器电路和第一差分振荡器电路的第一尾节点,使得它们分别由在第二差分振荡器电路和第一差分振荡器电路的第一尾节点处产生的电压信号来控制;第一尾电流路径从第一尾节点分别经由第一晶体管和第二晶体管延伸到共享尾节点;共享尾电流路径将共享尾节点连接到共享电压源节点,该共享电压源节点是差分振荡器电路二者的第一电压源节点;所述差分振荡器电路中的每个差分振荡器电路包括被配置成具有目标谐振频率的LC振荡电路;并且正交振荡器电路系统包括由差分振荡器电路共享的辅助LC振荡电路,辅助LC振荡电路被配置成具有基本上是目标谐振频率的两倍的谐振频率。

包括第一晶体管和第二晶体管的交叉耦合电路可以用作交叉耦合的反相放大器。特别地,每个晶体管均可以用作电流控制装置,该电流控制装置形成其差分振荡器电路的第一尾电流路径的一部分,并且被配置成基于差分振荡器电路中的另一者的第一尾节点电压信号来控制沿该第一尾电流路径流动的电流,以使各个差分振荡器电路的第一尾节点电压信号基本上反相。通过使各个差分振荡器电路的第一尾节点电压信号基本上反相,差分振荡器信号对被控制以形成一组正交振荡器信号。

差分振荡器电路的LC振荡电路定义目标谐振频率,并且由差分振荡器电路共享的辅助LC振荡电路被配置成具有基本上是目标谐振频率的两倍的谐振频率,使得交叉耦合电路的增益集中在目标谐振频率的两倍处。以此方式,也可以避免/衰减交叉耦合电路的DC增益和不需要的寄生频率处的增益。

第一晶体管和第二晶体管可以被连接为一对交叉耦合的晶体管。辅助LC振荡电路可以连接在差分振荡器电路的第一尾节点或第一尾电流路径之间。辅助LC振荡电路可以与该对交叉耦合的晶体管并联连接。

共享电流源或阻抗可以形成共享尾电流路径的一部分。这样的共享电流源可以被配置成调节沿该电流路径流动的偏置电流。

正交振荡器电路系统可以包括辅助共享尾节点。对于差分振荡器电路中的每个差分振荡器电路,辅助尾电流路径可以形成辅助LC振荡电路的一部分,并且经由辅助阻抗(其为辅助LC振荡电路的一部分)将第一尾节点连接到辅助共享尾节点。辅助共享尾电流路径可以将辅助共享尾节点连接到辅助共享电压源节点。辅助共享电流源可以形成辅助共享尾电流路径的一部分,并且被配置成调节沿该电流路径流动的偏置电流。辅助阻抗可以是电感器或者包括电感器。辅助阻抗可以一起实现为中心抽头电感器,中心抽头电感器的中心抽头是辅助共享尾节点。

电容器可以与辅助共享电流源或辅助共享尾电流路径并联连接,以例如滤除噪声。

辅助LC振荡电路可以包括将第一尾节点分别连接到电压源节点的一对第一节点电容器。该对第一节点电容器可以一起被实现为单个电容器。该对第一节点电容器可以被实现为相关节点处的寄生电容。

根据本发明的第三方面的实施方式,提供了一种正交振荡器电路系统,该正交振荡器电路系统包括:第一差分振荡器电路,其具有差分输出节点并且被配置成分别在这些输出节点处生成第一对差分振荡器信号;第二差分振荡器电路,其具有差分输出节点并且被配置成分别在这些输出节点处生成第二对差分振荡器信号;以及包括第一晶体管和第二晶体管的交叉耦合电路,其被连接以将第一差分振荡器电路和第二差分振荡器电路交叉耦合。第一晶体管和第二晶体管可以作为一对交叉耦合的晶体管来连接。

根据本发明的第四方面的实施方式,提供了一种正交振荡器电路系统,该正交振荡器电路系统包括:第一差分振荡器电路和第二差分振荡器电路,每个差分振荡器电路包括第一尾节点和第二尾节点、一对输出节点以及分别经由其输出节点在其第一尾节点与第二尾节点之间并行延伸的一对并联电流路径,并且每个差分振荡器电路被配置成在其各自的输出节点处生成一对差分振荡器信号;以及交叉耦合电路,其被连接以将差分振荡器电路交叉耦合,其中:对于差分振荡器电路中的每个差分振荡器电路,第一尾电流路径将第一尾节点连接到第一电压源节点,第二尾电流路径将第二尾节点连接到第二电压源节点,第一电压源节点和第二电压源节点中的一者用于连接到高电压源,并且第一电压源节点和第二电压源节点中的另一者用于连接到低电压源;差分振荡器电路中的每个差分振荡器电路均包括共模电压节点,在该共模电压节点处产生共模电压信号,该共模电压节点是连接在该差分振荡器电路的输出节点之间的分压器的中间节点,或者是该差分振荡器电路的第二尾电流路径的节点;并且交叉耦合电路连接到差分振荡器电路的共模节点并且被配置成控制差分振荡器电路中的一者或二者的操作以使各个差分振荡器电路的共模电压信号基本上反相。

在前述方面中的任何方面中,第一差分振荡器电路和第二差分振荡器电路的差分振荡器信号对可以形成一组正交振荡器信号。

在前述方面中的任何方面中,正交振荡器电路系统可以是IQ振荡器电路系统。在这种情况下,第一差分振荡器电路可以是I侧差分振荡器电路,第一差分振荡器电路的一对差分振荡器信号可以分别是I+差分振荡器信号和I-差分振荡器信号,第二差分振荡器电路可以是Q侧差分振荡器电路,并且第二差分振荡器电路的一对差分振荡器信号可以分别是Q+差分振荡器信号和Q-差分振荡器信号。

根据本发明的第五方面的实施方式,提供了一种锁相环电路系统,该锁相环电路系统包括根据前述方面中的任一方面的正交振荡器电路系统。

根据本发明的第六方面的实施方式,提供了一种集成电路系统,例如IC芯片,该集成电路系统包括根据前述第一方面至第四方面中的任一方面的正交振荡器电路系统或者根据前述第五方面的锁相环电路系统。

根据本发明的第七方面的实施方式,提供了包括根据前述第一方面至第四方面中的任一方面的正交振荡器电路系统或者根据前述第五方面的锁相环电路系统的模数转换器(ADC)、数模转换器(DAC)、串行器/解串器电路(SERDES)、时钟数据恢复电路(CDR)、无线收发器、处理器或时钟电路系统。

根据本发明的第八方面的实施方式,提供了一种正交振荡器电路系统,该正交振荡器电路系统包括:第一差分振荡器电路,其具有差分输出节点并且被配置成分别在这些输出节点处生成第一对差分振荡器信号;第二差分振荡器电路,其具有差分输出节点并且被配置成分别在这些输出节点处生成第二对差分振荡器信号;以及交叉耦合电路,其被连接以将第一差分振荡器电路和第二差分振荡器电路交叉耦合。交叉耦合电路可以包括一对交叉耦合的晶体管。

附图说明

现在将通过示例的方式来参考附图,在附图中:

图1如上所述是表示先前考虑的差分振荡器电路的电路图;

图2如上所述是先前考虑的正交振荡器电路系统的示意图;

图3呈现了两个曲线图,其以示例的方式示出了差分振荡器电路的电压波形;

图4是先前考虑的正交振荡器电路系统的示意性电路图;

图5是先前考虑的正交振荡器电路系统的示意性电路图;

图6是体现本发明的正交振荡器电路系统的示意性电路图;

图7呈现了两个曲线图,其示出了与图3类似的差分振荡器电路的电压波形;

图8是体现本发明的正交振荡器电路系统的示意性电路图;

图9是体现本发明的正交振荡器电路系统的示意性电路图;

图10是体现本发明的正交振荡器电路系统的示意性电路图;

图11是体现本发明的PLL电路系统的示意性电路图;以及

图12是体现本发明的集成电路系统的示意性电路图。

具体实施方式

在考虑本发明的实施方式之前,将考虑多个先前考虑的电路布置和相关分析。

图3呈现了两个曲线图,其以示例的方式示出了差分振荡器电路的电压波形。

上方的曲线图示出了差分振荡器电路1(作为图1的差分振荡器电路的示例差分振荡器电路)的电压波形,以及对该波形所应用于的电路的节点的指示。因此,波形OUT+、OUT-分别是在输出节点12和22处得到的电压波形。波形Vtail是在第一尾节点2处得到的电压波形。假定将差分振荡器电路1的LC振荡电路调谐为具有谐振频率f

下方的曲线图示出了与上方的曲线图相同的电压波形,但是针对差分振荡器电路1的两个实例,其可以称为差分振荡器电路1(I)即I侧振荡器电路和差分振荡器电路1(Q)即Q侧振荡器电路。还假定差分振荡器电路1(I)和1(Q)正交地工作,因此它们的输出差分振荡器信号可以称为:I+和I-,对应于电路1(I)的OUT+和OUT-;以及Q+和Q-,对应于电路1(Q)的OUT+和OUT-,其中I+、I-、Q+和Q-是一组正交信号。

因此,波形I+和I-分别是在电路1(I)的输出节点12和22处得到的电压波形,波形Q+和Q-分别是在电路1(Q)的输出节点12和22处得到的电压波形。在电路1(I)的第一尾节点2处得到波形Vtail I,在电路1(Q)的第一尾节点2处得到波形Vtail Q。再次,假定电路1(I)和1(Q)的LC振荡电路(LC振荡器)被调谐为具有谐振频率f

图4是示出如上所讨论的差分振荡器电路1(I)和1(Q)的示意图。如前所述,相似的元件由相似的附图标记表示,因此基于以上对图1的差分振荡器电路1的描述,将理解差分振荡器电路1(I)和1(Q)。差分振荡器电路1(I)和1(Q)特别地借助于反相放大器402一起构成正交振荡器电路系统400,该反相放大器402示意性地示出为将两个电路1(I)和1(Q)的第一尾节点2耦合在一起,以迫使这些尾节点2处的波形是差分的。尽管根据图4,反相放大器402耦合可以呈现单向耦合,但是耦合可以被视为双向的,使得反相放大器402耦合是反相放大器交叉耦合。

图5是先前考虑的正交振荡器电路系统500的示意图,该正交振荡器电路系统500是正交振荡器电路系统400的示例实现方式。这里,为了简单起见,电路1(I)和1(Q)分别被表示为根据图1的电路1E的等效电路1E(I)和1E(Q)。再次,相似的元件用相似的附图标记表示,并且省略重复的描述。

如图5所示,通过提供分别沿电路1E(I)和1E(Q)的第一尾电流路径30的变压器线圈502和504以及相应的并联电容器506和508来实现反相放大器402耦合。如前所述,振荡电路(TC)50以谐振频率f

然而,在集成电路系统中,例如在IC芯片上以相同的初级匝数和次级匝数来实现这样的变压器是复杂的并且需要大面积。

图6是正交振荡器电路系统600的示意图,该正交振荡器电路系统600如图5中那样也是使用电路1E(I)和1E(Q)的正交振荡器电路系统400的实现方式,但是具有反相放大器402耦合的改进的实现方式。再次,相似的元件用相似的附图标记表示,并且省略重复的描述。正交振荡器电路系统600体现了本发明。

如图6所示,通过提供沿相应的第一尾电流路径30的交叉耦合的晶体管602和604——在这种情况下为NMOS FET——来实现反相放大器402耦合,所述电流路径30被配置成在共享尾节点606处相交。共享尾电流路径608(由这两个电流路径30共享)将共享尾节点606连接到作为第一电压源节点32——在此情况下为接地电源(GND)——的共享电压源节点。沿共享尾电流路径608提供共享电流源610,以调节或控制沿该路径流动的偏置电流Ibias(以及因此来调节或控制沿两个电流路径30流动的电流的组合)。因此,不需要单独的电流源34。共享电流源610可以用诸如电阻器的阻抗代替。

晶体管602、604的源极端子连接到共享尾节点606,并且其漏极端子连接到相应的第一尾节点2,使得它们的沟道形成相应的第一尾电流路径30的相应部分。晶体管602和604的栅极端子连接到彼此的漏极端子。交叉耦合的晶体管602和604用作交叉耦合的反相放大器,迫使在各个第一尾端节点2处的波形是差分的。

还提供了辅助LC振荡电路620,该辅助LC振荡电路620用于将一对交叉耦合的晶体管602、604的增益集中在期望频率2f

LC振荡电路620包括辅助电容器622,辅助电容器622将相应的第一尾节点2连接到电压源节点32,在这种情况下连接到接地电源(GND)。此外,辅助电感器628和630沿相应的辅助尾电流路径将相应的第一尾节点2连接到辅助共享尾节点632。辅助共享尾电流路径634将辅助共享尾节点632连接到辅助共享电压源节点,在这种情况下,该辅助共享电压源节点是第一电压源节点32,即接地电源(GND)。沿辅助共享尾电流路径634提供辅助共享电流源636,以调节或控制沿该路径流动的偏置电流Ibias。电容器638与电流源636并联连接(例如,在节点632和GND之间),以滤除来自电流源636的噪声。

电感器628、630可以一起实现为中心抽头电感器(绕组/线圈),其中心抽头(即触点)连接到节点632,并且其相应的端部连接到第一尾节点2,如图6所示。这样的中心抽头电感器可以被称为差分电感器。使用去耦电容器638将中心抽头AC接地。

辅助共享电流源636可以被诸如电阻器的阻抗代替。

如前所述,随着辅助LC振荡电路620以2f

与变压器(参见图5)相比,差分电感器更容易实现并且具有更紧凑的面积和更高的Q因子。此外,在添加的一对差分晶体管602、604中使用的电流也流过第一尾节点2(即,流过两个差分振荡器电路的核心),从而有助于正交输出信号I+、I-、Q+、Q-的增益和摆幅。应当理解,这同样适用于本文稍后公开的实施方式。

发明人还考虑了实现正交振荡器电路系统的其他方式。在这方面,参考图7和图8。

首先从图8开始,示出了体现本发明的正交振荡器电路系统700的示意图,除了去除了反相放大器402以外,该正交振荡器电路系统700与图4的正交振荡器电路系统400相同。替代地,在图8的电路1(I)和1(Q)中的每个电路中,一对阻抗702串联连接在两个并联电流路径10、20之间(有效地在输出节点12、22之间),以便在它们之间定义共模节点704,在共模节点704处生成共模电压信号。阻抗702可以例如是电容器或包括电容器。反相放大器706连接在共模节点704之间。如前所述,在图4和图8之中,相似的元件用相似的附图标记表示,从而省略重复的描述。

图7呈现了与图3相同的两个曲线图,不同之处在于在相关的第一尾节点2处得到的Vtail波形已被在相关的共模节点704处得到的Vcm波形(共模波形)代替。

因此,在表示单个差分振荡器电路1的上方曲线图中,共模电压波形Vcm等效于在图8的电路1(I)中的节点704处得到的波形。再次假定电路1(和1(I))的LC振荡电路被调谐为具有谐振频率f

在对应于图8中的一对差分振荡器电路1(I)和1(Q)的下方曲线图中,分别在差分振荡器电路1(I)和1(Q)的节点704处得到共模电压波形Vcm-I和Vcm-Q。再次,假定电路1(I)和1(Q)的LC振荡电路被调谐为具有谐振频率f

因此,得出结论,如果迫使(或促使)电路1(I)和1(Q)的共模节点704处的波形是差分的,则可以实现正交操作,即,其中,I+、I-、Q+、Q-形成一组正交信号。在图8中的电路1(I)和1(Q)的共模节点704之间的反相放大器706的连接用于产生该操作。尽管根据图8,反相放大器802耦合可以呈现单向耦合,但是耦合可以被视为双向的,使得反相放大器802耦合是反相放大器交叉耦合。

当然,应当理解,可以以类似的方式为例如图1中所示的其他差分振荡器电路对提供这样的共模节点704,并且在这些节点处的波形由反相放大器布置如由图8中的反相放大器706来控制,以实现本发明的其他实施方式。本公开内容将相应地来理解。

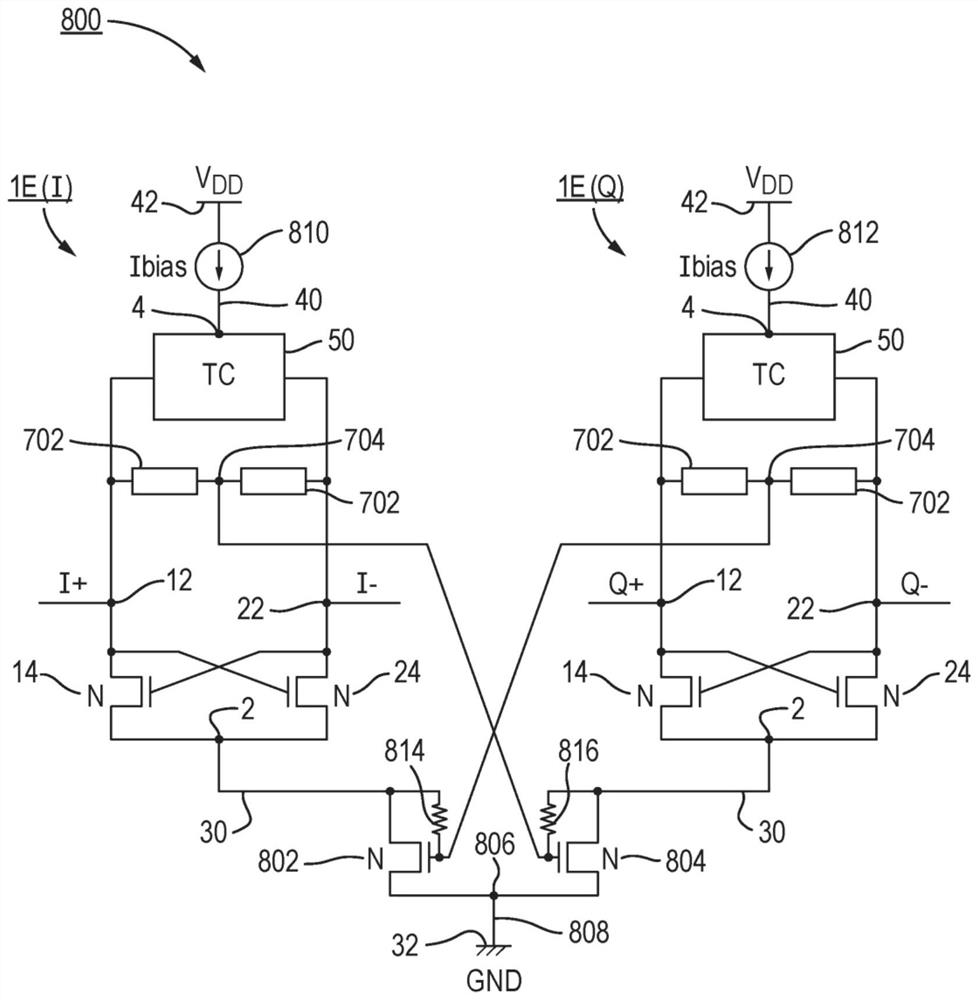

图9是体现本发明的正交振荡器电路系统800的示意图,正交振荡器电路系统800是正交振荡器电路系统700的实现方式,电路1(I)和1(Q)分别被表示为根据图1的电路1E的等效电路1E(I)和1E(Q)。再次,相似的元件用相似的附图标记表示,并且省略重复的描述。

如图9所示,通过沿相应的第一尾电流路径30提供交叉耦合的晶体管802和804——在这种情况下为NMOS FET——来实现反相放大器耦合706,所述电流路径30被配置成在共享尾节点806处相交。共享尾电流路径808(由两个电流路径30共享)将共享尾节点806连接到作为第一电压源节点32——在这种情况下为接地电源(GND)——的共享电压源节点。

如图所示,沿第二电流路径40提供电流源810、812,以调节或控制沿这些路径流动的相应偏置电流Ibias。因此,不需要电流源34。电流源810、812每个均可以被诸如电阻器的阻抗代替,但是当然在这种情况下,偏置电流不会被调节。

晶体管802、804的源极端子连接到共享尾节点806,并且其漏极端子连接到相应的第一尾节点2,使得它们的沟道形成相应的第一尾电流路径30的相应部分。晶体管802和804的栅极端子连接到彼此的差分振荡器电路的共模节点704。即,晶体管802的栅极端子连接到电路1E(Q)的共模节点704,并且晶体管804的栅极端子连接到电路1E(I)的共模节点704。从这个意义上,晶体管802和804被交叉耦合。回想到,阻抗702可以是电容器。考虑到这一点,晶体管802、804的栅极端子通过相应的电阻器814、816耦合到其漏极端子,以将其栅极电压DC偏置(自偏置)。因此,在DC处,晶体管802、804被二极管连接。当然,出于类似的原因,晶体管802和804的栅极端子替代地可以为耦合到电压源节点的电阻器。

在2f

同样,在添加的一对差分晶体管802、804中使用的电流也流过第一尾节点2(即,流过两个差分振荡器电路的核心),从而有助于正交输出信号I+、I-、Q+、Q-的增益和摆幅。即,该对差分晶体管802、804重复使用流过两个差分振荡器电路的电流,并且不需要额外的电流。此外,与图6实施方式相比,图9实施方式在所需电路面积方面更小。

图10是体现本发明的正交振荡器电路系统900的示意图,正交振荡器电路系统900是正交振荡器电路系统700的另一种实现方式,其中电路1(I)和1(Q)分别被表示为根据图1的电路1E的等效电路1E(I)和1E(Q)。

图10的实施方式与图9的实施方式类似,因此,相似的元件用相似的附图标记表示,并且省略重复的描述。

正交振荡器电路系统900和正交振荡器电路系统800之间的区别在于阻抗702(以及因此节点704)已被去除。晶体管802和804的栅极端子经由相应的电容器902、904连接到彼此的差分振荡器电路的第二尾节点4(其用作共模节点),而不是连接到节点704。即,晶体管802的栅极端子经由电容器904连接到电路1E(Q)的第二尾节点4,并且晶体管804的栅极端子经由电容器902连接到电路1E(I)的第二尾节点4。在这个意义上,晶体管802和804在图10中被交叉耦合。

在给定电容器902、904的情况下,晶体管802、804的栅极端子通过相应的电阻器814、816耦合至其漏极端子,以将其栅极电压DC偏置(自偏置),并且类似的考虑如图9中那样也适用。当然,出于类似的原因,晶体管802和804的栅极端子可以为耦合到电压源节点的电阻器。

同样,在2f

同样,在添加的一对差分晶体管802、804中使用的电流也流过第一尾节点2(即,流过两个差分振荡器电路的核心),从而有助于正交输出信号I+、I-、Q+、Q-的增益和摆幅。即,该对差分晶体管802、804重复使用流过两个差分振荡器电路的电流,并且不需要额外的电流。此外,图10实施方式与图6实施方式相比在所需电路面积方面更小。

应当理解,可以以类似的方式将在这样的共模节点704和4处的波形用于例如图1所示的其他差分振荡器电路对,并且如在图9和图10中那样利用反相放大器布置来控制,以实现本发明的其他实施方式。本公开内容将相应地来理解。

图11是体现本发明的锁相环(PLL)电路系统1000的示意图。

PLL电路系统包括如图11所示连接在一起的相位检测器1002、(低通)滤波器1004、VCO 1006和分频器1008。VCO可以使用本文公开的任何正交振荡器电路系统实施方式来实现,记住,如图1所示的电路的范围所例示的,这些正交振荡器电路系统实施方式的差分振荡器电路可以以许多不同的方式实现。

本领域技术人员将理解诸如图11所示的PLL电路系统的基本操作。然而,作为简要概述,VCO 1006生成输出信号O/P,相位检测器1002比较该输出信号O/P(由分频器1008分频)的相位与输入(周期性)参考信号REF的相位。相位检测器1002的输出取决于检测到的相位差并且在被输入到VCO 1006之前通过滤波器1004进行滤波以控制输出信号O/P的频率。在当前情况下,根据以上考虑的正交振荡器电路系统实施方式,输出信号O/P可以被视为正交输出信号,然而,相位检测器1002可以(经由分频器1008)被提供有构成正交输出信号的四个振荡器信号中的仅一个。

当然,图11仅描绘了一种可能的PLL拓扑,并且本发明扩展到使用本文公开的任何正交振荡器电路系统实施方式来实现其VCO的任何PLL拓扑。

本文公开的任何电路系统可以被实现为集成电路系统,例如作为IC芯片诸如倒装芯片(或作为其一部分)。图12是体现本发明的集成电路系统2000和3000的示意图。

集成电路系统2000和3000可以代表IC芯片中的一些或全部。集成电路系统2000包括根据本发明的正交振荡器电路系统,例如正交振荡器电路系统600、700、800或900。集成电路系统3000包括根据本发明的PLL电路系统,例如包括VCO 1006的PLL电路系统1000。VCO1006可以实现为正交振荡器电路系统600、700、800或900,尽管如先前所说明的,例如其振荡电路的L或C元件适于利用电压控制来控制。

本发明扩展到如上所述的集成电路系统和IC芯片,包括这种IC芯片的电路板,以及包括这种电路板的通信网络(例如,互联网光纤网络和无线网络)以及这种网络的网络设备。应当理解,PLL电路系统(其具有正交输出)可以用于需要时钟的各种应用中。本发明扩展到这样的应用,并且示例包括但不限于模数转换器(ADC)、数模转换器(DAC)、串行器/解串器电路(SERDES)、时钟数据恢复电路(CDR)、无线收发器、处理器和相关的时钟电路系统等。

在所附权利要求的精神和范围内,可以根据以上公开内容以许多不同的方式来体现本发明。

- 正交振荡器电路系统及含正交振荡器电路系统的电路系统

- 应力补偿振荡器电路系统和使用该电路系统的集成电路