LED芯片、驱动基板以及显示面板

文献发布时间:2023-06-19 11:42:32

技术领域

本申请涉及显示技术领域,具体涉及一种LED芯片、驱动基板以及显示面板。

背景技术

迷你型发光二极管(MiniLightEmitting Diode,MiniLED)/微型发光二极管(MicroLightEmitting Diode,MicroLED)显示作为一种新兴的显示技术,相较于传统的液晶显示,对比度更高、亮度更高且色域更广,且对比于目前的有机发光二极管显示,Mini-LED/Micro-LED在亮度、寿命以及功耗上均有更优异的表现。

主动式MiniLED/MicroLED驱动背板是通过电压驱动LED芯片发光。在目前的LED芯片设计架构中,受到传输电压信号的信号走线自身电阻的影响,驱动背板上会产生电阻压降(IR-Drop),进而导致靠近驱动芯片的LED芯片的发光亮度与远离驱动芯片的LED芯片的发光亮度存在差异,导致驱动背板的整体亮度不均一。

发明内容

本申请实施例提供一种LED芯片、驱动基板以及显示面板,以解决现在技术中存在的驱动背板整体亮度不均一的技术问题。

本申请实施例提供一种LED芯片,所述LED芯片具有一正极性输入端和一负极性输入端,所述LED芯片包括依次串联的第一芯片部、第二芯片部以及第三芯片部,所述正极性输入端位于所述第一芯片部上,所述负极性输入端位于所述第三芯片部上。

可选的,在本申请的一些实施例中,所述第一芯片部、所述第二芯片部和所述第三芯片部的承载电压均介于2V至4V之间。

可选的,在本申请的一些实施例中,所述LED芯片包括一衬底层,所述第一芯片部、所述第二芯片部以及所述第三芯片部间隔设置于所述衬底层上,所述第一芯片部和所述第二芯片部通过一第一连接走线导通,所述第二芯片部和所述第三芯片部通过一第二连接走线导通。

可选的,在本申请的一些实施例中,所述第一芯片部在所述衬底层上的正投影面积、所述第二芯片部在所述衬底层上的正投影面积以及所述第三芯片部在所述衬底层上的正投影面积相等。

可选的,在本申请的一些实施例中,所述LED芯片还包括:

外延层,所述外延层设置于所述衬底层上,所述外延层包括间隔设置的第一外延部、第二外延部以及第三外延部;以及

电极层,所述电极层设置于所述外延层远离所述衬底层的一侧,所述电极层包括第一输入电极、第一输出电极、第二输入电极、第二输出电极、第三输入电极以及第三输出电极,所述第一输入电极和第一输出电极设置于所述第一外延部上,所述第二输入电极和所述第二输出电极设置于所述第二外延部上,所述第三输入电极和所述第三输出电极设置于所述第三外延部上;

其中,所述第一外延部、所述第一输入电极和所述第一输出电极构成所述第一芯片部,所述第二外延部、所述第二输入电极和所述第二输出电极构成所述第二芯片部,所述第三外延部、所述第三输入电极和所述第三输出电极构成所述第三芯片部;

所述正极性输入端位于所述第一输入电极上,所述第一输出电极通过所述第一连接走线与所述第二输入电极电连接,所述第二输出电极通过所述第二连接走线与所述第三输入电极电连接,所述负极性输入端位于所述第三输出电极上。

可选的,在本申请的一些实施例中,所述第二芯片部位于所述第一芯片部和所述第三芯片部之间;

所述第一外延部和所述第二外延部之间具有第一沟槽,所述第一连接走线覆盖所述第一沟槽,所述第一连接走线的一端电连接于所述第一输出电极,所述第一连接走线的另一端电连接于所述第二输入电极;

所述第二外延部和所述第三外延部之间具有第二沟槽,所述第二连接走线覆盖所述第二沟槽,所述第二连接走线的一端电连接于所述第二输出电极,所述第二连接走线的另一端电连接于所述第三输入电极。

可选的,在本申请的一些实施例中,所述第一芯片部和所述第二芯片部并列设置于所述第三芯片部的同侧;

所述第一外延部和所述第二外延部之间具有第一沟槽,所述第一连接走线覆盖所述第一沟槽,所述第一连接走线的一端电连接于所述第一输出电极,所述第一连接走线的另一端电连接于所述第二输入电极;

所述第三外延部与所述第一外延部和所述第二外延部之间具有第二沟槽,所述第二沟槽连通于所述第一沟槽,所述第二连接走线覆盖所述第二沟槽位于所述第二外延部和所述第三外延部之间的部分,所述第二连接走线的一端电连接于所述第二输出电极,所述第二连接走线的另一端电连接于所述第三输入电极。

可选的,在本申请的一些实施例中,所述LED芯片还包括第四芯片部,所述第四芯片部串联在所述第二芯片部和所述第三芯片部之间。

可选的,在本申请的一些实施例中,所述LED芯片包括一衬底层,所述第一芯片部、所述第二芯片部、所述第三芯片部以及所述第四芯片部间隔设置于所述衬底层上,所述第一芯片部和所述第二芯片部通过一第一连接走线导通,所述第二芯片部和所述第四芯片部通过一第二连接走线导通,所述第四芯片部和所述第三芯片部通过一第三连接走线导通。

可选的,在本申请的一些实施例中,所述第一芯片部、所述第二芯片部、所述第四芯片部以及所述第三芯片部并列设置于所述衬底层上。

可选的,在本申请的一些实施例中,所述第一芯片部、所述第二芯片部、所述第四芯片部以及所述第三芯片部呈阵列排布。

本申请实施例提供一种驱动基板,其具有多个背光分区,所述驱动基板包括:

基底;以及

若干LED芯片组,设置于所述基底上,每一所述LED芯片组对应于一所述背光分区,所述LED芯片组包括串联设置的两个子LED芯片组,每一所述子LED芯片组包括两个并联设置的发光单元,每一所述发光单元包括一LED芯片;

其中,所述LED芯片具有一正极性输入端和一负极性输入端,所述LED芯片包括依次串联的第一芯片部、第二芯片部以及第三芯片部,所述正极性输入端位于所述第一芯片部上,所述负极性输入端位于所述第三芯片部上。

本申请实施例还提供一种显示面板,其包括背光模组,所述背光模组包括前述实施例所述的驱动基板。

本申请提供一种LED芯片、驱动基板以及显示面板,所述LED芯片具有一正极性输入端和一负极性输入端,LED芯片包括依次串联的第一芯片部、第二芯片部以及第三芯片部,正极性输入端位于第一芯片部上,负极性输入端位于第三芯片部上。本申请通过将LED芯片设置为依次串联的第一芯片部、第二芯片部以及第三芯片部,基于串联电路分压的原理,提高了LED芯片的承载电压,进而相较于独立的LED芯片结构,能够获得一种可承载高压的LED芯片,从而当所述LED芯片应用于驱动基板时,能够提高驱动基板整体亮度的均一性。

附图说明

为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

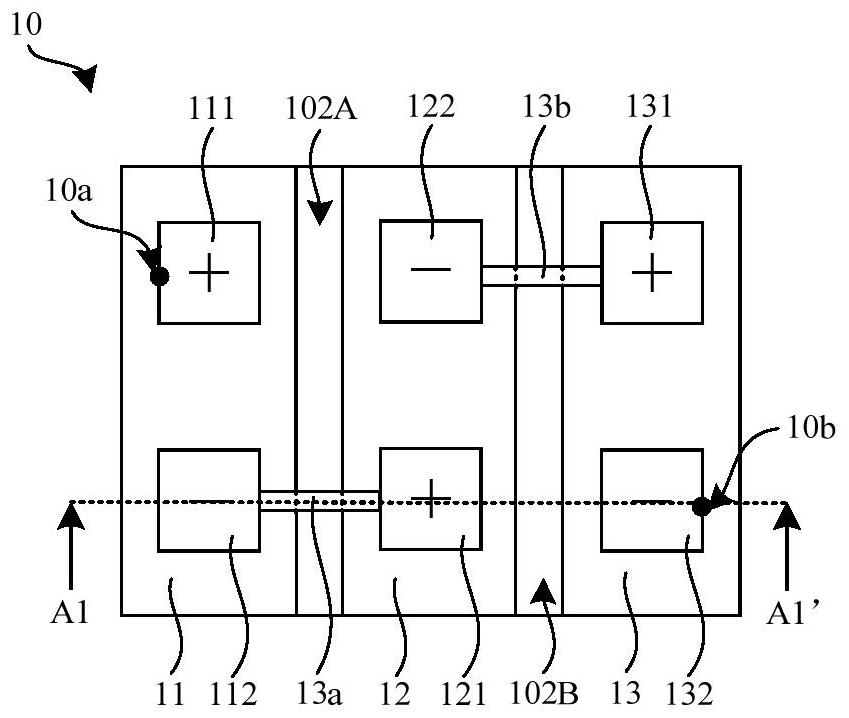

图1是本申请提供的LED芯片的第一种实施例的俯视示意图。

图2是图1所示的LED芯片沿A1-A1’线的剖面示意图。

图3是图1所示的LED芯片中的第一芯片部、第二芯片部以及第三芯片部在衬底层上的正投影的结构示意图。

图4是本申请提供的LED芯片的第二种实施例的俯视示意图。

图5是图4所示的LED芯片中的第一芯片部、第二芯片部以及第三芯片部在衬底层上的正投影的结构示意图。

图6是本申请提供的LED芯片的第三种实施例的俯视示意图。

图7是本申请提供的LED芯片的第四种实施例的俯视示意图。

图8是图7所示的LED芯片沿A2-A2’线的剖面示意图。

图9是图7所示的LED芯片中的第一芯片部、第二芯片部、第三芯片部以及第四芯片部在衬底层上的正投影的结构示意图。

图10是本申请提供的LED芯片的第五种实施例的俯视示意图。

图11是现有技术的驱动基板的俯视示意图。

图12是现有技术的驱动基板的发光单元的结构示意图。

图13是图12所示的发光单元沿B-B’线的剖面示意图。

图14是图12所述的发光单元的电压-电流特性曲线示意图。

图15是本申请提供的驱动基板的俯视示意图。

图16是本申请提供的驱动基板的发光单元的俯视示意图。

图17是图16所示的发光单元的电压-电流特性曲线示意图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。此外,应当理解的是,此处所描述的具体实施方式仅用于说明和解释本申请,并不用于限制本申请。在本申请中,在未作相反说明的情况下,使用的方位词如“上”和“下”通常是指装置实际使用或工作状态下的上和下,具体为附图中的图面方向;而“内”和“外”则是针对装置的轮廓而言的。

本申请实施例提供一种LED芯片、驱动基板以及显示面板,以下分别进行详细说明。需说明的是,以下实施例的描述顺序不作为对实施例优选顺序的限定。

需要说明的是,本申请中的LED芯片可以为MiniLED芯片,也可以为MicroLED,本申请以下各实施例仅以LED芯片为MiniLED芯片为例进行说明,但并不限于此。

请参照图1和图2,本申请第一种实施例提供一种LED芯片10。LED芯片10具有一正极性输入端10a和一负极性输入端10b。LED芯片10包括依次串联的第一芯片部11、第二芯片部12以及第三芯片部13。正极性输入端10a位于第一芯片部11上。负极性输入端10b位于第三芯片部13上。

由此,本实施例通过将LED芯片10设置为依次串联的第一芯片部11、第二芯片部12以及第三芯片部13,基于串联电路分压的原理,提高了LED芯片10的承载电压,进而相较于独立的LED芯片结构,获得了一种可承载高压的LED芯片10,从而当LED芯片10应用于驱动基板时,能够提高驱动基板整体亮度的均一性。

其中,由于LED芯片10的正极性输入端10a和负极性输入端10b位于LED芯片10的相对两侧,因此,当LED芯片10连接外部走线时,可以简化走线结构,为LED芯片10的使用提供了便利。

其中,第一芯片部11、第二芯片部12和第三芯片部13的承载电压均介于2V至4V之间。比如,所述承载电压可以为2V、2.5V、3V、3.5V或4V,等等。

在本实施例中,第一芯片部11、第二芯片部12和第三芯片部13的承载电压均为3V。此时,LED芯片10的承载电压为9V。

具体的,LED芯片10包括衬底层101、外延层102以及电极层103。外延层102设置于衬底层101上。电极层103设置于外延层102远离衬底层101的一侧。

其中,衬底层101的材料可以为氮化镓。

外延层102包括依次设置的P型氮化镓层1021、量子阱层1022以及N型氮化镓层1023。需要说明的是,本实施例中的P型氮化镓层1021与N型氮化镓层1023的位置可以互换,本申请对P型氮化镓层1021与N型氮化镓层1023的相对位置不作具体限定。另外,外延层102的具体膜层结构也可以根据实际应用需求进行设定,在此不再赘述。

在本实施例中,外延层102包括间隔设置的第一外延部102a、第二外延部102b以及第三外延部102c。

电极层103包括第一输入电极111、第一输出电极112、第二输入电极121、第二输出电极122、第三输入电极131以及第三输出电极132。第一输入电极111和第一输出电极112设置于第一外延部102a上。第二输入电极121和第二输出电极122设置于第二外延部102b上。第三输入电极131和第三输出电极132设置于第三外延部102c上。

其中,电极层103的材料可以为金属、合金或其他具体导电作用的材料,本申请对电极层103的材料不作具体限定。

需要说明的是,在本实施例中,第一输入电极111、第一输出电极112、第二输入电极121、第二输出电极122、第三输入电极131以及第三输出电极132的图案仅为示意,用以方便描述本实施例,但不能理解为对本申请的限制。

在本实施例中,第一外延部102a、第一输入电极111和第一输出电极112构成第一芯片部11。第二外延部102b、第二输入电极121和第二输出电极122构成第二芯片部12。第三外延部102c、第三输入电极131和第三输出电极132构成第三芯片部13。

其中,第一输入电极111为第一芯片部11的正极。LED芯片10的正极性输入端10a位于第一输入电极111上。第一输出电极112为第一芯片部11的负极。第二输入电极121为第二芯片部12的正极。第二输出电极122为第二芯片部12的负极。第三输入电极131为第三芯片部13的正极。第三输出电极132为第三芯片部13的负极。LED芯片10的负极性输入端10b位于第三输出电极132上。

需要说明的是,本申请中所述的“正极”均为各芯片部的正极性输入端,所述的“负极”均为各芯片部的负极性输入端。

在本实施例中,第一芯片部11、第二芯片部12以及第三芯片部13间隔设置于衬底层101上。第一芯片部11和第二芯片部12通过一第一连接走线13a导通。第二芯片部12和第三芯片部13通过一第二连接走线13b导通。

具体的,第一芯片部11中的第一输出电极112通过第一连接走线13a与第二芯片部12中的第二输入电极121电连接。第二芯片部12中的第二输出电极122通过第二连接走线13b与第三芯片部13中的第三输入电极131电连接。

在本实施例中,第一芯片部11、第二芯片部12以及第三芯片部13并列设置。第一外延部102a和第二外延部102b之间具有第一沟槽102A。第一连接走线13a覆盖第一沟槽102A。第一连接走线13a的一端电连接于第一输出电极112。第一连接走线13a的另一端电连接于第二输入电极121。第二外延部102b和第三外延部102c之间具有第二沟槽102B。第二连接走线13b覆盖第二沟槽102B。第二连接走线13b的一端电连接于第二输出电极122。第二连接走线13b的另一端电连接于第三输入电极131。

在本实施例中,第一沟槽102A和第二沟槽102B均为条状。第一沟槽102A和第二沟槽102B在垂直于衬底层101所在平面的截面封闭形状均为梯形。

在一些实施例中,第一沟槽102A和第二沟槽102B的形状也可以根据实际情况进行设定,本申请对此不作限定,只要保证第一连接走线13a和第二连接走线13b分别搭接在第一沟槽102A和第二沟槽102B的内表面,均在本申请的保护范围内。

请参照图3,在本实施例中,第一芯片部11、第二芯片部12以及第三芯片部13的尺寸相同。具体的,第一芯片部11在衬底层101上的正投影面积S1、第二芯片部12在衬底层101上的正投影面积S2以及第三芯片部13在衬底层101上的正投影面积S3相等。

上述设置能够避免因各芯片部的尺寸不同而导致LED芯片10整体散热不均,从而能够提高LED芯片10的散热性能以及信赖性。

在本实施例中,第一芯片部11、第二芯片部12以及第三芯片部13在衬底层101上的正投影的图案的形状均为方形,由此可以简化工艺,降低第一沟槽102A和第二沟槽102B的刻蚀难度,从而有利于节约工艺成本。

本实施例的LED芯片的制备方法如下:

B101:提供一生长基底;

其中,所述生长基底可以为蓝宝石基底、三氧化二铝基底或硅基底。

B102:在所述生长基底上生长一衬底层,所述衬底层具有多个芯片区,每一所述芯片区具有第一子芯片区、第二子芯片区和第三子芯片区;

B103:在所述衬底层上依次生长P型氮化镓层、量子阱层以及N型氮化镓层,以在所述衬底层上形成外延层;

B104:对所述外延层进行刻蚀,以在每一所述芯片区形成间隔设置的第一沟槽和第二沟槽;

其中,所述第一沟槽和所述第二沟槽贯穿所述外延层,且裸露出所述衬底层。所述第一沟槽和所述第二沟槽将所述外延层划分成间隔设置的第一外延部、第二外延部以及第三外延部。所述第一外延部、所述第二外延部和所述第三外延部分别位于所述第一子芯片区、第二子芯片区以及第三子芯片区。

B105:在所述外延层上形成电极层,所述电极层覆盖所述第一沟槽和所述第二沟槽的内表面;

B106:对所述电极层进行刻蚀,以在所述第一外延部上形成图案化的第一输入电极和第一输出电极,在所述第二外延部上形成图案化的第二输入电极和第二输出电极,在所述第三外延部上形成图案化的第三输入电极和第三输出电极,在所述第一沟槽的内表面形成电连接所述第一输出电极和所述第二输入电极的第一连接走线,在所述第二沟槽的内表面形成电连接所述第二输出电极和所述第三输入电极的第二连接走线;

B107:将上述得到的结构进行切割,每一所述芯片区对应形成一LED芯片。

其中,在所述LED芯片中,在所述第一子芯片区,第一外延部、第一输入电极以及第一输出电极构成第一芯片部。在所述第二子芯片区,第二外延部、第二输入电极以及第二输出电极构成第二芯片部。在所述第三子芯片区,第三外延部、第三输入电极以及第三输出电极构成第三芯片部。所述第一芯片部、所述第二芯片部以及第三芯片部共用所述衬底层。

需要说明的是,本申请的LED芯片的制备方法中的刻蚀、切割等工艺均为现有技术,在此不再赘述。

请参照图4和图5,本申请第二种实施例提供的LED芯片10与第一种实施例的区别之处在于:第一芯片部11和第三芯片部13在衬底层101上的正投影的图案的形状均为三角形,第二芯片部12在衬底层101上的正投影的图案的形状为六边形。

请参照图6,本申请第三种实施例提供的LED芯片10与第一种实施例的区别之处在于:第一芯片部11和第二芯片部12并列设置于第三芯片部13的同侧。第一外延部102a和第二外延部102b之间具有第一沟槽102A。第一连接走线13a覆盖第一沟槽102A。第三外延部102c与第一外延部102a和第二外延部102b之间具有第二沟槽102B。第二沟槽102B连通于第一沟槽102A。第二连接走线13b覆盖第二沟槽102B位于第二外延部12和第三外延部13之间的部分。

其中,LED芯片10的正极性输入端10a和负极性输入端10b位于LED芯片10的同侧。

请参照图7和图8,本申请第四种实施例提供的LED芯片10与第一种实施例的不同之处在于:LED芯片10还包括第四芯片部14。第四芯片部14串联在第二芯片部12和第三芯片部13之间。第一芯片部11、第二芯片部12、第四芯片部14以及第三芯片部13并列设置于衬底层101上。

本实施例通过将LED芯片10设置为依次串联的第一芯片部11、第二芯片部12、第四芯片部14以及第三芯片部13,基于串联电路分压的原理,进一步提高了LED芯片10的承载电压,从而当LED芯片10应用至驱动基板中时,能够进一步提高驱动基板整体亮度的均一性。

其中,第四芯片部14的承载电压可以介于2V至4V之间,如可以为2V、2.5V、3V、3.5V或4V。在本实施例中,第四芯片部14的承载电压为3V。此时,LED芯片10的承载电压为12V。

在本实施例中,外延层102还包括第四外延部102d。第四外延部102d设置于第二外延部102b和第三外延部102c之间。

电极层103包括第四输入电极141和第四输出电极142。第四输入电极141和第四输出电极142设置于第四外延部102d上。

其中,第四外延部102d、第四输入电极141以及第四输出电极142构成第四芯片部14。第四输入电极141为第四芯片部14的正极。第四输出电极142为第四芯片部14的负极。

在本实施例中,第二芯片部12和第四芯片部14通过一第二连接走线13b导通。第四芯片部14和第三芯片部13通过一第三连接走线13c导通。

具体的,第二芯片部12中的第二输出电极122通过第二连接走线13b与第四芯片部14中的第四输入电极141电连接。第四芯片部14中的第四输出电极142通过第三连接走线13c与第三芯片部13中的第三输入电极131电连接。

第二外延部102b和第四外延部102d之间具有第二沟槽102B。第二连接走线13b覆盖第二沟槽102B。第二连接走线13b的一端电连接于第二输出电极122。第二连接走线13b的另一端电连接于第四输入电极141。第四外延部102d和第三外延部102c之间具有第三沟槽102C。第三连接走线13c覆盖第三沟槽102C。第三连接走线13c的一端电连接于第四输出电极142。第三连接走线13c的另一端电连接于第三输入电极131。

其中,第二沟槽102B和第三沟槽102C均为条状。第二沟槽102B和第三沟槽102C在垂直于衬底层101所在平面的截面封闭形状均为梯形。

请参照图9,在本实施例中,第四芯片部14在衬底层101上的正投影面积S4等于第一芯片部11在衬底层101上的正投影面积S1/第二芯片部12在衬底层101上的正投影面积S2/第三芯片部13在衬底层101上的正投影面积S3。上述设置能够避免因各芯片部的尺寸不同而导致LED芯片10整体散热不均,从而能够提高LED芯片10的散热性能以及信赖性。

需要说明的是,在一些实施例中,LED芯片还可以包括五个及以上的芯片部,各芯片部的承载电压均相等,均为3V。比如,当LED芯片包括五个芯片部时,LED芯片的承载电压可达15V,当LED芯片包括六个芯片部时,LED芯片的承载电压可达18V,等等。LED芯片中芯片部的数量可以根据实际情况进行设定,本申请对此不作限定。

请参照图10,本申请第五种实施例提供的LED芯片10与第四种实施例的区别之处在于:第一芯片部11、第二芯片部12、第四芯片部14以及第三芯片部13呈阵列排布。第一外延部102a和第三外延部102c之间具有第四沟槽102D。第一沟槽102A、第二沟槽102B、第三沟槽102C和第四沟槽102D彼此连通形成十字状沟槽结构。

其中,LED芯片10的正极性输入端10a和负极性输入端10b位于LED芯片10的同侧。

请参照图11,在现有技术的驱动基板100’中,驱动基板100’包括玻璃基板100a’、驱动芯片20’以及若干LED芯片组30’。驱动芯片20’设置于玻璃基板100a’的端部。若干LED芯片组30’阵列设置于玻璃基板100a’的发光侧。同一列的LED芯片组30’的正极性输入端均由VDD’走线连接至驱动芯片20’。同一列的LED芯片组30’的负极性输入端均由VSS’走线连接至驱动芯片20’。

其中,VDD’走线接入高电平电压。VSS’走线接地。

驱动基板100’具有多个背光分区100A’。每一LED芯片组30’对应于一背光分区100A’。LED芯片组30’包括串联设置的两个子LED芯片组301’。每一子LED芯片组301’包括两个并联设置的发光单元3011’。每一发光单元3011’包括串联设置的两个LED芯片10’。

需要说明的是,发光单元3011’是指能够独立封装的LED芯片的集合,在现有技术中,发光单元3011’还包括封装两个LED芯片10’的封装结构,在此不再赘述。

请参照图12和图13,LED芯片10’具有正极性输入端10a’和负极性输入端10b’。LED芯片10’包括衬底层101’、外延层102’以及电极层103’。外延层102’设置于衬底层101’上。电极层103’设置于外延层102’远离衬底层101’的一侧。

外延层102’包括依次设置的P型氮化镓层1021’、量子阱层1022’以及N型氮化镓层1023’。电极层103’包括输入电极131’和输出电极132’。输入电极131’为正极。输出电极132’为负极。

由于LED芯片10’受电压驱动而发光,LED芯片10’对电压的微弱变化较为敏感,较小的电压变化通常会引起LED芯片10’较大的亮度变化。因此,LED芯片10’对驱动基板100’上的IR drop要求较高。IR drop的产生通常是由于VDD’走线和VSS’走线电阻的分压作用,在驱动基板100’中,自靠近驱动芯片20’的方向至远离驱动芯片20’的方向,LED芯片组30’的亮度逐渐降低,使得驱动基板100’上靠近驱动芯片20’侧的亮度与其对侧的亮度存在明显差异,驱动基板100’整体表现为亮度的不均一。

在现有技术中,LED芯片10’的承载电压通常为3V。每一发光单元3011’的承载电压为6V。对于上述具有3V承载电压的LED芯片10’,其流通的最大电流可达2mA,此时,流通至每一发光单元3011’的电流为4mA,流通至每一子LED芯片组301’的电流为8mA,流通至每一LED芯片组30’的电流为8mA。因此,发光单元3011’的承载电压决定了对应的LED芯片组30’的流通电流,因而决定了每一LED芯片组30’对应的背光分区100A’的发光亮度。

图14为发光单元3011’(两个串联的LED芯片10’)的电压(U)-电流(I)特性曲线示意图,对于承载电压为6V、流通电流为4mA的发光单元3011’而言,如图14所示,I随着U的波动而发生明显的变化,比如,当U变化0.1V时,I的变化值约为2mA,由此导致LED芯片组30’的电流变化随电压的波动较大。也即,自靠近驱动芯片20’的方向至远离靠近驱动芯片20’的方向,由于VDD’走线电阻而产生的电压的降低,会使得靠近驱动芯片20’的LED芯片组30’的流通电流大于远离LED芯片组30’的流通电流,靠近驱动芯片20’的LED芯片组30’的发光亮度大于远离LED芯片组30’的发光亮度,使得驱动基板100’整体的亮度表现为不均衡。

由于IR drop与驱动背板中的流通电流及电阻变化值均成正比,其中,电阻变化值与LED芯片设计架构正相关。因此,当驱动基板的LED芯片设计架构不变时,也即,电阻变化值不变时,可通过减小对应于背光分区的LED芯片组的流通电流的大小来降低IR drop,以改善驱动基板的亮度不均一问题。

针对现有技术中存在的上述技术问题,本申请提供一种驱动基板100。请参照图15,本申请实施例提供的驱动基板100包括基底100a、驱动芯片20以及若干LED芯片组30。驱动芯片20设置于基底100a的端部。若干LED芯片组30阵列设置于基底100a的发光侧。同一列的LED芯片组30的正极性输入端均由VDD走线连接至驱动芯片20。同一列的LED芯片组30的负极性输入端均由VSS走线连接至驱动芯片20。

其中,基底100a可以为玻璃基板。VDD走线接入高电平电压。VSS走线接地。

驱动基板100具有多个背光分区100A。每一LED芯片组30对应于一背光分区100A。LED芯片组30包括串联设置的两个子LED芯片组301。每一子LED芯片组301包括两个并联设置的发光单元3011。每一发光单元3011包括一LED芯片10。

需要说明的是,发光单元3011是指能够独立封装的LED芯片10,在本实施例中,发光单元3011还包括封装LED芯片10的封装结构。所述封装结构的具体结构可以参照现有技术,在此不再赘述。

另外,本实施例仅以LED芯片10包括四个芯片部为例进行说明,但并不限于此。

请参照图16,LED芯片10具有一正极性输入端10a和一负极性输入端10b。LED芯片10包括第一芯片部11、第二芯片部12、第三芯片部13以及第四芯片部14。第一芯片部11、第二芯片部12、第四芯片部14以及第三芯片部13依次串联。正极性输入端10a位于第一芯片部11上。负极性输入端10b位于第三芯片部13上。

在本实施例中,由第一芯片部11、第二芯片部12、第三芯片部13以及第四芯片部14的承载电压均为3V,其构成的LED芯片10的承载电压为12V,LED芯片10上流通的最大电流为2mA,此时,流通至每一发光单元3011的电流为2mA,流通至每一子LED芯片组301的电流为4mA,流通至每一LED芯片组30的电流为4mA。因此,相较于现有技术中的8mA,本实施例中每一LED芯片组30的流通电流可降低一倍,从而大大降低了IR drop。

图17为发光单元3011(LED芯片10)的电压-电流特性曲线示意图,对于承载电压为12V、流通电流为2mA的发光单元3011而言,如图17所示,I随着U的波动几乎不发生改变,比如,当U变化0.1V时,I的变化值几乎可以忽略不计,使得LED芯片组30的电流随电压的波动较小。因此,在电压信号于VDD走线和VSS走线中传输时,即使电压发生改变,由于LED芯片组30整体的电流变化值较小,导致靠近驱动芯片20的LED芯片组30的流通电流与远离LED芯片组30的流通电流的差异较小,靠近驱动芯片20的LED芯片组30的发光亮度与远离LED芯片组30的发光亮度的差异较小,从而提高了驱动基板100整体亮度的均一性。

在本实施例中,由于每一发光单元3011包括一个LED芯片10,因此,相较于现有技术中的每一发光单元包括两个LED芯片而言,本实施例节省了空间,节省了LED芯片10的使用数量,从而有利于节约工艺成本。

在一些实施例中,为了进一步提高驱动背板100的整体亮度,通过增大LED芯片10尺寸的方式,可以满足实际应用需求,在此不再赘述。

需要说明的是,LED芯片10的具体结构可以参照前述实施例的描述,在此不再赘述。

本申请实施例还提供一种显示面板,其包括背光模组,所述背光模组包括前述实施例所述的驱动基板100,其中,驱动基板100的具体结构可以参照前述实施例的描述,在此不再赘述。

本实施例通过使用包括驱动基板100的背光模组,提高了驱动基板100亮度的均一性,有利于提高显示面板的显示品味,进而提升显示产品的市场竞争力。

本申请实施例还提供一种提高LED芯片承载电压的方法,其包括以下步骤:

B201:提供多个LED芯片;

B202:将每一所述LED芯片划分成间隔设置的至少三个芯片部,每一所述芯片部的承载电压为3V。

其中,所述芯片部的数量可以为三个、四个或五个,等等。

本实施例通过将一LED芯片划分成至少三个芯片部,相较于独立的LED芯片结构,能够将LED芯片的承载电压提升至少3倍,进而提供了一种可承载9V以上高压的LED芯片。

相较于现有技术中的LED芯片,本申请提供的LED芯片通过将LED芯片设置为依次串联的第一芯片部、第二芯片部以及第三芯片部,基于串联电路分压的原理,提高了LED芯片的承载电压,进而相较于独立的LED芯片结构,能够获得一种可承载高压的LED芯片,从而当所述LED芯片应用于驱动基板时,能够提高驱动基板整体亮度的均一性。

以上对本申请实施例所提供的一种LED芯片、驱动基板以及显示面板进行了详细介绍,本文中应用了具体个例对本申请的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本申请的方法及其核心思想;同时,对于本领域的技术人员,依据本申请的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本申请的限制。

- LED芯片、驱动基板以及显示面板

- OLED显示面板的驱动方法、驱动芯片及显示装置